#include <instructions.hh>

Public Member Functions | |

| Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2 (InFmt_FLAT *) | |

| ~Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2 () | |

| int | getNumOperands () override |

| int | numDstRegOperands () override |

| int | numSrcRegOperands () override |

| int | getOperandSize (int opIdx) override |

| void | execute (GPUDynInstPtr) override |

| void | initiateAcc (GPUDynInstPtr) override |

| void | completeAcc (GPUDynInstPtr) override |

Public Member Functions inherited from gem5::Gcn3ISA::Inst_FLAT Public Member Functions inherited from gem5::Gcn3ISA::Inst_FLAT | |

| Inst_FLAT (InFmt_FLAT *, const std::string &opcode) | |

| ~Inst_FLAT () | |

| int | instSize () const override |

| void | generateDisassembly () override |

| void | initOperandInfo () override |

Public Member Functions inherited from gem5::Gcn3ISA::GCN3GPUStaticInst Public Member Functions inherited from gem5::Gcn3ISA::GCN3GPUStaticInst | |

| GCN3GPUStaticInst (const std::string &opcode) | |

| ~GCN3GPUStaticInst () | |

| bool | isFlatScratchRegister (int opIdx) override |

| bool | isExecMaskRegister (int opIdx) override |

| int | coalescerTokenCount () const override |

| Return the number of tokens needed by the coalescer. More... | |

| ScalarRegU32 | srcLiteral () const override |

Public Member Functions inherited from gem5::GPUStaticInst Public Member Functions inherited from gem5::GPUStaticInst | |

| GPUStaticInst (const std::string &opcode) | |

| virtual | ~GPUStaticInst () |

| void | instAddr (int inst_addr) |

| int | instAddr () const |

| int | nextInstAddr () const |

| void | instNum (int num) |

| int | instNum () |

| void | ipdInstNum (int num) |

| int | ipdInstNum () const |

| void | initDynOperandInfo (Wavefront *wf, ComputeUnit *cu) |

| const std::string & | disassemble () |

| int | numSrcVecOperands () |

| int | numDstVecOperands () |

| int | numSrcVecDWords () |

| int | numDstVecDWords () |

| int | numSrcScalarOperands () |

| int | numDstScalarOperands () |

| int | numSrcScalarDWords () |

| int | numDstScalarDWords () |

| int | maxOperandSize () |

| bool | isALU () const |

| bool | isBranch () const |

| bool | isCondBranch () const |

| bool | isNop () const |

| bool | isReturn () const |

| bool | isEndOfKernel () const |

| bool | isKernelLaunch () const |

| bool | isSDWAInst () const |

| bool | isDPPInst () const |

| bool | isUnconditionalJump () const |

| bool | isSpecialOp () const |

| bool | isWaitcnt () const |

| bool | isSleep () const |

| bool | isBarrier () const |

| bool | isMemSync () const |

| bool | isMemRef () const |

| bool | isFlat () const |

| bool | isFlatGlobal () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isAtomicNoRet () const |

| bool | isAtomicRet () const |

| bool | isScalar () const |

| bool | readsSCC () const |

| bool | writesSCC () const |

| bool | readsVCC () const |

| bool | writesVCC () const |

| bool | readsEXEC () const |

| bool | writesEXEC () const |

| bool | readsMode () const |

| bool | writesMode () const |

| bool | ignoreExec () const |

| bool | isAtomicAnd () const |

| bool | isAtomicOr () const |

| bool | isAtomicXor () const |

| bool | isAtomicCAS () const |

| bool | isAtomicExch () const |

| bool | isAtomicAdd () const |

| bool | isAtomicSub () const |

| bool | isAtomicInc () const |

| bool | isAtomicDec () const |

| bool | isAtomicMax () const |

| bool | isAtomicMin () const |

| bool | isArgLoad () const |

| bool | isGlobalMem () const |

| bool | isLocalMem () const |

| bool | isArgSeg () const |

| bool | isGlobalSeg () const |

| bool | isGroupSeg () const |

| bool | isKernArgSeg () const |

| bool | isPrivateSeg () const |

| bool | isReadOnlySeg () const |

| bool | isSpillSeg () const |

| bool | isGloballyCoherent () const |

| Coherence domain of a memory instruction. More... | |

| bool | isSystemCoherent () const |

| bool | isF16 () const |

| bool | isF32 () const |

| bool | isF64 () const |

| bool | isFMA () const |

| bool | isMAC () const |

| bool | isMAD () const |

| virtual uint32_t | getTargetPc () |

| void | setFlag (Flags flag) |

| const std::string & | opcode () const |

| const std::vector< OperandInfo > & | srcOperands () const |

| const std::vector< OperandInfo > & | dstOperands () const |

| const std::vector< OperandInfo > & | srcVecRegOperands () const |

| const std::vector< OperandInfo > & | dstVecRegOperands () const |

| const std::vector< OperandInfo > & | srcScalarRegOperands () const |

| const std::vector< OperandInfo > & | dstScalarRegOperands () const |

Additional Inherited Members | |

Public Types inherited from gem5::GPUStaticInst Public Types inherited from gem5::GPUStaticInst | |

| enum | OpType { SRC_VEC , SRC_SCALAR , DST_VEC , DST_SCALAR } |

| typedef int(RegisterManager::* | MapRegFn) (Wavefront *, int) |

Public Attributes inherited from gem5::GPUStaticInst Public Attributes inherited from gem5::GPUStaticInst | |

| enums::StorageClassType | executed_as |

Static Public Attributes inherited from gem5::GPUStaticInst Static Public Attributes inherited from gem5::GPUStaticInst | |

| static uint64_t | dynamic_id_count |

Protected Member Functions inherited from gem5::Gcn3ISA::Inst_FLAT Protected Member Functions inherited from gem5::Gcn3ISA::Inst_FLAT | |

| template<typename T > | |

| void | initMemRead (GPUDynInstPtr gpuDynInst) |

| template<int N> | |

| void | initMemRead (GPUDynInstPtr gpuDynInst) |

| template<typename T > | |

| void | initMemWrite (GPUDynInstPtr gpuDynInst) |

| template<int N> | |

| void | initMemWrite (GPUDynInstPtr gpuDynInst) |

| template<typename T > | |

| void | initAtomicAccess (GPUDynInstPtr gpuDynInst) |

| void | calcAddr (GPUDynInstPtr gpuDynInst, ConstVecOperandU64 &addr) |

Protected Member Functions inherited from gem5::Gcn3ISA::GCN3GPUStaticInst Protected Member Functions inherited from gem5::Gcn3ISA::GCN3GPUStaticInst | |

| void | panicUnimplemented () const |

Protected Attributes inherited from gem5::Gcn3ISA::Inst_FLAT Protected Attributes inherited from gem5::Gcn3ISA::Inst_FLAT | |

| InFmt_FLAT | instData |

| InFmt_FLAT_1 | extData |

Protected Attributes inherited from gem5::Gcn3ISA::GCN3GPUStaticInst Protected Attributes inherited from gem5::Gcn3ISA::GCN3GPUStaticInst | |

| ScalarRegU32 | _srcLiteral |

| if the instruction has a src literal - an immediate value that is part of the instruction stream - we store that here More... | |

Protected Attributes inherited from gem5::GPUStaticInst Protected Attributes inherited from gem5::GPUStaticInst | |

| const std::string | _opcode |

| std::string | disassembly |

| int | _instNum |

| int | _instAddr |

| std::vector< OperandInfo > | srcOps |

| std::vector< OperandInfo > | dstOps |

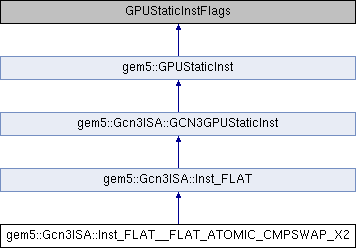

Detailed Description

Definition at line 42303 of file instructions.hh.

Constructor & Destructor Documentation

◆ Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2()

| gem5::Gcn3ISA::Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2::Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2 | ( | InFmt_FLAT * | iFmt | ) |

Definition at line 41033 of file instructions.cc.

References gem5::Gcn3ISA::InFmt_FLAT::GLC, gem5::Gcn3ISA::Inst_FLAT::instData, and gem5::GPUStaticInst::setFlag().

◆ ~Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2()

| gem5::Gcn3ISA::Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2::~Inst_FLAT__FLAT_ATOMIC_CMPSWAP_X2 | ( | ) |

Definition at line 41046 of file instructions.cc.

Member Function Documentation

◆ completeAcc()

|

overridevirtual |

Reimplemented from gem5::GPUStaticInst.

Definition at line 41120 of file instructions.cc.

References gem5::Gcn3ISA::Inst_FLAT::extData, gem5::GPUStaticInst::isAtomicRet(), gem5::Gcn3ISA::NumVecElemPerVecReg(), gem5::Gcn3ISA::InFmt_FLAT_1::VDST, and gem5::Gcn3ISA::VecOperand< DataType, Const, NumDwords >::write().

◆ execute()

|

overridevirtual |

TODO: If you encounter this panic, just remove this panic and restart the simulation. It should just work fine but this is to warn user that this path is never tested although all the necessary logic is implemented

Implements gem5::GPUStaticInst.

Definition at line 41056 of file instructions.cc.

References gem5::Gcn3ISA::InFmt_FLAT_1::ADDR, gem5::X86ISA::addr, gem5::Gcn3ISA::Inst_FLAT::calcAddr(), gem5::Gcn3ISA::InFmt_FLAT_1::DATA, data, gem5::Wavefront::decLGKMInstsIssued(), gem5::Wavefront::decVMemInstsIssued(), gem5::Wavefront::execUnitId, gem5::Gcn3ISA::Inst_FLAT::extData, fatal, gem5::Gcn3ISA::NumVecElemPerVecReg(), panic_if, gem5::Wavefront::rdGmReqsInPipe, gem5::Wavefront::rdLmReqsInPipe, gem5::Gcn3ISA::VecOperand< DataType, Const, NumDwords >::read(), gem5::Wavefront::wrGmReqsInPipe, and gem5::Wavefront::wrLmReqsInPipe.

◆ getNumOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 42310 of file instructions.hh.

References numDstRegOperands(), and numSrcRegOperands().

◆ getOperandSize()

|

inlineoverridevirtual |

Reimplemented from gem5::Gcn3ISA::GCN3GPUStaticInst.

Definition at line 42319 of file instructions.hh.

References fatal.

◆ initiateAcc()

|

overridevirtual |

Reimplemented from gem5::GPUStaticInst.

Definition at line 41114 of file instructions.cc.

◆ numDstRegOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 42315 of file instructions.hh.

Referenced by getNumOperands().

◆ numSrcRegOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 42316 of file instructions.hh.

Referenced by getNumOperands().

The documentation for this class was generated from the following files:

- arch/amdgpu/gcn3/insts/instructions.hh

- arch/amdgpu/gcn3/insts/instructions.cc