#include <remote_gdb.hh>

Public Member Functions | |

| char * | data () const |

| Return the pointer to the raw bytes buffer containing the register values. More... | |

| size_t | size () const |

| Return the size of the raw buffer, in bytes (i.e., half of the number of digits in the g/G packet). More... | |

| void | getRegs (ThreadContext *) |

| Fill the raw buffer from the registers in the ThreadContext. More... | |

| void | setRegs (ThreadContext *) const |

| Set the ThreadContext's registers from the values in the raw buffer. More... | |

| const std::string | name () const |

| Return the name to use in places like DPRINTF. More... | |

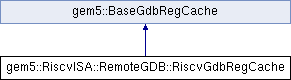

Public Member Functions inherited from gem5::BaseGdbRegCache Public Member Functions inherited from gem5::BaseGdbRegCache | |

| BaseGdbRegCache (BaseRemoteGDB *g) | |

| virtual | ~BaseGdbRegCache () |

Private Member Functions | |

| BaseGdbRegCache (BaseRemoteGDB *g) | |

Private Attributes | |

| struct { | |

| uint64_t gpr [int_reg::NumArchRegs] | |

| uint64_t pc | |

| uint64_t fpu [float_reg::NumRegs] | |

| uint32_t fflags | |

| uint32_t frm | |

| uint32_t fcsr | |

| uint32_t placeholder | |

| uint64_t cycle | |

| uint64_t time | |

| uint64_t ustatus | |

| uint64_t uie | |

| uint64_t utvec | |

| uint64_t uscratch | |

| uint64_t uepc | |

| uint64_t ucause | |

| uint64_t utval | |

| uint64_t uip | |

| uint64_t sstatus | |

| uint64_t sedeleg | |

| uint64_t sideleg | |

| uint64_t sie | |

| uint64_t stvec | |

| uint64_t scounteren | |

| uint64_t sscratch | |

| uint64_t sepc | |

| uint64_t scause | |

| uint64_t stval | |

| uint64_t sip | |

| uint64_t satp | |

| uint64_t mvendorid | |

| uint64_t marchid | |

| uint64_t mimpid | |

| uint64_t mhartid | |

| uint64_t mstatus | |

| uint64_t misa | |

| uint64_t medeleg | |

| uint64_t mideleg | |

| uint64_t mie | |

| uint64_t mtvec | |

| uint64_t mcounteren | |

| uint64_t mscratch | |

| uint64_t mepc | |

| uint64_t mcause | |

| uint64_t mtval | |

| uint64_t mip | |

| uint64_t hstatus | |

| uint64_t hedeleg | |

| uint64_t hideleg | |

| uint64_t hie | |

| uint64_t htvec | |

| uint64_t hscratch | |

| uint64_t hepc | |

| uint64_t hcause | |

| uint64_t hbadaddr | |

| uint64_t hip | |

| } | r |

| RISC-V Register Cache Order and sizes of registers found in ext/gdb-xml/riscv.xml To add support for more CSRs: More... | |

Additional Inherited Members | |

Protected Attributes inherited from gem5::BaseGdbRegCache Protected Attributes inherited from gem5::BaseGdbRegCache | |

| BaseRemoteGDB * | gdb |

Detailed Description

Definition at line 61 of file remote_gdb.hh.

Member Function Documentation

◆ BaseGdbRegCache()

|

inlineprivate |

Definition at line 134 of file remote_gdb.hh.

◆ data()

|

inlinevirtual |

Return the pointer to the raw bytes buffer containing the register values.

Each byte of this buffer is literally encoded as two hex digits in the g or G RSP packet.

Implements gem5::BaseGdbRegCache.

Definition at line 133 of file remote_gdb.hh.

References r.

◆ getRegs()

|

virtual |

Fill the raw buffer from the registers in the ThreadContext.

Implements gem5::BaseGdbRegCache.

Definition at line 189 of file remote_gdb.cc.

References gem5::RiscvISA::CSR_CYCLE, gem5::RiscvISA::CSR_FCSR, gem5::RiscvISA::CSR_FFLAGS, gem5::RiscvISA::CSR_FRM, gem5::RiscvISA::CSR_MARCHID, gem5::RiscvISA::CSR_MCAUSE, gem5::RiscvISA::CSR_MCOUNTEREN, gem5::RiscvISA::CSR_MEDELEG, gem5::RiscvISA::CSR_MEPC, gem5::RiscvISA::CSR_MHARTID, gem5::RiscvISA::CSR_MIDELEG, gem5::RiscvISA::CSR_MIE, gem5::RiscvISA::CSR_MIMPID, gem5::RiscvISA::CSR_MIP, gem5::RiscvISA::CSR_MISA, gem5::RiscvISA::CSR_MSCRATCH, gem5::RiscvISA::CSR_MSTATUS, gem5::RiscvISA::CSR_MTVAL, gem5::RiscvISA::CSR_MTVEC, gem5::RiscvISA::CSR_MVENDORID, gem5::RiscvISA::CSR_SATP, gem5::RiscvISA::CSR_SCAUSE, gem5::RiscvISA::CSR_SCOUNTEREN, gem5::RiscvISA::CSR_SEDELEG, gem5::RiscvISA::CSR_SEPC, gem5::RiscvISA::CSR_SIDELEG, gem5::RiscvISA::CSR_SIE, gem5::RiscvISA::CSR_SIP, gem5::RiscvISA::CSR_SSCRATCH, gem5::RiscvISA::CSR_SSTATUS, gem5::RiscvISA::CSR_STVAL, gem5::RiscvISA::CSR_STVEC, gem5::RiscvISA::CSR_TIME, gem5::RiscvISA::CSR_UCAUSE, gem5::RiscvISA::CSR_UEPC, gem5::RiscvISA::CSR_UIE, gem5::RiscvISA::CSR_UIP, gem5::RiscvISA::CSR_USCRATCH, gem5::RiscvISA::CSR_USTATUS, gem5::RiscvISA::CSR_UTVAL, gem5::RiscvISA::CSR_UTVEC, gem5::RiscvISA::CSRData, gem5::RiscvISA::CSRMasks, DPRINTF, gem5::X86ISA::floatRegClass, gem5::ThreadContext::getReg(), gem5::ArmISA::i, gem5::PCStateBase::instAddr(), gem5::ArmISA::intRegClass, gem5::MipsISA::float_reg::NumArchRegs, gem5::ArmISA::cc_reg::NumRegs, gem5::ThreadContext::pcState(), gem5::VegaISA::r, gem5::ThreadContext::readMiscReg(), and gem5::ThreadContext::readMiscRegNoEffect().

◆ name()

|

inlinevirtual |

Return the name to use in places like DPRINTF.

Having each concrete superclass redefine this member is useful in situations where the class of the regCache can change on the fly.

Implements gem5::BaseGdbRegCache.

Definition at line 139 of file remote_gdb.hh.

References gem5::BaseGdbRegCache::gdb, and gem5::BaseRemoteGDB::name().

◆ setRegs()

|

virtual |

Set the ThreadContext's registers from the values in the raw buffer.

Implements gem5::BaseGdbRegCache.

Definition at line 297 of file remote_gdb.cc.

References gem5::RiscvISA::CSR_CYCLE, gem5::RiscvISA::CSR_FCSR, gem5::RiscvISA::CSR_FFLAGS, gem5::RiscvISA::CSR_FRM, gem5::RiscvISA::CSR_MARCHID, gem5::RiscvISA::CSR_MCAUSE, gem5::RiscvISA::CSR_MCOUNTEREN, gem5::RiscvISA::CSR_MEDELEG, gem5::RiscvISA::CSR_MEPC, gem5::RiscvISA::CSR_MHARTID, gem5::RiscvISA::CSR_MIDELEG, gem5::RiscvISA::CSR_MIE, gem5::RiscvISA::CSR_MIMPID, gem5::RiscvISA::CSR_MIP, gem5::RiscvISA::CSR_MISA, gem5::RiscvISA::CSR_MSCRATCH, gem5::RiscvISA::CSR_MSTATUS, gem5::RiscvISA::CSR_MTVAL, gem5::RiscvISA::CSR_MTVEC, gem5::RiscvISA::CSR_MVENDORID, gem5::RiscvISA::CSR_SATP, gem5::RiscvISA::CSR_SCAUSE, gem5::RiscvISA::CSR_SCOUNTEREN, gem5::RiscvISA::CSR_SEDELEG, gem5::RiscvISA::CSR_SEPC, gem5::RiscvISA::CSR_SIDELEG, gem5::RiscvISA::CSR_SIE, gem5::RiscvISA::CSR_SIP, gem5::RiscvISA::CSR_SSCRATCH, gem5::RiscvISA::CSR_SSTATUS, gem5::RiscvISA::CSR_STVAL, gem5::RiscvISA::CSR_STVEC, gem5::RiscvISA::CSR_TIME, gem5::RiscvISA::CSR_UCAUSE, gem5::RiscvISA::CSR_UEPC, gem5::RiscvISA::CSR_UIE, gem5::RiscvISA::CSR_UIP, gem5::RiscvISA::CSR_USCRATCH, gem5::RiscvISA::CSR_USTATUS, gem5::RiscvISA::CSR_UTVAL, gem5::RiscvISA::CSR_UTVEC, gem5::RiscvISA::CSRData, gem5::RiscvISA::CSRMasks, DPRINTF, gem5::X86ISA::floatRegClass, gem5::ArmISA::i, gem5::ArmISA::intRegClass, gem5::ArmISA::mask, gem5::MipsISA::float_reg::NumArchRegs, gem5::ArmISA::cc_reg::NumRegs, gem5::ThreadContext::pcState(), gem5::VegaISA::r, gem5::ThreadContext::readMiscReg(), gem5::ThreadContext::readMiscRegNoEffect(), gem5::ThreadContext::setMiscReg(), gem5::ThreadContext::setMiscRegNoEffect(), and gem5::ThreadContext::setReg().

◆ size()

|

inlinevirtual |

Return the size of the raw buffer, in bytes (i.e., half of the number of digits in the g/G packet).

Implements gem5::BaseGdbRegCache.

Definition at line 134 of file remote_gdb.hh.

References r.

Member Data Documentation

◆ cycle

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::cycle |

Definition at line 83 of file remote_gdb.hh.

◆ fcsr

| uint32_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::fcsr |

Definition at line 80 of file remote_gdb.hh.

◆ fflags

| uint32_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::fflags |

Definition at line 78 of file remote_gdb.hh.

◆ fpu

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::fpu[float_reg::NumRegs] |

Definition at line 77 of file remote_gdb.hh.

◆ frm

| uint32_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::frm |

Definition at line 79 of file remote_gdb.hh.

◆ gpr

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::gpr[int_reg::NumArchRegs] |

Definition at line 75 of file remote_gdb.hh.

◆ hbadaddr

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hbadaddr |

Definition at line 129 of file remote_gdb.hh.

◆ hcause

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hcause |

Definition at line 128 of file remote_gdb.hh.

◆ hedeleg

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hedeleg |

Definition at line 122 of file remote_gdb.hh.

◆ hepc

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hepc |

Definition at line 127 of file remote_gdb.hh.

◆ hideleg

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hideleg |

Definition at line 123 of file remote_gdb.hh.

◆ hie

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hie |

Definition at line 124 of file remote_gdb.hh.

◆ hip

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hip |

Definition at line 130 of file remote_gdb.hh.

◆ hscratch

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hscratch |

Definition at line 126 of file remote_gdb.hh.

◆ hstatus

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::hstatus |

Definition at line 121 of file remote_gdb.hh.

◆ htvec

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::htvec |

Definition at line 125 of file remote_gdb.hh.

◆ marchid

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::marchid |

Definition at line 106 of file remote_gdb.hh.

◆ mcause

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mcause |

Definition at line 118 of file remote_gdb.hh.

◆ mcounteren

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mcounteren |

Definition at line 115 of file remote_gdb.hh.

◆ medeleg

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::medeleg |

Definition at line 111 of file remote_gdb.hh.

◆ mepc

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mepc |

Definition at line 117 of file remote_gdb.hh.

◆ mhartid

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mhartid |

Definition at line 108 of file remote_gdb.hh.

◆ mideleg

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mideleg |

Definition at line 112 of file remote_gdb.hh.

◆ mie

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mie |

Definition at line 113 of file remote_gdb.hh.

◆ mimpid

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mimpid |

Definition at line 107 of file remote_gdb.hh.

◆ mip

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mip |

Definition at line 120 of file remote_gdb.hh.

◆ misa

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::misa |

Definition at line 110 of file remote_gdb.hh.

◆ mscratch

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mscratch |

Definition at line 116 of file remote_gdb.hh.

◆ mstatus

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mstatus |

Definition at line 109 of file remote_gdb.hh.

◆ mtval

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mtval |

Definition at line 119 of file remote_gdb.hh.

◆ mtvec

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mtvec |

Definition at line 114 of file remote_gdb.hh.

◆ mvendorid

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::mvendorid |

Definition at line 105 of file remote_gdb.hh.

◆ pc

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::pc |

Definition at line 76 of file remote_gdb.hh.

◆ placeholder

| uint32_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::placeholder |

Definition at line 82 of file remote_gdb.hh.

◆

| struct { ... } gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::r |

RISC-V Register Cache Order and sizes of registers found in ext/gdb-xml/riscv.xml To add support for more CSRs:

- Uncomment relevant lines in ext/gdb-xml/riscv-64bit-csr.xml

- Add register to struct below

- Modify RiscvGdbRegCache::getRegs and setRegs

◆ satp

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::satp |

Definition at line 104 of file remote_gdb.hh.

◆ scause

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::scause |

Definition at line 101 of file remote_gdb.hh.

◆ scounteren

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::scounteren |

Definition at line 98 of file remote_gdb.hh.

◆ sedeleg

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::sedeleg |

Definition at line 94 of file remote_gdb.hh.

◆ sepc

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::sepc |

Definition at line 100 of file remote_gdb.hh.

◆ sideleg

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::sideleg |

Definition at line 95 of file remote_gdb.hh.

◆ sie

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::sie |

Definition at line 96 of file remote_gdb.hh.

◆ sip

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::sip |

Definition at line 103 of file remote_gdb.hh.

◆ sscratch

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::sscratch |

Definition at line 99 of file remote_gdb.hh.

◆ sstatus

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::sstatus |

Definition at line 93 of file remote_gdb.hh.

◆ stval

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::stval |

Definition at line 102 of file remote_gdb.hh.

◆ stvec

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::stvec |

Definition at line 97 of file remote_gdb.hh.

◆ time

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::time |

Definition at line 84 of file remote_gdb.hh.

◆ ucause

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::ucause |

Definition at line 90 of file remote_gdb.hh.

◆ uepc

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::uepc |

Definition at line 89 of file remote_gdb.hh.

◆ uie

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::uie |

Definition at line 86 of file remote_gdb.hh.

◆ uip

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::uip |

Definition at line 92 of file remote_gdb.hh.

◆ uscratch

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::uscratch |

Definition at line 88 of file remote_gdb.hh.

◆ ustatus

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::ustatus |

Definition at line 85 of file remote_gdb.hh.

◆ utval

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::utval |

Definition at line 91 of file remote_gdb.hh.

◆ utvec

| uint64_t gem5::RiscvISA::RemoteGDB::RiscvGdbRegCache::utvec |

Definition at line 87 of file remote_gdb.hh.

The documentation for this class was generated from the following files:

- arch/riscv/remote_gdb.hh

- arch/riscv/remote_gdb.cc