#include <pcstate.hh>

Public Member Functions | |

| SimplePCState (const SimplePCState &other) | |

| SimplePCState & | operator= (const SimplePCState &other)=default |

| SimplePCState () | |

| SimplePCState (Addr val) | |

| PCStateBase * | clone () const override |

| void | set (Addr val) override |

| Force this PC to reflect a particular value, resetting all its other fields around it. | |

| bool | branching () const override |

| void | advance () override |

| Public Member Functions inherited from gem5::GenericISA::PCStateWithNext | |

| Addr | pc () const |

| void | pc (Addr val) |

| Addr | npc () const |

| void | npc (Addr val) |

| MicroPC | upc () const |

| void | upc (MicroPC val) |

| MicroPC | nupc () const |

| void | nupc (MicroPC val) |

| void | uReset () override |

| void | setNPC (Addr val) |

| void | output (std::ostream &os) const override |

| void | update (const PCStateBase &other) override |

| bool | equals (const PCStateBase &other) const override |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::PCStateBase | |

| virtual | ~PCStateBase ()=default |

| template<class Target> | |

| Target & | as () |

| template<class Target> | |

| const Target & | as () const |

| void | update (const PCStateBase *ptr) |

| Addr | instAddr () const |

| Returns the memory address of the instruction this PC points to. | |

| MicroPC | microPC () const |

| Returns the current micropc. | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Protected Types | |

| typedef PCStateWithNext | Base |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Protected Member Functions inherited from gem5::GenericISA::PCStateWithNext | |

| PCStateWithNext (const PCStateWithNext &other) | |

| PCStateWithNext & | operator= (const PCStateWithNext &other)=default |

| PCStateWithNext () | |

| Protected Member Functions inherited from gem5::PCStateBase | |

| PCStateBase (const PCStateBase &other) | |

| PCStateBase & | operator= (const PCStateBase &other)=default |

| PCStateBase () | |

| Protected Attributes inherited from gem5::GenericISA::PCStateWithNext | |

| Addr | _npc = 0 |

| MicroPC | _nupc = 1 |

| Protected Attributes inherited from gem5::PCStateBase | |

| Addr | _pc = 0 |

| MicroPC | _upc = 0 |

Detailed Description

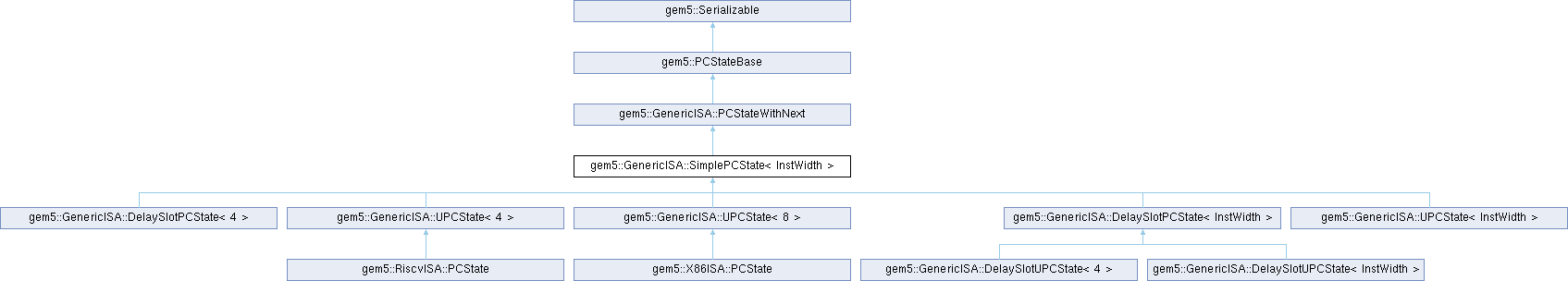

class gem5::GenericISA::SimplePCState< InstWidth >

Definition at line 354 of file pcstate.hh.

Member Typedef Documentation

◆ Base

|

protected |

Definition at line 357 of file pcstate.hh.

Constructor & Destructor Documentation

◆ SimplePCState() [1/3]

|

inline |

Definition at line 360 of file pcstate.hh.

References SimplePCState().

Referenced by operator=(), and SimplePCState().

◆ SimplePCState() [2/3]

|

inline |

Definition at line 362 of file pcstate.hh.

Referenced by clone().

◆ SimplePCState() [3/3]

|

inlineexplicit |

Definition at line 363 of file pcstate.hh.

References gem5::ArmISA::set, and gem5::X86ISA::val.

Member Function Documentation

◆ advance()

|

inlineoverridevirtual |

Implements gem5::PCStateBase.

Definition at line 392 of file pcstate.hh.

References gem5::GenericISA::PCStateWithNext::_npc, and gem5::PCStateBase::_pc.

Referenced by gem5::ArmISA::BranchImm64::branchTarget(), gem5::ArmISA::BranchImmImmReg64::branchTarget(), gem5::ArmISA::BranchImmReg64::branchTarget(), gem5::RiscvISA::RiscvStaticInst::buildRetPC(), and gem5::GenericISA::UPCState< 4 >::uEnd().

◆ branching()

|

inlineoverridevirtual |

Implements gem5::PCStateBase.

Reimplemented in gem5::GenericISA::UPCState< InstWidth >, gem5::GenericISA::UPCState< 4 >, and gem5::GenericISA::UPCState< 8 >.

Definition at line 385 of file pcstate.hh.

References gem5::GenericISA::PCStateWithNext::npc(), and gem5::GenericISA::PCStateWithNext::pc().

◆ clone()

|

inlineoverridevirtual |

Implements gem5::PCStateBase.

Reimplemented in gem5::GenericISA::UPCState< InstWidth >, gem5::GenericISA::UPCState< 4 >, and gem5::GenericISA::UPCState< 8 >.

Definition at line 366 of file pcstate.hh.

References SimplePCState().

◆ operator=()

|

default |

References SimplePCState().

◆ set()

|

inlineoverridevirtual |

Force this PC to reflect a particular value, resetting all its other fields around it.

This is useful for in place (re)initialization.

- Parameters

-

val The value to set the PC to.

Reimplemented from gem5::GenericISA::PCStateWithNext.

Reimplemented in gem5::GenericISA::UPCState< InstWidth >, gem5::GenericISA::UPCState< 4 >, and gem5::GenericISA::UPCState< 8 >.

Definition at line 378 of file pcstate.hh.

References gem5::GenericISA::PCStateWithNext::npc(), gem5::GenericISA::PCStateWithNext::set(), and gem5::X86ISA::val.

Referenced by gem5::ArmISA::SkipFunc::returnFromFuncIn(), gem5::GenericISA::DelaySlotPCState< 4 >::set(), gem5::GenericISA::UPCState< 4 >::set(), gem5::ArmISA::RemoteGDB::AArch32GdbRegCache::setRegs(), gem5::ArmISA::RemoteGDB::AArch64GdbRegCache::setRegs(), and gem5::fastmodel::FastmodelRemoteGDB::AArch64GdbRegCache::setRegs().

The documentation for this class was generated from the following file:

- arch/generic/pcstate.hh

Generated on Mon Oct 27 2025 04:13:19 for gem5 by doxygen 1.14.0