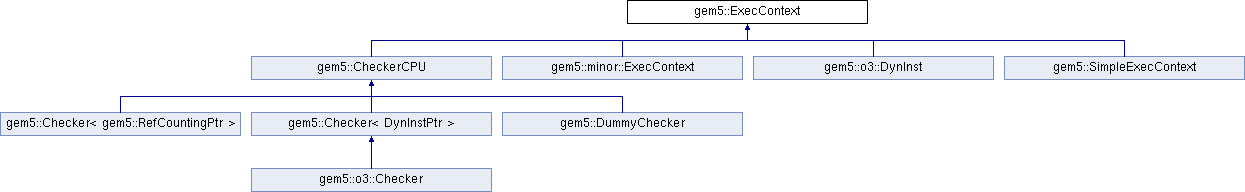

The ExecContext is an abstract base class the provides the interface used by the ISA to manipulate the state of the CPU model. More...

#include <exec_context.hh>

Public Member Functions | |

| virtual ThreadContext * | tcBase () const =0 |

| Returns a pointer to the ThreadContext. More... | |

Integer Register Interfaces | |

| virtual RegVal | readIntRegOperand (const StaticInst *si, int idx)=0 |

| Reads an integer register. More... | |

| virtual void | setIntRegOperand (const StaticInst *si, int idx, RegVal val)=0 |

| Sets an integer register to a value. More... | |

Floating Point Register Interfaces | |

| virtual RegVal | readFloatRegOperandBits (const StaticInst *si, int idx)=0 |

| Reads a floating point register in its binary format, instead of by value. More... | |

| virtual void | setFloatRegOperandBits (const StaticInst *si, int idx, RegVal val)=0 |

| Sets the bits of a floating point register of single width to a binary value. More... | |

| virtual const TheISA::VecRegContainer & | readVecRegOperand (const StaticInst *si, int idx) const =0 |

| Vector Register Interfaces. More... | |

| virtual TheISA::VecRegContainer & | getWritableVecRegOperand (const StaticInst *si, int idx)=0 |

| Gets destination vector register operand for modification. More... | |

| virtual void | setVecRegOperand (const StaticInst *si, int idx, const TheISA::VecRegContainer &val)=0 |

| Sets a destination vector register operand to a value. More... | |

| virtual RegVal | readVecElemOperand (const StaticInst *si, int idx) const =0 |

| Vector Elem Interfaces. More... | |

| virtual void | setVecElemOperand (const StaticInst *si, int idx, RegVal val)=0 |

| Sets a vector register to a value. More... | |

| virtual const TheISA::VecPredRegContainer & | readVecPredRegOperand (const StaticInst *si, int idx) const =0 |

| Predicate registers interface. More... | |

| virtual TheISA::VecPredRegContainer & | getWritableVecPredRegOperand (const StaticInst *si, int idx)=0 |

| Gets destination predicate register operand for modification. More... | |

| virtual void | setVecPredRegOperand (const StaticInst *si, int idx, const TheISA::VecPredRegContainer &val)=0 |

| Sets a destination predicate register operand to a value. More... | |

Condition Code Registers | |

| virtual RegVal | readCCRegOperand (const StaticInst *si, int idx)=0 |

| virtual void | setCCRegOperand (const StaticInst *si, int idx, RegVal val)=0 |

Misc Register Interfaces | |

| virtual RegVal | readMiscRegOperand (const StaticInst *si, int idx)=0 |

| virtual void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val)=0 |

| virtual RegVal | readMiscReg (int misc_reg)=0 |

| Reads a miscellaneous register, handling any architectural side effects due to reading that register. More... | |

| virtual void | setMiscReg (int misc_reg, RegVal val)=0 |

| Sets a miscellaneous register, handling any architectural side effects due to writing that register. More... | |

PC Control | |

| virtual const PCStateBase & | pcState () const =0 |

| virtual void | pcState (const PCStateBase &val)=0 |

Memory Interface | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Perform an atomic memory read operation. More... | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Initiate a timing memory read operation. More... | |

| virtual Fault | initiateHtmCmd (Request::Flags flags)=0 |

| Initiate an HTM command, e.g. More... | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable)=0 |

| For atomic-mode contexts, perform an atomic memory write operation. More... | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More... | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More... | |

| virtual void | setStCondFailures (unsigned int sc_failures)=0 |

| Sets the number of consecutive store conditional failures. More... | |

| virtual unsigned int | readStCondFailures () const =0 |

| Returns the number of consecutive store conditional failures. More... | |

ARM-Specific Interfaces | |

| virtual bool | readPredicate () const =0 |

| virtual void | setPredicate (bool val)=0 |

| virtual bool | readMemAccPredicate () const =0 |

| virtual void | setMemAccPredicate (bool val)=0 |

| virtual uint64_t | newHtmTransactionUid () const =0 |

| virtual uint64_t | getHtmTransactionUid () const =0 |

| virtual bool | inHtmTransactionalState () const =0 |

| virtual uint64_t | getHtmTransactionalDepth () const =0 |

X86-Specific Interfaces | |

| virtual void | demapPage (Addr vaddr, uint64_t asn)=0 |

| Invalidate a page in the DTLB and ITLB. More... | |

| virtual void | armMonitor (Addr address)=0 |

| virtual bool | mwait (PacketPtr pkt)=0 |

| virtual void | mwaitAtomic (ThreadContext *tc)=0 |

| virtual AddressMonitor * | getAddrMonitor ()=0 |

Detailed Description

The ExecContext is an abstract base class the provides the interface used by the ISA to manipulate the state of the CPU model.

Register accessor methods in this class typically provide the index of the instruction's operand (e.g., 0 or 1), not the architectural register index, to simplify the implementation of register renaming. The architectural register index can be found by indexing into the instruction's own operand index table.

- Note

- The methods in this class typically take a raw pointer to the StaticInst is provided instead of a ref-counted StaticInstPtr to reduce overhead as an argument. This is fine as long as the implementation doesn't copy the pointer into any long-term storage (which is pretty hard to imagine they would have reason to do).

Definition at line 73 of file exec_context.hh.

Member Function Documentation

◆ amoMem()

|

inlinevirtual |

For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation)

Reimplemented in gem5::SimpleExecContext.

Definition at line 238 of file exec_context.hh.

References panic.

◆ armMonitor()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ demapPage()

|

pure virtual |

Invalidate a page in the DTLB and ITLB.

Implemented in gem5::SimpleExecContext, gem5::CheckerCPU, gem5::o3::DynInst, and gem5::minor::ExecContext.

◆ getAddrMonitor()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ getHtmTransactionalDepth()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ getHtmTransactionUid()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ getWritableVecPredRegOperand()

|

pure virtual |

Gets destination predicate register operand for modification.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ getWritableVecRegOperand()

|

pure virtual |

Gets destination vector register operand for modification.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ inHtmTransactionalState()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ initiateHtmCmd()

|

pure virtual |

Initiate an HTM command, e.g.

tell Ruby we're starting/stopping a transaction

Implemented in gem5::SimpleExecContext, gem5::o3::DynInst, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ initiateMemAMO()

|

inlinevirtual |

For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation)

Reimplemented in gem5::SimpleExecContext, and gem5::minor::ExecContext.

Definition at line 249 of file exec_context.hh.

References panic.

◆ initiateMemRead()

|

inlinevirtual |

Initiate a timing memory read operation.

Must be overridden for exec contexts that support timing memory mode. Not pure virtual since exec contexts that only support atomic memory mode need not override (though in that case this function should never be called).

Reimplemented in gem5::SimpleExecContext, and gem5::minor::ExecContext.

Definition at line 214 of file exec_context.hh.

References panic.

Referenced by gem5::X86ISA::initiateMemRead().

◆ mwait()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ mwaitAtomic()

|

pure virtual |

Implemented in gem5::SimpleExecContext, gem5::CheckerCPU, gem5::minor::ExecContext, and gem5::o3::DynInst.

◆ newHtmTransactionUid()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ pcState() [1/2]

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

Referenced by gem5::DecoderFaultInst::execute(), gem5::DebugStep::execute(), gem5::ArmISA::ArmStaticInst::readPC(), gem5::ArmISA::ArmStaticInst::setAIWNextPC(), gem5::ArmISA::ArmStaticInst::setIWNextPC(), and gem5::ArmISA::ArmStaticInst::setNextPC().

◆ pcState() [2/2]

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readCCRegOperand()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::minor::ExecContext, and gem5::CheckerCPU.

◆ readFloatRegOperandBits()

|

pure virtual |

Reads a floating point register in its binary format, instead of by value.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readIntRegOperand()

|

pure virtual |

Reads an integer register.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readMem()

|

inlinevirtual |

Perform an atomic memory read operation.

Must be overridden for exec contexts that support atomic memory mode. Not pure virtual since exec contexts that only support timing memory mode need not override (though in that case this function should never be called).

Reimplemented in gem5::SimpleExecContext.

Definition at line 200 of file exec_context.hh.

References panic.

Referenced by gem5::X86ISA::readMemAtomic(), and gem5::X86ISA::readPackedMemAtomic().

◆ readMemAccPredicate()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readMiscReg()

|

pure virtual |

Reads a miscellaneous register, handling any architectural side effects due to reading that register.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

Referenced by gem5::ArmISA::ISA::handleLockedSnoopHit().

◆ readMiscRegOperand()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readPredicate()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readStCondFailures()

|

pure virtual |

Returns the number of consecutive store conditional failures.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readVecElemOperand()

|

pure virtual |

Vector Elem Interfaces.

Reads an element of a vector register.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readVecPredRegOperand()

|

pure virtual |

Predicate registers interface.

Reads source predicate register operand.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ readVecRegOperand()

|

pure virtual |

Vector Register Interfaces.

Reads source vector register operand.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setCCRegOperand()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::minor::ExecContext, and gem5::CheckerCPU.

◆ setFloatRegOperandBits()

|

pure virtual |

Sets the bits of a floating point register of single width to a binary value.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setIntRegOperand()

|

pure virtual |

Sets an integer register to a value.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setMemAccPredicate()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setMiscReg()

|

pure virtual |

Sets a miscellaneous register, handling any architectural side effects due to writing that register.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

Referenced by gem5::ArmISA::ISA::globalClearExclusive(), gem5::ArmISA::ISA::handleLockedRead(), and gem5::ArmISA::ISA::handleLockedSnoopHit().

◆ setMiscRegOperand()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setPredicate()

|

pure virtual |

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setStCondFailures()

|

pure virtual |

Sets the number of consecutive store conditional failures.

Implemented in gem5::minor::ExecContext, gem5::o3::DynInst, gem5::SimpleExecContext, and gem5::CheckerCPU.

◆ setVecElemOperand()

|

pure virtual |

Sets a vector register to a value.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setVecPredRegOperand()

|

pure virtual |

Sets a destination predicate register operand to a value.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ setVecRegOperand()

|

pure virtual |

Sets a destination vector register operand to a value.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

◆ tcBase()

|

pure virtual |

Returns a pointer to the ThreadContext.

Implemented in gem5::o3::DynInst, gem5::SimpleExecContext, gem5::CheckerCPU, and gem5::minor::ExecContext.

Referenced by gem5::X86ISA::MicroHalt::execute(), gem5::DebugStep::execute(), gem5::MiscRegImplDefined64::execute(), gem5::McrMrcMiscInst::execute(), gem5::McrMrcImplDefined::execute(), gem5::ArmISA::ISA::globalClearExclusive(), gem5::ArmISA::ISA::handleLockedRead(), gem5::ArmISA::ISA::handleLockedSnoop(), gem5::ArmISA::ISA::handleLockedSnoopHit(), gem5::ArmISA::ISA::handleLockedWrite(), gem5::MipsISA::readRegOtherThread(), gem5::MipsISA::setRegOtherThread(), and gem5::ArmISA::ArmStaticInst::softwareBreakpoint32().

◆ writeMem()

|

pure virtual |

For atomic-mode contexts, perform an atomic memory write operation.

For timing-mode contexts, initiate a timing memory write operation.

Implemented in gem5::SimpleExecContext, and gem5::minor::ExecContext.

Referenced by gem5::X86ISA::writeMemAtomic(), gem5::X86ISA::writeMemTiming(), and gem5::X86ISA::writePackedMem().

The documentation for this class was generated from the following file:

- cpu/exec_context.hh