#include <pm4_packet_processor.hh>

Public Member Functions | |

| PM4PacketProcessor (const PM4PacketProcessorParams &p) | |

| void | setGPUDevice (AMDGPUDevice *gpu_device) |

| Tick | write (PacketPtr pkt) override |

| Inherited methods. | |

| Tick | read (PacketPtr pkt) override |

| Pure virtual function that the device must implement. | |

| AddrRangeList | getAddrRanges () const override |

| Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| TranslationGenPtr | translate (Addr vaddr, Addr size) override |

| Method for functional translation. | |

| uint32_t | getKiqDoorbellOffset () |

| uint32_t | getPqDoorbellOffset () |

| Addr | getGARTAddr (Addr addr) const |

| PM4Queue * | getQueue (Addr offset, bool gfx=false) |

| Based on an offset communicated through doorbell write, the PM4PacketProcessor identifies which queue needs processing. | |

| void | mapPq (Addr offset) |

| The first graphics queue, the Primary Queueu a.k.a. | |

| void | mapKiq (Addr offset) |

| The first compute queue, the Kernel Interface Queueu a.k.a. | |

| void | newQueue (QueueDesc *q, Addr offset, PM4MapQueues *pkt=nullptr, int id=-1) |

| This method creates a new PM4Queue based on a queue descriptor and an offset. | |

| void | process (PM4Queue *q, Addr wptrOffset) |

| This method start processing a PM4Queue from the current read pointer to the newly communicated write pointer (i.e., wptrOffset). | |

| void | updateReadIndex (Addr offset, uint64_t rd_idx) |

| Update read index on doorbell rings. | |

| void | decodeNext (PM4Queue *q) |

| This method decodes the next packet in a PM4Queue. | |

| void | decodeHeader (PM4Queue *q, PM4Header header) |

| This method calls other PM4 packet processing methods based on the header of a PM4 packet. | |

| void | writeData (PM4Queue *q, PM4WriteData *pkt) |

| void | writeDataDone (PM4Queue *q, PM4WriteData *pkt, Addr addr) |

| void | mapQueues (PM4Queue *q, PM4MapQueues *pkt) |

| void | unmapQueues (PM4Queue *q, PM4UnmapQueues *pkt) |

| void | doneMQDWrite (Addr mqdAddr, Addr addr) |

| void | mapProcess (uint32_t pasid, uint64_t ptBase, uint32_t shMemBases) |

| void | mapProcessGfx9 (PM4Queue *q, PM4MapProcess *pkt) |

| void | mapProcessGfx90a (PM4Queue *q, PM4MapProcessMI200 *pkt) |

| void | processMQD (PM4MapQueues *pkt, PM4Queue *q, Addr addr, QueueDesc *mqd, uint16_t vmid) |

| void | processSDMAMQD (PM4MapQueues *pkt, PM4Queue *q, Addr addr, SDMAQueueDesc *mqd, uint16_t vmid) |

| void | releaseMem (PM4Queue *q, PM4ReleaseMem *pkt) |

| void | releaseMemDone (PM4Queue *q, PM4ReleaseMem *pkt, Addr addr) |

| void | runList (PM4Queue *q, PM4RunList *pkt) |

| void | indirectBuffer (PM4Queue *q, PM4IndirectBuf *pkt) |

| void | switchBuffer (PM4Queue *q, PM4SwitchBuf *pkt) |

| void | setUconfigReg (PM4Queue *q, PM4SetUconfigReg *pkt) |

| void | waitRegMem (PM4Queue *q, PM4WaitRegMem *pkt) |

| void | queryStatus (PM4Queue *q, PM4QueryStatus *pkt) |

| void | queryStatusDone (PM4Queue *q, PM4QueryStatus *pkt) |

| void | writeMMIO (PacketPtr pkt, Addr mmio_offset) |

| void | setHqdVmid (uint32_t data) |

| void | setHqdActive (uint32_t data) |

| void | setHqdPqBase (uint32_t data) |

| void | setHqdPqBaseHi (uint32_t data) |

| void | setHqdPqDoorbellCtrl (uint32_t data) |

| void | setHqdPqPtr (uint32_t data) |

| void | setHqdPqWptrLo (uint32_t data) |

| void | setHqdPqWptrHi (uint32_t data) |

| void | setHqdPqRptrReportAddr (uint32_t data) |

| void | setHqdPqRptrReportAddrHi (uint32_t data) |

| void | setHqdPqWptrPollAddr (uint32_t data) |

| void | setHqdPqWptrPollAddrHi (uint32_t data) |

| void | setHqdPqControl (uint32_t data) |

| void | setHqdIbCtrl (uint32_t data) |

| void | setRbVmid (uint32_t data) |

| void | setRbCntl (uint32_t data) |

| void | setRbWptrLo (uint32_t data) |

| void | setRbWptrHi (uint32_t data) |

| void | setRbRptrAddrLo (uint32_t data) |

| void | setRbRptrAddrHi (uint32_t data) |

| void | setRbWptrPollAddrLo (uint32_t data) |

| void | setRbWptrPollAddrHi (uint32_t data) |

| void | setRbBaseLo (uint32_t data) |

| void | setRbBaseHi (uint32_t data) |

| void | setRbDoorbellCntrl (uint32_t data) |

| void | setRbDoorbellRangeLo (uint32_t data) |

| void | setRbDoorbellRangeHi (uint32_t data) |

Public Member Functions inherited from gem5::DmaVirtDevice Public Member Functions inherited from gem5::DmaVirtDevice | |

| DmaVirtDevice (const Params &p) | |

| virtual | ~DmaVirtDevice () |

| void | dmaReadVirt (Addr host_addr, unsigned size, DmaCallback *cb, void *data, Tick delay=0) |

| Initiate a DMA read from virtual address host_addr. | |

| void | dmaWriteVirt (Addr host_addr, unsigned size, DmaCallback *b, void *data, Tick delay=0) |

| Initiate a DMA write from virtual address host_addr. | |

| void | dmaVirt (DmaFnPtr dmaFn, Addr host_addr, unsigned size, DmaCallback *cb, void *data, Tick delay=0) |

| Initiate a call to DmaDevice using DmaFnPtr do a DMA starting from virtual address host_addr for size number of bytes on the data. | |

| virtual TranslationGenPtr | translate (Addr vaddr, Addr size)=0 |

| Function used to translate a range of addresses from virtual to physical addresses. | |

Public Member Functions inherited from gem5::DmaDevice Public Member Functions inherited from gem5::DmaDevice | |

| DmaDevice (const Params &p) | |

| virtual | ~DmaDevice ()=default |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, uint32_t sid, uint32_t ssid, Tick delay=0) |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, uint32_t sid, uint32_t ssid, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| bool | dmaPending () const |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| unsigned int | cacheBlockSize () const |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

Public Member Functions inherited from gem5::PioDevice Public Member Functions inherited from gem5::PioDevice | |

| PioDevice (const Params &p) | |

| virtual | ~PioDevice () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

Public Member Functions inherited from gem5::ClockedObject Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

Public Member Functions inherited from gem5::SimObject Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

Public Member Functions inherited from gem5::EventManager Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Public Member Functions inherited from gem5::Serializable Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| virtual void | serialize (CheckpointOut &cp) const =0 |

| Serialize an object. | |

| virtual void | unserialize (CheckpointIn &cp)=0 |

| Unserialize an object. | |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from gem5::Drainable Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

Public Member Functions inherited from gem5::statistics::Group Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

Public Member Functions inherited from gem5::Named Public Member Functions inherited from gem5::Named | |

| Named (const std::string &name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Public Member Functions inherited from gem5::Clocked Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Private Attributes | |

| AMDGPUDevice * | gpuDevice |

| PrimaryQueue | pq |

| PM4MapQueues | pq_pkt |

| QueueDesc | kiq |

| PM4MapQueues | kiq_pkt |

| std::unordered_map< uint16_t, PM4Queue * > | queues |

| std::unordered_map< uint32_t, PM4Queue * > | queuesMap |

Additional Inherited Members | |

Public Types inherited from gem5::DmaVirtDevice Public Types inherited from gem5::DmaVirtDevice | |

| typedef void(DmaDevice::* | DmaFnPtr) (Addr, int, Event *, uint8_t *, Tick) |

Public Types inherited from gem5::DmaDevice Public Types inherited from gem5::DmaDevice | |

| typedef DmaDeviceParams | Params |

Public Types inherited from gem5::PioDevice Public Types inherited from gem5::PioDevice | |

| using | Params = PioDeviceParams |

Public Types inherited from gem5::ClockedObject Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

Public Types inherited from gem5::SimObject Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Static Public Member Functions inherited from gem5::SimObject Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

Static Public Member Functions inherited from gem5::Serializable Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

Public Attributes inherited from gem5::ClockedObject Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| virtual AddrRangeList | getAddrRanges () const =0 |

| Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to. | |

| virtual Tick | read (PacketPtr pkt)=0 |

| Pure virtual function that the device must implement. | |

| virtual Tick | write (PacketPtr pkt)=0 |

| Pure virtual function that the device must implement. | |

Protected Member Functions inherited from gem5::Drainable Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual DrainState | drain ()=0 |

| Draining is the process of clearing out the states of SimObjects.These are the SimObjects that are partially executed or are partially in flight. | |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

Protected Member Functions inherited from gem5::Clocked Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes inherited from gem5::DmaDevice Protected Attributes inherited from gem5::DmaDevice | |

| DmaPort | dmaPort |

Protected Attributes inherited from gem5::PioDevice Protected Attributes inherited from gem5::PioDevice | |

| System * | sys |

| PioPort< PioDevice > | pioPort |

| The pioPort that handles the requests for us and provides us requests that it sees. | |

Protected Attributes inherited from gem5::SimObject Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

Protected Attributes inherited from gem5::EventManager Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

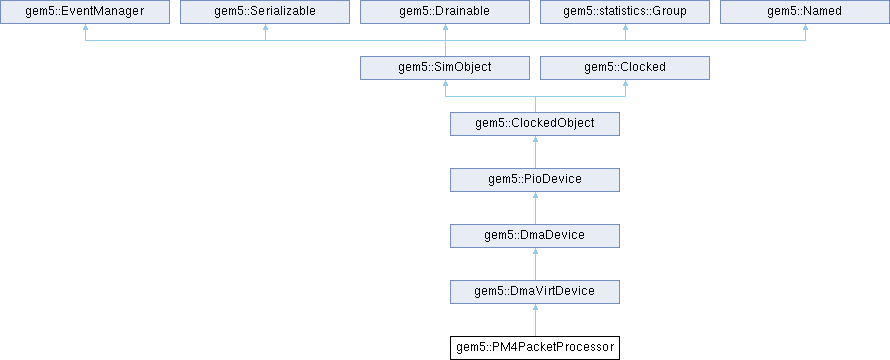

Detailed Description

Definition at line 52 of file pm4_packet_processor.hh.

Constructor & Destructor Documentation

◆ PM4PacketProcessor()

| gem5::PM4PacketProcessor::PM4PacketProcessor | ( | const PM4PacketProcessorParams & | p | ) |

Definition at line 51 of file pm4_packet_processor.cc.

Member Function Documentation

◆ decodeHeader()

This method calls other PM4 packet processing methods based on the header of a PM4 packet.

Definition at line 193 of file pm4_packet_processor.cc.

References decodeNext(), gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, getGARTAddr(), gem5::AMDGPUDevice::getGfxVersion(), gem5::AMDGPUDevice::getVM(), gpuDevice, header, indirectBuffer(), gem5::AMDGPUVM::invalidateTLBs(), gem5::IT_INDIRECT_BUFFER, gem5::IT_INVALIDATE_TLBS, gem5::IT_MAP_PROCESS, gem5::IT_MAP_QUEUES, gem5::IT_NOP, gem5::IT_QUERY_STATUS, gem5::IT_RELEASE_MEM, gem5::IT_RUN_LIST, gem5::IT_SET_UCONFIG_REG, gem5::IT_SWITCH_BUFFER, gem5::IT_UNMAP_QUEUES, gem5::IT_WAIT_REG_MEM, gem5::IT_WRITE_DATA, mapProcessGfx9(), mapProcessGfx90a(), mapQueues(), gem5::ArmISA::q, queryStatus(), releaseMem(), runList(), setUconfigReg(), switchBuffer(), unmapQueues(), waitRegMem(), warn, and writeData().

Referenced by decodeNext().

◆ decodeNext()

| void gem5::PM4PacketProcessor::decodeNext | ( | PM4Queue * | q | ) |

This method decodes the next packet in a PM4Queue.

Definition at line 166 of file pm4_packet_processor.cc.

References decodeHeader(), decodeNext(), gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, getGARTAddr(), header, and gem5::ArmISA::q.

Referenced by decodeHeader(), decodeNext(), indirectBuffer(), mapProcessGfx9(), mapProcessGfx90a(), mapQueues(), process(), queryStatusDone(), releaseMemDone(), runList(), setUconfigReg(), switchBuffer(), unmapQueues(), waitRegMem(), writeData(), and writeDataDone().

◆ doneMQDWrite()

Definition at line 619 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, and DPRINTF.

Referenced by unmapQueues().

◆ getAddrRanges()

|

overridevirtual |

Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to.

- Returns

- a list of non-overlapping address ranges

Implements gem5::PioDevice.

Definition at line 79 of file pm4_packet_processor.cc.

◆ getGARTAddr()

Definition at line 92 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::bits(), gem5::AMDGPUDevice::getVM(), gpuDevice, and gem5::AMDGPUVM::inAGP().

Referenced by decodeHeader(), decodeNext(), mapQueues(), queryStatus(), releaseMem(), unmapQueues(), and writeData().

◆ getKiqDoorbellOffset()

|

inline |

Definition at line 85 of file pm4_packet_processor.hh.

References gem5::GEM5_PACKED::doorbell, and kiq.

Referenced by writeMMIO().

◆ getPqDoorbellOffset()

|

inline |

Definition at line 86 of file pm4_packet_processor.hh.

References gem5::PrimaryQueue::doorbellOffset, and pq.

Referenced by writeMMIO().

◆ getQueue()

Based on an offset communicated through doorbell write, the PM4PacketProcessor identifies which queue needs processing.

Definition at line 102 of file pm4_packet_processor.cc.

References mapKiq(), mapPq(), gem5::ArmISA::offset, and queuesMap.

Referenced by gem5::AMDGPUDevice::writeDoorbell().

◆ indirectBuffer()

| void gem5::PM4PacketProcessor::indirectBuffer | ( | PM4Queue * | q, |

| PM4IndirectBuf * | pkt | ||

| ) |

Definition at line 692 of file pm4_packet_processor.cc.

References decodeNext(), DPRINTF, gem5::GEM5_PACKED::ibBase, gem5::GEM5_PACKED::ibSize, and gem5::ArmISA::q.

Referenced by decodeHeader().

◆ mapKiq()

| void gem5::PM4PacketProcessor::mapKiq | ( | Addr | offset | ) |

The first compute queue, the Kernel Interface Queueu a.k.a.

KIQ, needs to be mapped since all queue details are communicated through MMIOs to special registers.

Definition at line 116 of file pm4_packet_processor.cc.

References DPRINTF, kiq, kiq_pkt, newQueue(), and gem5::ArmISA::offset.

Referenced by getQueue().

◆ mapPq()

| void gem5::PM4PacketProcessor::mapPq | ( | Addr | offset | ) |

The first graphics queue, the Primary Queueu a.k.a.

RB0, needs to be mapped since all queue details are communicated through MMIOs to special registers.

Definition at line 123 of file pm4_packet_processor.cc.

References DPRINTF, newQueue(), gem5::ArmISA::offset, pq, and pq_pkt.

Referenced by getQueue().

◆ mapProcess()

| void gem5::PM4PacketProcessor::mapProcess | ( | uint32_t | pasid, |

| uint64_t | ptBase, | ||

| uint32_t | shMemBases | ||

| ) |

Definition at line 625 of file pm4_packet_processor.cc.

References gem5::AMDGPUDevice::allocateVMID(), gem5::bits(), gem5::AMDGPUDevice::CP(), gem5::AMDGPUDevice::getVM(), gpuDevice, gem5::HW_REG_SH_MEM_BASES, gem5::Shader::setHwReg(), gem5::Shader::setLdsApe(), gem5::AMDGPUVM::setPageTableBase(), gem5::Shader::setScratchApe(), and gem5::GPUCommandProcessor::shader().

Referenced by mapProcessGfx9(), and mapProcessGfx90a().

◆ mapProcessGfx9()

| void gem5::PM4PacketProcessor::mapProcessGfx9 | ( | PM4Queue * | q, |

| PM4MapProcess * | pkt | ||

| ) |

Definition at line 645 of file pm4_packet_processor.cc.

References gem5::GEM5_PACKED::completionSignal, decodeNext(), DPRINTF, mapProcess(), gem5::GEM5_PACKED::pasid, gem5::GEM5_PACKED::processQuantum, gem5::GEM5_PACKED::ptBase, gem5::ArmISA::q, and gem5::GEM5_PACKED::shMemBases.

Referenced by decodeHeader().

◆ mapProcessGfx90a()

| void gem5::PM4PacketProcessor::mapProcessGfx90a | ( | PM4Queue * | q, |

| PM4MapProcessMI200 * | pkt | ||

| ) |

Definition at line 660 of file pm4_packet_processor.cc.

References gem5::GEM5_PACKED::completionSignal, decodeNext(), DPRINTF, mapProcess(), gem5::GEM5_PACKED::pasid, gem5::GEM5_PACKED::processQuantum, gem5::GEM5_PACKED::ptBase, gem5::ArmISA::q, and gem5::GEM5_PACKED::shMemBases.

Referenced by decodeHeader().

◆ mapQueues()

| void gem5::PM4PacketProcessor::mapQueues | ( | PM4Queue * | q, |

| PM4MapQueues * | pkt | ||

| ) |

Definition at line 366 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::GEM5_PACKED::allocFormat, gem5::GEM5_PACKED::checkDisable, decodeNext(), gem5::DmaVirtDevice::dmaReadVirt(), gem5::GEM5_PACKED::doorbellOffset, DPRINTF, gem5::GEM5_PACKED::engineSel, getGARTAddr(), gpuDevice, gem5::AMDGPUDevice::lastVMID(), gem5::AMDGPUDevice::mapDoorbellToVMID(), gem5::GEM5_PACKED::me, gem5::GEM5_PACKED::mqdAddr, gem5::GEM5_PACKED::numQueues, panic, gem5::GEM5_PACKED::pipe, processMQD(), processSDMAMQD(), gem5::ArmISA::q, gem5::GEM5_PACKED::queueSel, gem5::GEM5_PACKED::queueSlot, gem5::GEM5_PACKED::queueType, gem5::GEM5_PACKED::vmid, and gem5::GEM5_PACKED::wptrAddr.

Referenced by decodeHeader().

◆ newQueue()

| void gem5::PM4PacketProcessor::newQueue | ( | QueueDesc * | q, |

| Addr | offset, | ||

| PM4MapQueues * | pkt = nullptr, |

||

| int | id = -1 |

||

| ) |

This method creates a new PM4Queue based on a queue descriptor and an offset.

Definition at line 130 of file pm4_packet_processor.cc.

References gem5::GEM5_PACKED::aql, gem5::GEM5_PACKED::base, gem5::Compute, gem5::ComputeAQL, DPRINTF, gpuDevice, gem5::ArmISA::id, gem5::ArmISA::offset, gem5::ArmISA::q, queues, queuesMap, and gem5::AMDGPUDevice::setDoorbellType().

Referenced by mapKiq(), mapPq(), processMQD(), and unserialize().

◆ process()

This method start processing a PM4Queue from the current read pointer to the newly communicated write pointer (i.e., wptrOffset).

Definition at line 155 of file pm4_packet_processor.cc.

References decodeNext(), and gem5::ArmISA::q.

Referenced by gem5::AMDGPUDevice::writeDoorbell().

◆ processMQD()

| void gem5::PM4PacketProcessor::processMQD | ( | PM4MapQueues * | pkt, |

| PM4Queue * | q, | ||

| Addr | addr, | ||

| QueueDesc * | mqd, | ||

| uint16_t | vmid | ||

| ) |

Definition at line 416 of file pm4_packet_processor.cc.

References gem5::GEM5_PACKED::aql, gem5::GEM5_PACKED::aqlRptr, gem5::GEM5_PACKED::base, gem5::AMDGPUDevice::CP(), gem5::GEM5_PACKED::doorbell, DPRINTF, gpuDevice, gem5::GEM5_PACKED::hqd_active, gem5::GEM5_PACKED::hqd_pq_control, gem5::GEM5_PACKED::hqd_vmid, gem5::GPUCommandProcessor::hsaPacketProc(), gem5::PM4Queue::id(), gem5::AMDGPUDevice::insertQId(), gem5::GEM5_PACKED::mqdBase, gem5::GEM5_PACKED::mqdReadIndex, newQueue(), gem5::ArmISA::offset, queuesMap, gem5::GEM5_PACKED::rptr, and gem5::HSAPacketProcessor::setDeviceQueueDesc().

Referenced by mapQueues().

◆ processSDMAMQD()

| void gem5::PM4PacketProcessor::processSDMAMQD | ( | PM4MapQueues * | pkt, |

| PM4Queue * | q, | ||

| Addr | addr, | ||

| SDMAQueueDesc * | mqd, | ||

| uint16_t | vmid | ||

| ) |

Definition at line 450 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::bits(), gem5::GEM5_PACKED::doorbellOffset, DPRINTF, gem5::GEM5_PACKED::engineSel, gem5::AMDGPUDevice::getSDMAById(), gpuDevice, gem5::GEM5_PACKED::rb_base, gem5::SDMAEngine::registerRLCQueue(), gem5::RLC, gem5::GEM5_PACKED::sdmax_rlcx_ib_base_hi, gem5::GEM5_PACKED::sdmax_rlcx_ib_base_lo, gem5::GEM5_PACKED::sdmax_rlcx_rb_cntl, gem5::GEM5_PACKED::sdmax_rlcx_rb_rptr, gem5::GEM5_PACKED::sdmax_rlcx_rb_rptr_addr_hi, gem5::GEM5_PACKED::sdmax_rlcx_rb_rptr_addr_lo, gem5::GEM5_PACKED::sdmax_rlcx_rb_rptr_hi, gem5::GEM5_PACKED::sdmax_rlcx_rb_wptr, gem5::GEM5_PACKED::sdmax_rlcx_rb_wptr_hi, gem5::AMDGPUDevice::setDoorbellType(), and gem5::AMDGPUDevice::setSDMAEngine().

Referenced by mapQueues().

◆ queryStatus()

| void gem5::PM4PacketProcessor::queryStatus | ( | PM4Queue * | q, |

| PM4QueryStatus * | pkt | ||

| ) |

Definition at line 748 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::GEM5_PACKED::addr, gem5::GEM5_PACKED::command, gem5::GEM5_PACKED::contextId, gem5::GEM5_PACKED::data, gem5::DmaVirtDevice::dmaWriteVirt(), gem5::GEM5_PACKED::doorbellOffset, DPRINTF, gem5::GEM5_PACKED::engineSel, getGARTAddr(), gem5::GEM5_PACKED::interruptSel, panic, gem5::GEM5_PACKED::pasid, gem5::ArmISA::q, and queryStatusDone().

Referenced by decodeHeader().

◆ queryStatusDone()

| void gem5::PM4PacketProcessor::queryStatusDone | ( | PM4Queue * | q, |

| PM4QueryStatus * | pkt | ||

| ) |

Definition at line 773 of file pm4_packet_processor.cc.

References decodeNext(), DPRINTF, and gem5::ArmISA::q.

Referenced by queryStatus().

◆ read()

Pure virtual function that the device must implement.

Called when a read command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 75 of file pm4_packet_processor.hh.

◆ releaseMem()

| void gem5::PM4PacketProcessor::releaseMem | ( | PM4Queue * | q, |

| PM4ReleaseMem * | pkt | ||

| ) |

Definition at line 478 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::GEM5_PACKED::addr, gem5::GEM5_PACKED::dataLo, gem5::GEM5_PACKED::dataSelect, gem5::GEM5_PACKED::destSelect, gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, gem5::GEM5_PACKED::event, gem5::GEM5_PACKED::eventIdx, getGARTAddr(), gem5::GEM5_PACKED::intCtxId, gem5::GEM5_PACKED::intSelect, panic, gem5::ArmISA::q, and releaseMemDone().

Referenced by decodeHeader().

◆ releaseMemDone()

| void gem5::PM4PacketProcessor::releaseMemDone | ( | PM4Queue * | q, |

| PM4ReleaseMem * | pkt, | ||

| Addr | addr | ||

| ) |

Definition at line 502 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::CP_EOP, gem5::GEM5_PACKED::dataLo, decodeNext(), DPRINTF, gem5::AMDGPUDevice::getIH(), gpuDevice, gem5::GEM5_PACKED::intCtxId, gem5::GEM5_PACKED::intSelect, gem5::AMDGPUInterruptHandler::prepareInterruptCookie(), gem5::ArmISA::q, gem5::SOC15_IH_CLIENTID_GRBM_CP, and gem5::AMDGPUInterruptHandler::submitInterruptCookie().

Referenced by releaseMem().

◆ runList()

| void gem5::PM4PacketProcessor::runList | ( | PM4Queue * | q, |

| PM4RunList * | pkt | ||

| ) |

Definition at line 675 of file pm4_packet_processor.cc.

References decodeNext(), DPRINTF, gem5::GEM5_PACKED::ibBase, gem5::GEM5_PACKED::ibSize, and gem5::ArmISA::q.

Referenced by decodeHeader().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 1039 of file pm4_packet_processor.cc.

References gem5::X86ISA::base, gem5::ArmISA::i, gem5::PowerISA::me, gem5::ArmISA::offset, gem5::ArmISA::q, queues, gem5::ClockedObject::serialize(), SERIALIZE_ARRAY, and SERIALIZE_SCALAR.

◆ setGPUDevice()

| void gem5::PM4PacketProcessor::setGPUDevice | ( | AMDGPUDevice * | gpu_device | ) |

Definition at line 86 of file pm4_packet_processor.cc.

References gpuDevice.

Referenced by gem5::AMDGPUDevice::AMDGPUDevice().

◆ setHqdActive()

| void gem5::PM4PacketProcessor::setHqdActive | ( | uint32_t | data | ) |

Definition at line 882 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_active, and kiq.

Referenced by writeMMIO().

◆ setHqdIbCtrl()

| void gem5::PM4PacketProcessor::setHqdIbCtrl | ( | uint32_t | data | ) |

Definition at line 954 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_ib_control, and kiq.

Referenced by writeMMIO().

◆ setHqdPqBase()

| void gem5::PM4PacketProcessor::setHqdPqBase | ( | uint32_t | data | ) |

Definition at line 888 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_base_lo, and kiq.

Referenced by writeMMIO().

◆ setHqdPqBaseHi()

| void gem5::PM4PacketProcessor::setHqdPqBaseHi | ( | uint32_t | data | ) |

Definition at line 894 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_base_hi, and kiq.

Referenced by writeMMIO().

◆ setHqdPqControl()

| void gem5::PM4PacketProcessor::setHqdPqControl | ( | uint32_t | data | ) |

Definition at line 948 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_control, and kiq.

Referenced by writeMMIO().

◆ setHqdPqDoorbellCtrl()

| void gem5::PM4PacketProcessor::setHqdPqDoorbellCtrl | ( | uint32_t | data | ) |

Definition at line 900 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_doorbell_control, and kiq.

Referenced by writeMMIO().

◆ setHqdPqPtr()

| void gem5::PM4PacketProcessor::setHqdPqPtr | ( | uint32_t | data | ) |

Definition at line 906 of file pm4_packet_processor.cc.

References data, kiq, and gem5::GEM5_PACKED::rptr.

Referenced by writeMMIO().

◆ setHqdPqRptrReportAddr()

| void gem5::PM4PacketProcessor::setHqdPqRptrReportAddr | ( | uint32_t | data | ) |

Definition at line 924 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_rptr_report_addr_lo, and kiq.

Referenced by writeMMIO().

◆ setHqdPqRptrReportAddrHi()

| void gem5::PM4PacketProcessor::setHqdPqRptrReportAddrHi | ( | uint32_t | data | ) |

Definition at line 930 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_rptr_report_addr_hi, and kiq.

Referenced by writeMMIO().

◆ setHqdPqWptrHi()

| void gem5::PM4PacketProcessor::setHqdPqWptrHi | ( | uint32_t | data | ) |

Definition at line 918 of file pm4_packet_processor.cc.

Referenced by writeMMIO().

◆ setHqdPqWptrLo()

| void gem5::PM4PacketProcessor::setHqdPqWptrLo | ( | uint32_t | data | ) |

Definition at line 912 of file pm4_packet_processor.cc.

Referenced by writeMMIO().

◆ setHqdPqWptrPollAddr()

| void gem5::PM4PacketProcessor::setHqdPqWptrPollAddr | ( | uint32_t | data | ) |

Definition at line 936 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_wptr_poll_addr_lo, and kiq.

Referenced by writeMMIO().

◆ setHqdPqWptrPollAddrHi()

| void gem5::PM4PacketProcessor::setHqdPqWptrPollAddrHi | ( | uint32_t | data | ) |

Definition at line 942 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_wptr_poll_addr_hi, and kiq.

Referenced by writeMMIO().

◆ setHqdVmid()

| void gem5::PM4PacketProcessor::setHqdVmid | ( | uint32_t | data | ) |

Definition at line 876 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_vmid, and kiq.

Referenced by writeMMIO().

◆ setRbBaseHi()

| void gem5::PM4PacketProcessor::setRbBaseHi | ( | uint32_t | data | ) |

Definition at line 1014 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_base_hi, and pq.

Referenced by writeMMIO().

◆ setRbBaseLo()

| void gem5::PM4PacketProcessor::setRbBaseLo | ( | uint32_t | data | ) |

Definition at line 1008 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_base_lo, and pq.

Referenced by writeMMIO().

◆ setRbCntl()

| void gem5::PM4PacketProcessor::setRbCntl | ( | uint32_t | data | ) |

Definition at line 966 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_control, and pq.

Referenced by writeMMIO().

◆ setRbDoorbellCntrl()

| void gem5::PM4PacketProcessor::setRbDoorbellCntrl | ( | uint32_t | data | ) |

Definition at line 1020 of file pm4_packet_processor.cc.

References data, gem5::PrimaryQueue::doorbellOffset, gem5::GEM5_PACKED::hqd_pq_doorbell_control, and pq.

Referenced by writeMMIO().

◆ setRbDoorbellRangeHi()

| void gem5::PM4PacketProcessor::setRbDoorbellRangeHi | ( | uint32_t | data | ) |

Definition at line 1033 of file pm4_packet_processor.cc.

References data, gem5::PrimaryQueue::doorbellRangeHi, and pq.

Referenced by writeMMIO().

◆ setRbDoorbellRangeLo()

| void gem5::PM4PacketProcessor::setRbDoorbellRangeLo | ( | uint32_t | data | ) |

Definition at line 1027 of file pm4_packet_processor.cc.

References data, gem5::PrimaryQueue::doorbellRangeLo, and pq.

Referenced by writeMMIO().

◆ setRbRptrAddrHi()

| void gem5::PM4PacketProcessor::setRbRptrAddrHi | ( | uint32_t | data | ) |

Definition at line 990 of file pm4_packet_processor.cc.

References data, pq, and gem5::PrimaryQueue::queueRptrAddrHi.

Referenced by writeMMIO().

◆ setRbRptrAddrLo()

| void gem5::PM4PacketProcessor::setRbRptrAddrLo | ( | uint32_t | data | ) |

Definition at line 984 of file pm4_packet_processor.cc.

References data, pq, and gem5::PrimaryQueue::queueRptrAddrLo.

Referenced by writeMMIO().

◆ setRbVmid()

| void gem5::PM4PacketProcessor::setRbVmid | ( | uint32_t | data | ) |

Definition at line 960 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_vmid, and pq.

Referenced by writeMMIO().

◆ setRbWptrHi()

| void gem5::PM4PacketProcessor::setRbWptrHi | ( | uint32_t | data | ) |

Definition at line 978 of file pm4_packet_processor.cc.

References data, pq, and gem5::PrimaryQueue::queueWptrHi.

Referenced by writeMMIO().

◆ setRbWptrLo()

| void gem5::PM4PacketProcessor::setRbWptrLo | ( | uint32_t | data | ) |

Definition at line 972 of file pm4_packet_processor.cc.

References data, pq, and gem5::PrimaryQueue::queueWptrLo.

Referenced by writeMMIO().

◆ setRbWptrPollAddrHi()

| void gem5::PM4PacketProcessor::setRbWptrPollAddrHi | ( | uint32_t | data | ) |

Definition at line 1002 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_wptr_poll_addr_hi, and pq.

Referenced by writeMMIO().

◆ setRbWptrPollAddrLo()

| void gem5::PM4PacketProcessor::setRbWptrPollAddrLo | ( | uint32_t | data | ) |

Definition at line 996 of file pm4_packet_processor.cc.

References data, gem5::GEM5_PACKED::hqd_pq_wptr_poll_addr_lo, and pq.

Referenced by writeMMIO().

◆ setUconfigReg()

| void gem5::PM4PacketProcessor::setUconfigReg | ( | PM4Queue * | q, |

| PM4SetUconfigReg * | pkt | ||

| ) |

Definition at line 719 of file pm4_packet_processor.cc.

References gem5::GEM5_PACKED::data, decodeNext(), gpuDevice, gem5::GEM5_PACKED::offset, PACKET3_SET_UCONFIG_REG_START, gem5::ArmISA::q, and gem5::AMDGPUDevice::setRegVal().

Referenced by decodeHeader().

◆ switchBuffer()

| void gem5::PM4PacketProcessor::switchBuffer | ( | PM4Queue * | q, |

| PM4SwitchBuf * | pkt | ||

| ) |

Definition at line 707 of file pm4_packet_processor.cc.

References decodeNext(), DPRINTF, and gem5::ArmISA::q.

Referenced by decodeHeader().

◆ translate()

|

overridevirtual |

Method for functional translation.

AMDGPUDevice will perform DMA operations on VAs, and because page faults are not currently supported for Vega 10, we must be able to find the pages mapped for the process.

Implements gem5::DmaVirtDevice.

Definition at line 64 of file pm4_packet_processor.cc.

References gem5::AMDGPUDevice::getVM(), gpuDevice, gem5::AMDGPUVM::inAGP(), and gem5::MipsISA::vaddr.

◆ unmapQueues()

| void gem5::PM4PacketProcessor::unmapQueues | ( | PM4Queue * | q, |

| PM4UnmapQueues * | pkt | ||

| ) |

Definition at line 532 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::GEM5_PACKED::base, gem5::AMDGPUDevice::CP(), gem5::AMDGPUDevice::deallocateAllQueues(), gem5::AMDGPUDevice::deallocatePasid(), gem5::AMDGPUDevice::deallocateVmid(), decodeNext(), gem5::DmaVirtDevice::dmaWriteVirt(), doneMQDWrite(), gem5::GEM5_PACKED::doorbellOffset0, gem5::GEM5_PACKED::doorbellOffset1, gem5::GEM5_PACKED::doorbellOffset2, gem5::GEM5_PACKED::doorbellOffset3, DPRINTF, getGARTAddr(), gem5::AMDGPUDevice::getUsedVMIDs(), gem5::AMDGPUDevice::getVMID(), gpuDevice, gem5::GPUCommandProcessor::hsaPacketProc(), gem5::ArmISA::id, gem5::GEM5_PACKED::mqdReadIndex, gem5::GEM5_PACKED::numQueues, panic, gem5::GEM5_PACKED::pasid, gem5::ArmISA::q, queues, and gem5::GEM5_PACKED::queueSel.

Referenced by decodeHeader().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 1120 of file pm4_packet_processor.cc.

References gem5::X86ISA::base, gem5::GEM5_PACKED::base, DPRINTF, gem5::ArmISA::i, gem5::GEM5_PACKED::ibBase, gem5::GEM5_PACKED::ibRptr, gem5::PowerISA::me, gem5::GEM5_PACKED::mqdBase, newQueue(), gem5::ArmISA::offset, queues, gem5::GEM5_PACKED::rptr, gem5::ClockedObject::unserialize(), UNSERIALIZE_ARRAY, and UNSERIALIZE_SCALAR.

◆ updateReadIndex()

| void gem5::PM4PacketProcessor::updateReadIndex | ( | Addr | offset, |

| uint64_t | rd_idx | ||

| ) |

Update read index on doorbell rings.

We use write index, however read index == write index when the queue is empty. This allows us to save previous read index when a queue is remapped. The remapped queue will read from the previous read index rather than reset to zero.

Definition at line 525 of file pm4_packet_processor.cc.

References gem5::ArmISA::offset, and queuesMap.

Referenced by gem5::AMDGPUDevice::writeDoorbell().

◆ waitRegMem()

| void gem5::PM4PacketProcessor::waitRegMem | ( | PM4Queue * | q, |

| PM4WaitRegMem * | pkt | ||

| ) |

Definition at line 732 of file pm4_packet_processor.cc.

References decodeNext(), DPRINTF, gem5::GEM5_PACKED::function, gem5::GEM5_PACKED::mask, gem5::GEM5_PACKED::memAddrHi, gem5::GEM5_PACKED::memAddrLo, gem5::GEM5_PACKED::memSpace, gem5::GEM5_PACKED::operation, gem5::GEM5_PACKED::pollInterval, gem5::ArmISA::q, and gem5::GEM5_PACKED::reference.

Referenced by decodeHeader().

◆ write()

Inherited methods.

Implements gem5::PioDevice.

Definition at line 74 of file pm4_packet_processor.hh.

◆ writeData()

| void gem5::PM4PacketProcessor::writeData | ( | PM4Queue * | q, |

| PM4WriteData * | pkt | ||

| ) |

Definition at line 336 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::GEM5_PACKED::data, decodeNext(), gem5::GEM5_PACKED::destAddr, gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, getGARTAddr(), gem5::ArmISA::q, gem5::GEM5_PACKED::writeConfirm, and writeDataDone().

Referenced by decodeHeader().

◆ writeDataDone()

| void gem5::PM4PacketProcessor::writeDataDone | ( | PM4Queue * | q, |

| PM4WriteData * | pkt, | ||

| Addr | addr | ||

| ) |

Definition at line 354 of file pm4_packet_processor.cc.

References gem5::X86ISA::addr, gem5::GEM5_PACKED::data, decodeNext(), DPRINTF, gem5::ArmISA::q, and gem5::GEM5_PACKED::writeConfirm.

Referenced by writeData().

◆ writeMMIO()

Definition at line 782 of file pm4_packet_processor.cc.

References gem5::Compute, getKiqDoorbellOffset(), gem5::Packet::getLE(), getPqDoorbellOffset(), gem5::Gfx, gpuDevice, mmCP_HQD_ACTIVE, mmCP_HQD_IB_CONTROL, mmCP_HQD_PQ_BASE, mmCP_HQD_PQ_BASE_HI, mmCP_HQD_PQ_CONTROL, mmCP_HQD_PQ_DOORBELL_CONTROL, mmCP_HQD_PQ_RPTR, mmCP_HQD_PQ_RPTR_REPORT_ADDR, mmCP_HQD_PQ_RPTR_REPORT_ADDR_HI, mmCP_HQD_PQ_WPTR_HI, mmCP_HQD_PQ_WPTR_LO, mmCP_HQD_PQ_WPTR_POLL_ADDR, mmCP_HQD_PQ_WPTR_POLL_ADDR_HI, mmCP_HQD_VMID, mmCP_RB0_BASE, mmCP_RB0_BASE_HI, mmCP_RB0_CNTL, mmCP_RB0_RPTR_ADDR, mmCP_RB0_RPTR_ADDR_HI, mmCP_RB0_WPTR, mmCP_RB0_WPTR_HI, mmCP_RB_DOORBELL_CONTROL, mmCP_RB_DOORBELL_RANGE_LOWER, mmCP_RB_DOORBELL_RANGE_UPPER, mmCP_RB_VMID, mmCP_RB_WPTR_POLL_ADDR_HI, mmCP_RB_WPTR_POLL_ADDR_LO, gem5::AMDGPUDevice::setDoorbellType(), setHqdActive(), setHqdIbCtrl(), setHqdPqBase(), setHqdPqBaseHi(), setHqdPqControl(), setHqdPqDoorbellCtrl(), setHqdPqPtr(), setHqdPqRptrReportAddr(), setHqdPqRptrReportAddrHi(), setHqdPqWptrHi(), setHqdPqWptrLo(), setHqdPqWptrPollAddr(), setHqdPqWptrPollAddrHi(), setHqdVmid(), setRbBaseHi(), setRbBaseLo(), setRbCntl(), setRbDoorbellCntrl(), setRbDoorbellRangeHi(), setRbDoorbellRangeLo(), setRbRptrAddrHi(), setRbRptrAddrLo(), setRbVmid(), setRbWptrHi(), setRbWptrLo(), setRbWptrPollAddrHi(), and setRbWptrPollAddrLo().

Referenced by gem5::AMDGPUDevice::writeMMIO().

Member Data Documentation

◆ gpuDevice

|

private |

Definition at line 54 of file pm4_packet_processor.hh.

Referenced by decodeHeader(), getGARTAddr(), mapProcess(), mapQueues(), newQueue(), processMQD(), processSDMAMQD(), releaseMemDone(), setGPUDevice(), setUconfigReg(), translate(), unmapQueues(), and writeMMIO().

◆ kiq

|

private |

Definition at line 59 of file pm4_packet_processor.hh.

Referenced by getKiqDoorbellOffset(), mapKiq(), PM4PacketProcessor(), setHqdActive(), setHqdIbCtrl(), setHqdPqBase(), setHqdPqBaseHi(), setHqdPqControl(), setHqdPqDoorbellCtrl(), setHqdPqPtr(), setHqdPqRptrReportAddr(), setHqdPqRptrReportAddrHi(), setHqdPqWptrPollAddr(), setHqdPqWptrPollAddrHi(), and setHqdVmid().

◆ kiq_pkt

|

private |

Definition at line 60 of file pm4_packet_processor.hh.

Referenced by mapKiq().

◆ pq

|

private |

Definition at line 56 of file pm4_packet_processor.hh.

Referenced by getPqDoorbellOffset(), mapPq(), PM4PacketProcessor(), setRbBaseHi(), setRbBaseLo(), setRbCntl(), setRbDoorbellCntrl(), setRbDoorbellRangeHi(), setRbDoorbellRangeLo(), setRbRptrAddrHi(), setRbRptrAddrLo(), setRbVmid(), setRbWptrHi(), setRbWptrLo(), setRbWptrPollAddrHi(), and setRbWptrPollAddrLo().

◆ pq_pkt

|

private |

Definition at line 57 of file pm4_packet_processor.hh.

Referenced by mapPq().

◆ queues

|

private |

Definition at line 63 of file pm4_packet_processor.hh.

Referenced by newQueue(), serialize(), unmapQueues(), and unserialize().

◆ queuesMap

|

private |

Definition at line 65 of file pm4_packet_processor.hh.

Referenced by getQueue(), newQueue(), processMQD(), and updateReadIndex().

The documentation for this class was generated from the following files:

- dev/amdgpu/pm4_packet_processor.hh

- dev/amdgpu/pm4_packet_processor.cc