#include <faults.hh>

Public Member Functions | |

| FastInstructionAccessMMUMiss (Addr addr) | |

| FastInstructionAccessMMUMiss () | |

| void | invoke (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

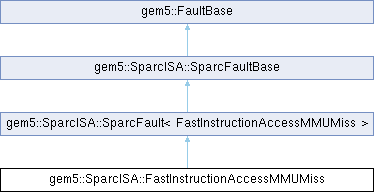

| Public Member Functions inherited from gem5::SparcISA::SparcFault< FastInstructionAccessMMUMiss > | |

| FaultName | name () const |

| TrapType | trapType () |

| FaultPriority | priority () |

| PrivilegeLevel | getNextLevel (PrivilegeLevel current) |

| Public Member Functions inherited from gem5::SparcISA::SparcFaultBase | |

| void | invoke (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

| Public Member Functions inherited from gem5::FaultBase | |

| virtual | ~FaultBase () |

Protected Attributes | |

| Addr | vaddr |

Detailed Description

Constructor & Destructor Documentation

◆ FastInstructionAccessMMUMiss() [1/2]

|

inline |

Definition at line 211 of file faults.hh.

References gem5::X86ISA::addr, and vaddr.

◆ FastInstructionAccessMMUMiss() [2/2]

|

inline |

Member Function Documentation

◆ invoke()

|

virtual |

Reimplemented from gem5::FaultBase.

Definition at line 621 of file faults.cc.

References gem5::bits(), gem5::EmulationPageTable::Entry::flags, gem5::FullSystem, gem5::ThreadContext::getMMUPtr(), gem5::ThreadContext::getProcessPtr(), gem5::SparcISA::MMU::insertItlbEntry(), gem5::SparcISA::SparcFaultBase::invoke(), gem5::SparcISA::MISCREG_TLB_DATA, gem5::MipsISA::p, gem5::EmulationPageTable::Entry::paddr, panic_if, gem5::SparcISA::TlbEntry::pte, gem5::ThreadContext::readMiscRegNoEffect(), gem5::EmulationPageTable::ReadOnly, gem5::EmulationPageTable::Uncacheable, and vaddr.

Member Data Documentation

◆ vaddr

|

protected |

Definition at line 209 of file faults.hh.

Referenced by FastInstructionAccessMMUMiss(), FastInstructionAccessMMUMiss(), and invoke().

The documentation for this class was generated from the following files:

Generated on Mon Oct 27 2025 04:13:23 for gem5 by doxygen 1.14.0