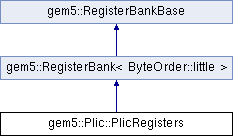

MMIO Registers. More...

Public Member Functions | |

| PlicRegisters (const std::string &name, Addr base, Plic *plic) | |

| void | init () |

| Public Member Functions inherited from gem5::RegisterBank< ByteOrder::little > | |

| void | setDebugFlag (const ::gem5::debug::SimpleFlag &flag) |

| constexpr | RegisterBank (const std::string &new_name, Addr new_base) |

| virtual | ~RegisterBank () |

| RegisterBank (RegisterBank &&)=default | |

| void | addRegisters (std::initializer_list< RegisterAdder > adders) |

| void | addRegistersAt (std::initializer_list< RegisterAdder > adders) |

| void | addRegister (RegisterAdder reg) |

| Addr | base () const |

| Addr | size () const |

| const std::string & | name () const |

| virtual void | read (Addr addr, void *buf, Addr bytes) |

| virtual void | write (Addr addr, const void *buf, Addr bytes) |

| virtual void | reset () |

Public Attributes | |

| const Addr | pendingStart = 0x1000 |

| const Addr | enableStart = 0x2000 |

| const Addr | thresholdStart = 0x0200000 |

| const Addr | enablePadding = 0x80 |

| const Addr | thresholdPadding = 0x1000 |

| const Addr | maxBankSize = 0x4000000 |

| std::vector< Register32 > | priority |

| std::vector< Register32 > | pending |

| std::vector< std::vector< Register32 > > | enable |

| std::vector< Register32 > | threshold |

| std::vector< Register32 > | claim |

| std::vector< RegisterRaz > | enable_holes |

| std::vector< RegisterRaz > | claim_holes |

| std::vector< RegisterRaz > | reserved |

| Plic * | plic |

Additional Inherited Members | |

| Public Types inherited from gem5::RegisterBank< ByteOrder::little > | |

| using | Register8 |

| using | Register8LE |

| using | Register8BE |

| using | Register16 |

| using | Register16LE |

| using | Register16BE |

| using | Register32 |

| using | Register32LE |

| using | Register32BE |

| using | Register64 |

| using | Register64LE |

| using | Register64BE |

| Static Public Member Functions inherited from gem5::RegisterBank< ByteOrder::little > | |

| static constexpr Data | readWithMask (const Data &value, const Data &bitmask) |

| static constexpr Data | writeWithMask (const Data &old, const Data &value, const Data &bitmask) |

Detailed Description

MMIO Registers.

Priority (0-7):

- memory map: 0x0000000 - 0x0000FFC (1024 sources, 32 bits each)

- gem5: vector<uint32_t> (index: source_id, size: n_src)

... reserved[0]

Pending:

- memory map: 0x0001000 - 0x0001080 (1024 sources, 1 bit each)

- gem5: vector<bitset<32>> (index: addr_offset, size: ceil(n_src/32))

... reserved[1]

Enable:

- memory map: 0x0002000 - 0x01F2000 (15872 contexts, 1024 sources, 1 bit each)

- gem5: vector<vector<bitset<32>>> (index: [context_id addr_offset], size: [n_context, ceil(n_src/32)]) ... reserved[2]

Threshold:

- memory map: 0x0200000 - 0x3FFFFFC (15872 contexts, 32-bit each, 0x1000 byte spacing)

- gem5: vector<uint32_t> (index: context_id, size: n_context)

Claim / Complete:

- memory map: 0x0200004 - 0x3FFFFFC (15872 contexts, 32-bit each, 0x1000 byte spacing)

- gem5: getter / setter functions

... reserved[3]

Constructor & Destructor Documentation

◆ PlicRegisters()

|

inline |

Definition at line 217 of file plic.hh.

References gem5::RegisterBank< ByteOrder::little >::base(), gem5::RegisterBank< ByteOrder::little >::name(), gem5::Plic::Plic(), and plic.

Member Function Documentation

◆ init()

| void gem5::Plic::PlicRegisters::init | ( | ) |

Definition at line 204 of file plic.cc.

References gem5::RegisterBank< ByteOrder::little >::addRegister(), claim, claim_holes, enable, enable_holes, enablePadding, enableStart, gem5::ArmISA::i, maxBankSize, pending, pendingStart, plic, priority, gem5::Plic::readClaim(), reserved, threshold, thresholdPadding, thresholdStart, gem5::Plic::writeClaim(), gem5::Plic::writeEnable(), gem5::Plic::writePriority(), and gem5::Plic::writeThreshold().

Member Data Documentation

◆ claim

| std::vector<Register32> gem5::Plic::PlicRegisters::claim |

◆ claim_holes

| std::vector<RegisterRaz> gem5::Plic::PlicRegisters::claim_holes |

◆ enable

| std::vector<std::vector<Register32> > gem5::Plic::PlicRegisters::enable |

◆ enable_holes

| std::vector<RegisterRaz> gem5::Plic::PlicRegisters::enable_holes |

◆ enablePadding

| const Addr gem5::Plic::PlicRegisters::enablePadding = 0x80 |

◆ enableStart

| const Addr gem5::Plic::PlicRegisters::enableStart = 0x2000 |

◆ maxBankSize

| const Addr gem5::Plic::PlicRegisters::maxBankSize = 0x4000000 |

◆ pending

| std::vector<Register32> gem5::Plic::PlicRegisters::pending |

◆ pendingStart

| const Addr gem5::Plic::PlicRegisters::pendingStart = 0x1000 |

◆ plic

| Plic* gem5::Plic::PlicRegisters::plic |

Definition at line 221 of file plic.hh.

Referenced by init(), and PlicRegisters().

◆ priority

| std::vector<Register32> gem5::Plic::PlicRegisters::priority |

◆ reserved

| std::vector<RegisterRaz> gem5::Plic::PlicRegisters::reserved |

◆ threshold

| std::vector<Register32> gem5::Plic::PlicRegisters::threshold |

◆ thresholdPadding

| const Addr gem5::Plic::PlicRegisters::thresholdPadding = 0x1000 |

◆ thresholdStart

| const Addr gem5::Plic::PlicRegisters::thresholdStart = 0x0200000 |

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:53 for gem5 by doxygen 1.14.0