#include <tarmac_parser.hh>

Classes | |

| struct | ParserInstEntry |

| struct | ParserMemEntry |

| struct | ParserRegEntry |

| struct | TarmacParserRecordEvent |

| Event triggered to check the value of the destination registers. More... | |

Public Member Functions | |

| TarmacParserRecord (Tick _when, ThreadContext *_thread, const StaticInstPtr _staticInst, ArmISA::PCState _pc, TarmacParser &_parent, const StaticInstPtr _macroStaticInst=NULL) | |

| void | dump () override |

| bool | readMemNoEffect (Addr addr, uint8_t *data, unsigned size, unsigned flags) |

| Performs a memory access to read the value written by a previous write. More... | |

Public Member Functions inherited from gem5::Trace::TarmacBaseRecord Public Member Functions inherited from gem5::Trace::TarmacBaseRecord | |

| TarmacBaseRecord (Tick _when, ThreadContext *_thread, const StaticInstPtr _staticInst, ArmISA::PCState _pc, const StaticInstPtr _macroStaticInst=NULL) | |

Public Member Functions inherited from gem5::Trace::InstRecord Public Member Functions inherited from gem5::Trace::InstRecord | |

| InstRecord (Tick _when, ThreadContext *_thread, const StaticInstPtr _staticInst, TheISA::PCState _pc, const StaticInstPtr _macroStaticInst=NULL) | |

| virtual | ~InstRecord () |

| void | setWhen (Tick new_when) |

| void | setMem (Addr a, Addr s, unsigned f) |

| template<typename T , size_t N> | |

| void | setData (std::array< T, N > d) |

| void | setData (uint64_t d) |

| void | setData (uint32_t d) |

| void | setData (uint16_t d) |

| void | setData (uint8_t d) |

| void | setData (int64_t d) |

| void | setData (int32_t d) |

| void | setData (int16_t d) |

| void | setData (int8_t d) |

| void | setData (double d) |

| void | setData (TheISA::VecRegContainer &d) |

| void | setData (TheISA::VecPredRegContainer &d) |

| void | setFetchSeq (InstSeqNum seq) |

| void | setCPSeq (InstSeqNum seq) |

| void | setPredicate (bool val) |

| void | setFaulting (bool val) |

| Tick | getWhen () const |

| ThreadContext * | getThread () const |

| StaticInstPtr | getStaticInst () const |

| TheISA::PCState | getPCState () const |

| StaticInstPtr | getMacroStaticInst () const |

| Addr | getAddr () const |

| Addr | getSize () const |

| unsigned | getFlags () const |

| bool | getMemValid () const |

| uint64_t | getIntData () const |

| double | getFloatData () const |

| int | getDataStatus () const |

| InstSeqNum | getFetchSeq () const |

| bool | getFetchSeqValid () const |

| InstSeqNum | getCpSeq () const |

| bool | getCpSeqValid () const |

| bool | getFaulting () const |

Static Public Member Functions | |

| static void | printMismatchHeader (const StaticInstPtr inst, ArmISA::PCState pc) |

| Print a mismatch header containing the instruction fields as reported by gem5. More... | |

Static Public Member Functions inherited from gem5::Trace::TarmacBaseRecord Static Public Member Functions inherited from gem5::Trace::TarmacBaseRecord | |

| static ISetState | pcToISetState (ArmISA::PCState pc) |

| Returns the Instruction Set State according to the current PCState. More... | |

Static Public Attributes | |

| static const int | MaxLineLength = 256 |

Protected Attributes | |

| TarmacParser & | parent |

Protected Attributes inherited from gem5::Trace::InstRecord Protected Attributes inherited from gem5::Trace::InstRecord | |

| Tick | when |

| ThreadContext * | thread |

| StaticInstPtr | staticInst |

| TheISA::PCState | pc |

| StaticInstPtr | macroStaticInst |

| Addr | addr |

| The address that was accessed. More... | |

| Addr | size |

| The size of the memory request. More... | |

| unsigned | flags |

| The flags that were assigned to the request. More... | |

| union { | |

| uint64_t as_int | |

| double as_double | |

| TheISA::VecRegContainer * as_vec | |

| TheISA::VecPredRegContainer * as_pred | |

| } | data |

| InstSeqNum | fetch_seq |

| InstSeqNum | cp_seq |

| enum gem5::Trace::InstRecord::DataStatus | data_status |

| bool | mem_valid |

| bool | fetch_seq_valid |

| bool | cp_seq_valid |

| bool | predicate |

| is the predicate for execution this inst true or false (not execed)? More... | |

| bool | faulting |

| Did the execution of this instruction fault? (requires ExecFaulting to be enabled) More... | |

Private Types | |

| using | MiscRegMap = std::unordered_map< std::string, RegIndex > |

| Map from misc. More... | |

Private Member Functions | |

| bool | advanceTrace () |

| Advances the TARMAC trace up to the next instruction, register, or memory access record. More... | |

| const char * | iSetStateToStr (ISetState isetstate) const |

| Returns the string representation of an instruction set state. More... | |

Private Attributes | |

| bool | parsingStarted |

| True if a TARMAC instruction record has already been parsed for this instruction. More... | |

| bool | mismatch |

| True if a mismatch has been detected for this instruction. More... | |

| bool | mismatchOnPcOrOpcode |

| True if a mismatch has been detected for this instruction on PC or opcode. More... | |

| RequestPtr | memReq |

| Request for memory write checks. More... | |

Static Private Attributes | |

| static ParserInstEntry | instRecord |

| Buffer for instruction trace records. More... | |

| static ParserRegEntry | regRecord |

| Buffer for register trace records. More... | |

| static ParserMemEntry | memRecord |

| Buffer for memory access trace records (stores only). More... | |

| static TarmacRecordType | currRecordType |

| Type of last parsed record. More... | |

| static char | buf [MaxLineLength] |

| Buffer used for trace file parsing. More... | |

| static std::list< ParserRegEntry > | destRegRecords |

| List of records of destination registers. More... | |

| static MiscRegMap | miscRegMap |

| static int8_t | maxVectorLength = 0 |

| Max. More... | |

Additional Inherited Members | |

Public Types inherited from gem5::Trace::TarmacBaseRecord Public Types inherited from gem5::Trace::TarmacBaseRecord | |

| enum | TarmacRecordType { TARMAC_INST, TARMAC_REG, TARMAC_MEM, TARMAC_UNSUPPORTED } |

| TARMAC trace record type. More... | |

| enum | ISetState { ISET_ARM, ISET_THUMB, ISET_A64, ISET_UNSUPPORTED } |

| ARM instruction set state. More... | |

| enum | RegType { REG_R, REG_X, REG_S, REG_D, REG_P, REG_Q, REG_Z, REG_MISC } |

| ARM register type. More... | |

Protected Types inherited from gem5::Trace::InstRecord Protected Types inherited from gem5::Trace::InstRecord | |

| enum | DataStatus { DataInvalid = 0, DataInt8 = 1, DataInt16 = 2, DataInt32 = 4, DataInt64 = 8, DataDouble = 3, DataVec = 5, DataVecPred = 6 } |

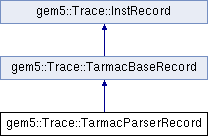

Detailed Description

Definition at line 66 of file tarmac_parser.hh.

Member Typedef Documentation

◆ MiscRegMap

|

private |

Constructor & Destructor Documentation

◆ TarmacParserRecord()

| gem5::Trace::TarmacParserRecord::TarmacParserRecord | ( | Tick | _when, |

| ThreadContext * | _thread, | ||

| const StaticInstPtr | _staticInst, | ||

| ArmISA::PCState | _pc, | ||

| TarmacParser & | _parent, | ||

| const StaticInstPtr | _macroStaticInst = NULL |

||

| ) |

Definition at line 962 of file tarmac_parser.cc.

References maxVectorLength, and memReq.

Member Function Documentation

◆ advanceTrace()

|

private |

Advances the TARMAC trace up to the next instruction, register, or memory access record.

The collected data is stored in one of {inst/reg/mem}_record.

- Returns

- False if EOF is reached.

Definition at line 1086 of file tarmac_parser.cc.

References gem5::Trace::TarmacBaseRecord::InstEntry::addr, buf, gem5::ArmISA::c, gem5::Trace::TarmacParser::cpuId, currRecordType, gem5::Trace::InstRecord::data, gem5::ArmISA::i, gem5::Trace::TarmacBaseRecord::RegEntry::index, instRecord, gem5::ArmISA::INTREG_ABT(), gem5::ArmISA::INTREG_FIQ(), gem5::ArmISA::INTREG_HYP(), gem5::ArmISA::INTREG_IRQ(), gem5::ArmISA::INTREG_MON(), gem5::ArmISA::INTREG_SVC(), gem5::ArmISA::INTREG_UND(), gem5::ArmISA::INTREG_USR(), gem5::Trace::TarmacBaseRecord::ISET_A64, gem5::Trace::TarmacBaseRecord::ISET_ARM, gem5::Trace::TarmacBaseRecord::ISET_THUMB, gem5::Trace::TarmacBaseRecord::ISET_UNSUPPORTED, gem5::Trace::TarmacBaseRecord::InstEntry::isetstate, gem5::ArmISA::lo, MaxLineLength, maxVectorLength, memRecord, gem5::Trace::TarmacParser::memWrCheck, miscRegMap, gem5::Trace::TarmacBaseRecord::InstEntry::opcode, parent, parsingStarted, gem5::Trace::TarmacBaseRecord::REG_D, gem5::Trace::TarmacBaseRecord::REG_MISC, gem5::Trace::TarmacBaseRecord::REG_P, gem5::Trace::TarmacBaseRecord::REG_Q, gem5::Trace::TarmacBaseRecord::REG_R, gem5::Trace::TarmacBaseRecord::REG_S, gem5::Trace::TarmacBaseRecord::REG_X, gem5::Trace::TarmacBaseRecord::REG_Z, regRecord, gem5::Trace::TarmacParserRecord::ParserRegEntry::repr, gem5::Trace::TarmacParserRecord::ParserInstEntry::seq_num, gem5::Trace::TarmacBaseRecord::InstEntry::taken, gem5::Trace::TarmacBaseRecord::TARMAC_INST, gem5::Trace::TarmacBaseRecord::TARMAC_MEM, gem5::Trace::TarmacBaseRecord::TARMAC_REG, gem5::Trace::TarmacBaseRecord::TARMAC_UNSUPPORTED, gem5::Trace::TarmacParser::trace, gem5::Trace::TarmacBaseRecord::RegEntry::type, gem5::ArmISA::v, gem5::Trace::TarmacBaseRecord::RegEntry::values, and warn.

Referenced by dump().

◆ dump()

|

overridevirtual |

Implements gem5::Trace::TarmacBaseRecord.

Definition at line 979 of file tarmac_parser.cc.

References gem5::Trace::TarmacBaseRecord::InstEntry::addr, advanceTrace(), gem5::ArmISA::TLB::AllowUnaligned, currRecordType, gem5::curTick(), destRegRecords, gem5::MipsISA::event, gem5::Trace::TarmacParser::exitOnDiff, gem5::Trace::TarmacParser::exitOnInsnDiff, gem5::exitSimLoop(), gem5::RefCountingPtr< T >::get(), instRecord, gem5::Trace::TarmacBaseRecord::ISET_UNSUPPORTED, gem5::Trace::TarmacBaseRecord::InstEntry::isetstate, iSetStateToStr(), gem5::StaticInst::isLastMicroop(), gem5::StaticInst::isMicroop(), gem5::Trace::TarmacParser::macroopInProgress, gem5::mainEventQueue, memRecord, mismatch, mismatchOnPcOrOpcode, gem5::Trace::TarmacBaseRecord::InstEntry::opcode, gem5::Trace::output(), panic, parent, parsingStarted, gem5::Trace::InstRecord::pc, gem5::Trace::TarmacBaseRecord::pcToISetState(), printMismatchHeader(), readMemNoEffect(), regRecord, gem5::Trace::InstRecord::staticInst, gem5::Trace::TarmacBaseRecord::TARMAC_INST, gem5::Trace::TarmacBaseRecord::TARMAC_MEM, gem5::Trace::TarmacBaseRecord::TARMAC_REG, gem5::Trace::TarmacBaseRecord::TARMAC_UNSUPPORTED, and gem5::Trace::InstRecord::thread.

◆ iSetStateToStr()

|

private |

Returns the string representation of an instruction set state.

Definition at line 1357 of file tarmac_parser.cc.

References gem5::Trace::TarmacBaseRecord::ISET_A64, gem5::Trace::TarmacBaseRecord::ISET_ARM, and gem5::Trace::TarmacBaseRecord::ISET_THUMB.

Referenced by dump().

◆ printMismatchHeader()

|

static |

Print a mismatch header containing the instruction fields as reported by gem5.

Definition at line 949 of file tarmac_parser.cc.

References gem5::curTick(), gem5::StaticInst::disassemble(), gem5::StaticInst::getEMI(), gem5::Trace::output(), and gem5::MipsISA::pc.

Referenced by dump().

◆ readMemNoEffect()

| bool gem5::Trace::TarmacParserRecord::readMemNoEffect | ( | Addr | addr, |

| uint8_t * | data, | ||

| unsigned | size, | ||

| unsigned | flags | ||

| ) |

Performs a memory access to read the value written by a previous write.

- Returns

- False if the result of the memory access should be ignored (faulty memory access, etc.).

Definition at line 1289 of file tarmac_parser.cc.

References gem5::Trace::InstRecord::addr, gem5::AddrRange::contains(), gem5::Trace::InstRecord::data, gem5::Trace::InstRecord::flags, gem5::Request::funcRequestorId, gem5::ThreadContext::getMMUPtr(), gem5::ThreadContext::getVirtProxy(), gem5::Trace::TarmacParser::ignoredAddrRange, memReq, gem5::Request::NO_ACCESS, gem5::NoFault, parent, gem5::ThreadContext::pcState(), gem5::BaseMMU::Read, gem5::PortProxy::readBlob(), gem5::Trace::InstRecord::size, gem5::Trace::InstRecord::thread, and gem5::ArmISA::MMU::translateAtomic().

Referenced by dump().

Member Data Documentation

◆ buf

|

staticprivate |

Buffer used for trace file parsing.

Definition at line 175 of file tarmac_parser.hh.

Referenced by advanceTrace().

◆ currRecordType

|

staticprivate |

Type of last parsed record.

Definition at line 172 of file tarmac_parser.hh.

Referenced by advanceTrace(), and dump().

◆ destRegRecords

|

staticprivate |

List of records of destination registers.

Definition at line 178 of file tarmac_parser.hh.

Referenced by dump().

◆ instRecord

|

staticprivate |

Buffer for instruction trace records.

Definition at line 163 of file tarmac_parser.hh.

Referenced by advanceTrace(), and dump().

◆ MaxLineLength

|

static |

Definition at line 126 of file tarmac_parser.hh.

Referenced by advanceTrace(), and gem5::Trace::TarmacParser::advanceTraceToStartPc().

◆ maxVectorLength

|

staticprivate |

Max.

vector length (SVE).

Definition at line 203 of file tarmac_parser.hh.

Referenced by advanceTrace(), and TarmacParserRecord().

◆ memRecord

|

staticprivate |

Buffer for memory access trace records (stores only).

Definition at line 169 of file tarmac_parser.hh.

Referenced by advanceTrace(), and dump().

◆ memReq

|

private |

Request for memory write checks.

Definition at line 200 of file tarmac_parser.hh.

Referenced by readMemNoEffect(), and TarmacParserRecord().

◆ miscRegMap

|

staticprivate |

Definition at line 182 of file tarmac_parser.hh.

Referenced by advanceTrace().

◆ mismatch

|

private |

True if a mismatch has been detected for this instruction.

Definition at line 191 of file tarmac_parser.hh.

Referenced by dump().

◆ mismatchOnPcOrOpcode

|

private |

True if a mismatch has been detected for this instruction on PC or opcode.

Definition at line 197 of file tarmac_parser.hh.

Referenced by dump().

◆ parent

|

protected |

Definition at line 206 of file tarmac_parser.hh.

Referenced by advanceTrace(), dump(), and readMemNoEffect().

◆ parsingStarted

|

private |

True if a TARMAC instruction record has already been parsed for this instruction.

Definition at line 188 of file tarmac_parser.hh.

Referenced by advanceTrace(), and dump().

◆ regRecord

|

staticprivate |

Buffer for register trace records.

Definition at line 166 of file tarmac_parser.hh.

Referenced by advanceTrace(), and dump().

The documentation for this class was generated from the following files:

- arch/arm/tracers/tarmac_parser.hh

- arch/arm/tracers/tarmac_parser.cc