#include <evs.hh>

Classes | |

| struct | CorePins |

Public Member Functions | |

| ScxEvsCortexR52 (const Params &p) | |

| ScxEvsCortexR52 (const sc_core::sc_module_name &mod_name, const Params &p) | |

| void | raiseInterruptPin (int num) |

| void | lowerInterruptPin (int num) |

| Port & | gem5_getPort (const std::string &if_name, int idx) override |

| void | end_of_elaboration () override |

| void | start_of_simulation () override |

| void | sendFunc (PacketPtr pkt) override |

| void | setClkPeriod (Tick clk_period) override |

| void | setSysCounterFrq (uint64_t sys_counter_frq) override |

| void | setCluster (SimObject *cluster) override |

Private Types | |

| using | Base = typename Types::Base |

| using | Params = typename Types::Params |

| using | Evs = ScxEvsCortexR52< Types > |

| using | ClstrInt = IntSinkPin< ScxEvsCortexR52 > |

Private Member Functions | |

| SC_HAS_PROCESS (ScxEvsCortexR52) | |

Private Attributes | |

| ClockRateControlInitiatorSocket | clockRateControl |

| SignalInterruptInitiatorSocket | signalInterrupt |

| std::vector< std::unique_ptr< CorePins > > | corePins |

| std::vector< std::unique_ptr< ClstrInt > > | spis |

| CortexR52Cluster * | gem5CpuCluster |

| const Params & | params |

Static Private Attributes | |

| static const int | CoreCount = Types::CoreCount |

| static const int | PpiCount = 9 |

| static const int | SpiCount = 960 |

Detailed Description

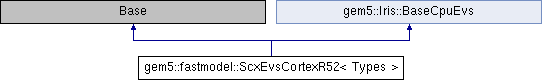

template<class Types>

class gem5::fastmodel::ScxEvsCortexR52< Types >

Member Typedef Documentation

◆ Base

|

private |

◆ ClstrInt

|

private |

◆ Evs

|

private |

◆ Params

|

private |

Constructor & Destructor Documentation

◆ ScxEvsCortexR52() [1/2]

|

inline |

◆ ScxEvsCortexR52() [2/2]

| gem5::fastmodel::ScxEvsCortexR52< Types >::ScxEvsCortexR52 | ( | const sc_core::sc_module_name & | mod_name, |

| const Params & | p | ||

| ) |

Definition at line 81 of file evs.cc.

References tlm::tlm_base_initiator_socket< BUSWIDTH, FW_IF, BW_IF, N, POL >::bind(), gem5::fastmodel::ScxEvsCortexR52< Types >::clockRateControl, gem5::fastmodel::ScxEvsCortexR52< Types >::CoreCount, gem5::fastmodel::ScxEvsCortexR52< Types >::corePins, gem5::csprintf(), gem5::ArmISA::i, name(), gem5::fastmodel::ScxEvsCortexR52< Types >::signalInterrupt, gem5::fastmodel::ScxEvsCortexR52< Types >::SpiCount, and gem5::fastmodel::ScxEvsCortexR52< Types >::spis.

Member Function Documentation

◆ end_of_elaboration()

|

inlineoverride |

◆ gem5_getPort()

|

override |

Definition at line 110 of file evs.cc.

References gem5::ArmISA::a, and panic.

◆ lowerInterruptPin()

|

inline |

◆ raiseInterruptPin()

|

inline |

◆ SC_HAS_PROCESS()

|

private |

◆ sendFunc()

|

overridevirtual |

Implements gem5::Iris::BaseCpuEvs.

Definition at line 100 of file evs.cc.

References sc_gem5::packet2payload(), and panic_if.

◆ setClkPeriod()

|

overridevirtual |

Implements gem5::Iris::BaseCpuEvs.

Definition at line 45 of file evs.cc.

References gem5::sim_clock::as_int::s.

◆ setCluster()

|

overridevirtual |

◆ setSysCounterFrq()

|

overridevirtual |

◆ start_of_simulation()

|

inlineoverride |

Member Data Documentation

◆ clockRateControl

|

private |

Definition at line 74 of file evs.hh.

Referenced by gem5::fastmodel::ScxEvsCortexR52< Types >::ScxEvsCortexR52().

◆ CoreCount

|

staticprivate |

Definition at line 65 of file evs.hh.

Referenced by gem5::fastmodel::ScxEvsCortexR52< Types >::ScxEvsCortexR52().

◆ corePins

|

private |

Definition at line 107 of file evs.hh.

Referenced by gem5::fastmodel::ScxEvsCortexR52< Types >::ScxEvsCortexR52().

◆ gem5CpuCluster

|

private |

◆ params

|

private |

◆ PpiCount

|

staticprivate |

Definition at line 66 of file evs.hh.

Referenced by gem5::fastmodel::ScxEvsCortexR52< Types >::CorePins::CorePins().

◆ signalInterrupt

|

private |

Definition at line 75 of file evs.hh.

Referenced by gem5::fastmodel::ScxEvsCortexR52< Types >::CorePins::lowerInterruptPin(), gem5::fastmodel::ScxEvsCortexR52< Types >::CorePins::raiseInterruptPin(), and gem5::fastmodel::ScxEvsCortexR52< Types >::ScxEvsCortexR52().

◆ SpiCount

|

staticprivate |

Definition at line 67 of file evs.hh.

Referenced by gem5::fastmodel::ScxEvsCortexR52< Types >::ScxEvsCortexR52().

◆ spis

|

private |

Definition at line 111 of file evs.hh.

Referenced by gem5::fastmodel::ScxEvsCortexR52< Types >::ScxEvsCortexR52().

The documentation for this class was generated from the following files: