Specific non-templated derived class used for SimObject configuration. More...

#include <dummy_checker.hh>

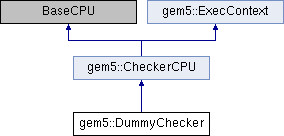

Inheritance diagram for gem5::DummyChecker:

Public Member Functions | |

| DummyChecker (const Params &p) | |

Public Member Functions inherited from gem5::CheckerCPU Public Member Functions inherited from gem5::CheckerCPU | |

| void | init () override |

| PARAMS (CheckerCPU) | |

| CheckerCPU (const Params &p) | |

| virtual | ~CheckerCPU () |

| void | setSystem (System *system) |

| void | setIcachePort (RequestPort *icache_port) |

| void | setDcachePort (RequestPort *dcache_port) |

| Port & | getDataPort () override |

| Port & | getInstPort () override |

| BaseMMU * | getMMUPtr () |

| virtual Counter | totalInsts () const override |

| virtual Counter | totalOps () const override |

| void | serialize (CheckpointOut &cp) const override |

| void | unserialize (CheckpointIn &cp) override |

| RegVal | getRegOperand (const StaticInst *si, int idx) override |

| void | getRegOperand (const StaticInst *si, int idx, void *val) override |

| void * | getWritableRegOperand (const StaticInst *si, int idx) override |

| void | setRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setRegOperand (const StaticInst *si, int idx, const void *val) override |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| Fault | initiateMemMgmtCmd (Request::Flags flags) override |

| Initiate a memory management command with no valid address. More... | |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| const PCStateBase & | pcState () const override |

| void | pcState (const PCStateBase &val) override |

| RegVal | readMiscRegNoEffect (int misc_reg) const |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a miscellaneous register, handling any architectural side effects due to reading that register. More... | |

| void | setMiscRegNoEffect (int misc_reg, RegVal val) |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a miscellaneous register, handling any architectural side effects due to writing that register. More... | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | recordPCChange (const PCStateBase &val) |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. More... | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| RequestPtr | genMemFragmentRequest (Addr frag_addr, int size, Request::Flags flags, const std::vector< bool > &byte_enable, int &frag_size, int &size_left) const |

| Helper function used to generate the request for a single fragment of a memory access. More... | |

| Fault | readMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable) override |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable) override |

| Fault | amoMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. More... | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. More... | |

| void | wakeup (ThreadID tid) override |

| void | handleError () |

| bool | checkFlags (const RequestPtr &unverified_req, Addr vAddr, Addr pAddr, int flags) |

| Checks if the flags set by the Checker and Checkee match. More... | |

| void | dumpAndExit () |

| ThreadContext * | tcBase () const override |

| Returns a pointer to the ThreadContext. More... | |

| SimpleThread * | threadBase () |

Public Member Functions inherited from gem5::ExecContext Public Member Functions inherited from gem5::ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Perform an atomic memory read operation. More... | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Initiate a timing memory read operation. More... | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable)=0 |

| For atomic-mode contexts, perform an atomic memory write operation. More... | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More... | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More... | |

Additional Inherited Members | |

Public Attributes inherited from gem5::CheckerCPU Public Attributes inherited from gem5::CheckerCPU | |

| SimpleThread * | thread |

| Counter | numLoad |

| Counter | startNumLoad |

| InstResult | unverifiedResult |

| RequestPtr | unverifiedReq |

| uint8_t * | unverifiedMemData |

| bool | changedPC |

| bool | willChangePC |

| std::unique_ptr< PCStateBase > | newPCState |

| bool | exitOnError |

| bool | updateOnError |

| bool | warnOnlyOnLoadError |

| InstSeqNum | youngestSN |

Protected Attributes inherited from gem5::CheckerCPU Protected Attributes inherited from gem5::CheckerCPU | |

| RequestorID | requestorId |

| id attached to all issued requests More... | |

| std::vector< Process * > | workload |

| System * | systemPtr |

| RequestPort * | icachePort |

| RequestPort * | dcachePort |

| ThreadContext * | tc |

| BaseMMU * | mmu |

| std::queue< InstResult > | result |

| StaticInstPtr | curStaticInst |

| StaticInstPtr | curMacroStaticInst |

| Counter | numInst |

| Counter | startNumInst |

| std::queue< int > | miscRegIdxs |

Detailed Description

Specific non-templated derived class used for SimObject configuration.

Definition at line 50 of file dummy_checker.hh.

Constructor & Destructor Documentation

◆ DummyChecker()

|

inline |

Definition at line 53 of file dummy_checker.hh.

References fatal_if, and gem5::VegaISA::p.

The documentation for this class was generated from the following file:

- cpu/dummy_checker.hh