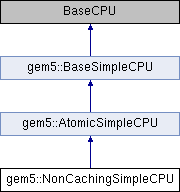

The NonCachingSimpleCPU is an AtomicSimpleCPU using the 'atomic_noncaching' memory mode instead of just 'atomic'. More...

#include <noncaching.hh>

Public Member Functions | |

| NonCachingSimpleCPU (const BaseNonCachingSimpleCPUParams &p) | |

| void | verifyMemoryMode () const override |

Public Member Functions inherited from gem5::AtomicSimpleCPU Public Member Functions inherited from gem5::AtomicSimpleCPU | |

| AtomicSimpleCPU (const BaseAtomicSimpleCPUParams ¶ms) | |

| virtual | ~AtomicSimpleCPU () |

| void | init () override |

| DrainState | drain () override |

| void | drainResume () override |

| void | switchOut () override |

| void | takeOverFrom (BaseCPU *old_cpu) override |

| void | verifyMemoryMode () const override |

| void | activateContext (ThreadID thread_num) override |

| void | suspendContext (ThreadID thread_num) override |

| bool | genMemFragmentRequest (const RequestPtr &req, Addr frag_addr, int size, Request::Flags flags, const std::vector< bool > &byte_enable, int &frag_size, int &size_left) const |

| Helper function used to set up the request for a single fragment of a memory access. More... | |

| Fault | readMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | initiateMemMgmtCmd (Request::Flags flags) override |

| Memory management commands such as hardware transactional memory commands or TLB invalidation commands are memory operations but are neither really (true) loads nor stores. More... | |

| void | htmSendAbortSignal (ThreadID tid, uint64_t htm_uid, HtmFailureFaultCause cause) override |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | amoMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| void | regProbePoints () override |

| void | printAddr (Addr a) |

| Print state of address in memory system via PrintReq (for debugging). More... | |

Public Member Functions inherited from gem5::BaseSimpleCPU Public Member Functions inherited from gem5::BaseSimpleCPU | |

| BaseSimpleCPU (const BaseSimpleCPUParams ¶ms) | |

| virtual | ~BaseSimpleCPU () |

| void | wakeup (ThreadID tid) override |

| void | checkForInterrupts () |

| void | setupFetchRequest (const RequestPtr &req) |

| void | serviceInstCountEvents () |

| void | preExecute () |

| void | postExecute () |

| void | advancePC (const Fault &fault) |

| void | haltContext (ThreadID thread_num) override |

| void | resetStats () override |

| virtual Fault | initiateMemRead (Addr addr, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| virtual Fault | initiateMemAMO (Addr addr, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| void | countInst () |

| Counter | totalInsts () const override |

| Counter | totalOps () const override |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| void | unserializeThread (CheckpointIn &cp, ThreadID tid) override |

Protected Member Functions | |

| Tick | sendPacket (RequestPort &port, const PacketPtr &pkt) override |

| Tick | fetchInstMem () override |

Protected Member Functions inherited from gem5::AtomicSimpleCPU Protected Member Functions inherited from gem5::AtomicSimpleCPU | |

| void | tick () |

| bool | isCpuDrained () const |

| Check if a system is in a drained state. More... | |

| bool | tryCompleteDrain () |

| Try to complete a drain request. More... | |

| Port & | getDataPort () override |

| Return a reference to the data port. More... | |

| Port & | getInstPort () override |

| Return a reference to the instruction port. More... | |

| void | threadSnoop (PacketPtr pkt, ThreadID sender) |

| Perform snoop for other cpu-local thread contexts. More... | |

Protected Member Functions inherited from gem5::BaseSimpleCPU Protected Member Functions inherited from gem5::BaseSimpleCPU | |

| void | checkPcEventQueue () |

| void | swapActiveThread () |

| void | traceFault () |

| Handler used when encountering a fault; its purpose is to tear down the InstRecord. More... | |

Protected Attributes | |

| AddrRangeMap< MemBackdoorPtr, 1 > | memBackdoors |

Protected Attributes inherited from gem5::AtomicSimpleCPU Protected Attributes inherited from gem5::AtomicSimpleCPU | |

| EventFunctionWrapper | tickEvent |

| const int | width |

| bool | locked |

| const bool | simulate_data_stalls |

| const bool | simulate_inst_stalls |

| AtomicCPUPort | icachePort |

| AtomicCPUDPort | dcachePort |

| RequestPtr | ifetch_req |

| RequestPtr | data_read_req |

| RequestPtr | data_write_req |

| RequestPtr | data_amo_req |

| bool | dcache_access |

| Tick | dcache_latency |

| ProbePointArg< std::pair< SimpleThread *, const StaticInstPtr > > * | ppCommit |

| Probe Points. More... | |

Protected Attributes inherited from gem5::BaseSimpleCPU Protected Attributes inherited from gem5::BaseSimpleCPU | |

| ThreadID | curThread |

| branch_prediction::BPredUnit * | branchPred |

| Status | _status |

| std::unique_ptr< PCStateBase > | preExecuteTempPC |

Additional Inherited Members | |

Public Attributes inherited from gem5::BaseSimpleCPU Public Attributes inherited from gem5::BaseSimpleCPU | |

| Trace::InstRecord * | traceData |

| CheckerCPU * | checker |

| std::vector< SimpleExecContext * > | threadInfo |

| std::list< ThreadID > | activeThreads |

| StaticInstPtr | curStaticInst |

| Current instruction. More... | |

| StaticInstPtr | curMacroStaticInst |

Protected Types inherited from gem5::BaseSimpleCPU Protected Types inherited from gem5::BaseSimpleCPU | |

| enum | Status { Idle, Running, Faulting, ITBWaitResponse, IcacheRetry, IcacheWaitResponse, IcacheWaitSwitch, DTBWaitResponse, DcacheRetry, DcacheWaitResponse, DcacheWaitSwitch } |

Detailed Description

The NonCachingSimpleCPU is an AtomicSimpleCPU using the 'atomic_noncaching' memory mode instead of just 'atomic'.

Definition at line 53 of file noncaching.hh.

Constructor & Destructor Documentation

◆ NonCachingSimpleCPU()

| gem5::NonCachingSimpleCPU::NonCachingSimpleCPU | ( | const BaseNonCachingSimpleCPUParams & | p | ) |

Definition at line 47 of file noncaching.cc.

References fatal_if, gem5::FullSystem, and gem5::VegaISA::p.

Member Function Documentation

◆ fetchInstMem()

|

overrideprotectedvirtual |

Reimplemented from gem5::AtomicSimpleCPU.

Definition at line 91 of file noncaching.cc.

References gem5::PowerISA::bd, gem5::BaseSimpleCPU::curThread, decoder, gem5::AtomicSimpleCPU::fetchInstMem(), gem5::AtomicSimpleCPU::ifetch_req, memBackdoors, gem5::ArmISA::offset, and gem5::BaseSimpleCPU::threadInfo.

◆ sendPacket()

|

overrideprotectedvirtual |

Reimplemented from gem5::AtomicSimpleCPU.

Definition at line 66 of file noncaching.cc.

References gem5::PowerISA::bd, memBackdoors, panic, and gem5::RequestPort::sendAtomicBackdoor().

◆ verifyMemoryMode()

|

override |

Definition at line 57 of file noncaching.cc.

References fatal, and gem5::X86ISA::system.

Member Data Documentation

◆ memBackdoors

|

protected |

Definition at line 61 of file noncaching.hh.

Referenced by fetchInstMem(), and sendPacket().

The documentation for this class was generated from the following files:

- cpu/simple/noncaching.hh

- cpu/simple/noncaching.cc