Request for doing barrier accounting in the store buffer. More...

#include <lsq.hh>

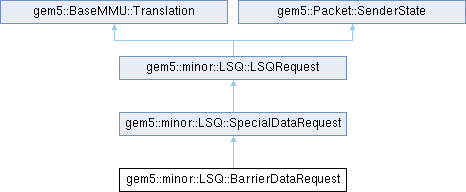

Inheritance diagram for gem5::minor::LSQ::BarrierDataRequest:

Public Member Functions | |

| bool | isBarrier () |

| Is this a request a barrier? | |

| BarrierDataRequest (LSQ &port_, MinorDynInstPtr inst_) | |

Public Member Functions inherited from gem5::minor::LSQ::SpecialDataRequest Public Member Functions inherited from gem5::minor::LSQ::SpecialDataRequest | |

| void | startAddrTranslation () |

| Send single translation request. | |

| PacketPtr | getHeadPacket () |

| Get the head packet as counted by numIssuedFragments. | |

| void | stepToNextPacket () |

| Step on numIssuedFragments. | |

| bool | sentAllPackets () |

| Has no packets to send. | |

| bool | hasPacketsInMemSystem () |

| Never sends any requests. | |

| void | retireResponse (PacketPtr packet_) |

| Keep the given packet as the response packet LSQRequest::packet. | |

| SpecialDataRequest (LSQ &port_, MinorDynInstPtr inst_) | |

Public Member Functions inherited from gem5::minor::LSQ::LSQRequest Public Member Functions inherited from gem5::minor::LSQ::LSQRequest | |

| LSQRequest (LSQ &port_, MinorDynInstPtr inst_, bool isLoad_, PacketDataPtr data_=NULL, uint64_t *res_=NULL) | |

| virtual | ~LSQRequest () |

| void | makePacket () |

| Make a packet to use with the memory transaction. | |

| bool | skippedMemAccess () |

| Was no memory access attempted for this request? | |

| void | setSkipped () |

| Set this request as having been skipped before a memory transfer was attempt. | |

| AddrRangeCoverage | containsAddrRangeOf (LSQRequest *other_request) |

| Does this request's address range fully cover the range of other_request? | |

| virtual void | startAddrTranslation ()=0 |

| Start the address translation process for this request. | |

| virtual PacketPtr | getHeadPacket ()=0 |

| Get the next packet to issue for this request. | |

| virtual void | stepToNextPacket ()=0 |

| Step to the next packet for the next call to getHeadPacket. | |

| virtual bool | sentAllPackets ()=0 |

| Have all packets been sent? | |

| virtual bool | hasPacketsInMemSystem ()=0 |

| True if this request has any issued packets in the memory system and so can't be interrupted until it gets responses. | |

| virtual void | retireResponse (PacketPtr packet_)=0 |

| Retire a response packet into the LSQRequest packet possibly completing this transfer. | |

| virtual bool | isBarrier () |

| Is this a request a barrier? | |

| bool | needsToBeSentToStoreBuffer () |

| This request, once processed by the requests/transfers queues, will need to go to the store buffer. | |

| void | setState (LSQRequestState new_state) |

| Set state and output trace output. | |

| bool | isComplete () const |

| Has this request been completed. | |

| void | reportData (std::ostream &os) const |

| MinorTrace report interface. | |

Public Member Functions inherited from gem5::BaseMMU::Translation Public Member Functions inherited from gem5::BaseMMU::Translation | |

| virtual | ~Translation () |

| virtual void | markDelayed ()=0 |

| Signal that the translation has been delayed due to a hw page table walk. | |

| virtual void | finish (const Fault &fault, const RequestPtr &req, ThreadContext *tc, BaseMMU::Mode mode)=0 |

| virtual bool | squashed () const |

| This function is used by the page table walker to determine if it should translate the a pending request or if the underlying request has been squashed. | |

Public Member Functions inherited from gem5::Packet::SenderState Public Member Functions inherited from gem5::Packet::SenderState | |

| SenderState () | |

| virtual | ~SenderState () |

Additional Inherited Members | |

Public Types inherited from gem5::minor::LSQ::LSQRequest Public Types inherited from gem5::minor::LSQ::LSQRequest | |

| enum | LSQRequestState { NotIssued , InTranslation , Translated , Failed , RequestIssuing , StoreToStoreBuffer , RequestNeedsRetry , StoreInStoreBuffer , StoreBufferIssuing , StoreBufferNeedsRetry , Complete } |

Static Public Member Functions inherited from gem5::minor::LSQ::LSQRequest Static Public Member Functions inherited from gem5::minor::LSQ::LSQRequest | |

| static AddrRangeCoverage | containsAddrRangeOf (Addr req1_addr, unsigned int req1_size, Addr req2_addr, unsigned int req2_size) |

| Does address range req1 (req1_addr to req1_addr + req1_size - 1) fully cover, partially cover or not cover at all the range req2. | |

Public Attributes inherited from gem5::minor::LSQ::LSQRequest Public Attributes inherited from gem5::minor::LSQ::LSQRequest | |

| LSQ & | port |

| Owning port. | |

| MinorDynInstPtr | inst |

| Instruction which made this request. | |

| bool | isLoad |

| Load/store indication used for building packet. | |

| PacketDataPtr | data |

| Dynamically allocated and populated data carried for building write packets. | |

| PacketPtr | packet |

| RequestPtr | request |

| The underlying request of this LSQRequest. | |

| uint64_t * | res |

| Res from pushRequest. | |

| bool | skipped |

| Was skipped. | |

| bool | issuedToMemory |

| This in an access other than a normal cacheable load that's visited the memory system. | |

| bool | isTranslationDelayed |

| Address translation is delayed due to table walk. | |

| LSQRequestState | state |

Public Attributes inherited from gem5::Packet::SenderState Public Attributes inherited from gem5::Packet::SenderState | |

| SenderState * | predecessor |

Protected Member Functions inherited from gem5::minor::LSQ::SpecialDataRequest Protected Member Functions inherited from gem5::minor::LSQ::SpecialDataRequest | |

| void | finish (const Fault &fault_, const RequestPtr &request_, ThreadContext *tc, BaseMMU::Mode mode) |

| TLB interace. | |

Protected Member Functions inherited from gem5::minor::LSQ::LSQRequest Protected Member Functions inherited from gem5::minor::LSQ::LSQRequest | |

| void | markDelayed () |

| BaseMMU::Translation interface. | |

| void | tryToSuppressFault () |

| Instructions may want to suppress translation faults (e.g. | |

| void | disableMemAccess () |

| void | completeDisabledMemAccess () |

Detailed Description

Request for doing barrier accounting in the store buffer.

Not for use outside that unit

Constructor & Destructor Documentation

◆ BarrierDataRequest()

|

inline |

Definition at line 339 of file lsq.hh.

References gem5::minor::LSQ::LSQRequest::Complete, and gem5::minor::LSQ::LSQRequest::state.

Member Function Documentation

◆ isBarrier()

|

inlinevirtual |

Is this a request a barrier?

Reimplemented from gem5::minor::LSQ::LSQRequest.

The documentation for this class was generated from the following file:

- cpu/minor/lsq.hh