#include <interrupt_handler.hh>

Classes | |

| class | DmaEvent |

| struct | SenderState |

Public Member Functions | |

| AMDGPUInterruptHandler (const AMDGPUInterruptHandlerParams &p) | |

| Tick | write (PacketPtr pkt) override |

| Pure virtual function that the device must implement. More... | |

| Tick | read (PacketPtr pkt) override |

| Pure virtual function that the device must implement. More... | |

| AddrRangeList | getAddrRanges () const override |

| Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

| void | setGPUDevice (AMDGPUDevice *gpu_device) |

| void | prepareInterruptCookie (ContextID cntxtId, uint32_t ring_id, uint32_t client_id, uint32_t source_id) |

| void | submitInterruptCookie () |

| void | submitWritePointer () |

| void | intrPost () |

| void | writeMMIO (PacketPtr pkt, Addr mmio_offset) |

| Methods for setting the values of interrupt handler MMIO registers. More... | |

| uint32_t | getDoorbellOffset () const |

| void | setCntl (const uint32_t &data) |

| void | setBase (const uint32_t &data) |

| void | setBaseHi (const uint32_t &data) |

| void | setRptr (const uint32_t &data) |

| void | setWptr (const uint32_t &data) |

| void | setWptrAddrLo (const uint32_t &data) |

| void | setWptrAddrHi (const uint32_t &data) |

| void | setDoorbellOffset (const uint32_t &data) |

| void | updateRptr (const uint32_t &data) |

Public Member Functions inherited from gem5::DmaDevice Public Member Functions inherited from gem5::DmaDevice | |

| DmaDevice (const Params &p) | |

| virtual | ~DmaDevice ()=default |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, uint32_t sid, uint32_t ssid, Tick delay=0) |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, uint32_t sid, uint32_t ssid, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| bool | dmaPending () const |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| unsigned int | cacheBlockSize () const |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. More... | |

Public Member Functions inherited from gem5::PioDevice Public Member Functions inherited from gem5::PioDevice | |

| PioDevice (const Params &p) | |

| virtual | ~PioDevice () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. More... | |

Public Member Functions inherited from gem5::ClockedObject Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from gem5::SimObject Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| virtual void | regProbePoints () |

| Register probe points for this object. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. More... | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from gem5::EventManager Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. More... | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. More... | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Public Member Functions inherited from gem5::Serializable Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from gem5::Drainable Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Public Member Functions inherited from gem5::statistics::Group Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. More... | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. More... | |

| virtual void | resetStats () |

| Callback to reset stats. More... | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. More... | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. More... | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. More... | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. More... | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. More... | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. More... | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. More... | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

Public Member Functions inherited from gem5::Named Public Member Functions inherited from gem5::Named | |

| Named (const std::string &name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Public Member Functions inherited from gem5::Clocked Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Private Attributes | |

| AMDGPUDevice * | gpuDevice |

| AMDGPUIHRegs | regs |

| std::queue< AMDGPUInterruptCookie * > | interruptQueue |

| AMDGPUInterruptHandler::DmaEvent * | dmaEvent |

Additional Inherited Members | |

Public Types inherited from gem5::DmaDevice Public Types inherited from gem5::DmaDevice | |

| typedef DmaDeviceParams | Params |

Public Types inherited from gem5::PioDevice Public Types inherited from gem5::PioDevice | |

| using | Params = PioDeviceParams |

Public Types inherited from gem5::ClockedObject Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. More... | |

Public Types inherited from gem5::SimObject Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Static Public Member Functions inherited from gem5::SimObject Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. More... | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. More... | |

Static Public Member Functions inherited from gem5::Serializable Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. More... | |

Public Attributes inherited from gem5::ClockedObject Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Protected Member Functions inherited from gem5::Drainable Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. More... | |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from gem5::Clocked Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. More... | |

Protected Attributes inherited from gem5::DmaDevice Protected Attributes inherited from gem5::DmaDevice | |

| DmaPort | dmaPort |

Protected Attributes inherited from gem5::PioDevice Protected Attributes inherited from gem5::PioDevice | |

| System * | sys |

| PioPort< PioDevice > | pioPort |

| The pioPort that handles the requests for us and provides us requests that it sees. More... | |

Protected Attributes inherited from gem5::SimObject Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from gem5::EventManager Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

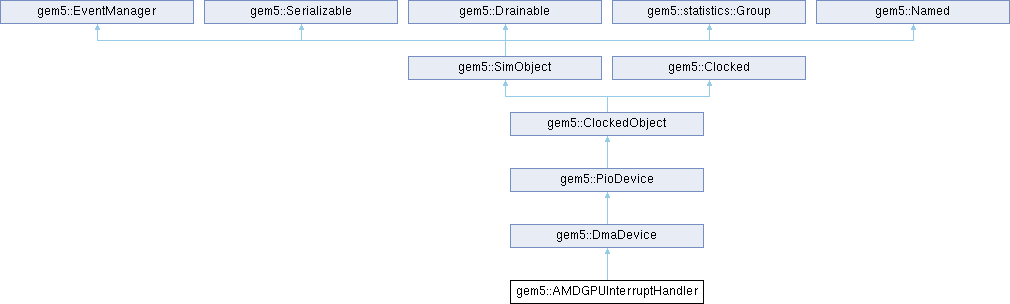

Detailed Description

Definition at line 130 of file interrupt_handler.hh.

Constructor & Destructor Documentation

◆ AMDGPUInterruptHandler()

| gem5::AMDGPUInterruptHandler::AMDGPUInterruptHandler | ( | const AMDGPUInterruptHandlerParams & | p | ) |

Definition at line 53 of file interrupt_handler.cc.

References regs.

Member Function Documentation

◆ getAddrRanges()

|

overridevirtual |

Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to.

- Returns

- a list of non-overlapping address ranges

Implements gem5::PioDevice.

Definition at line 61 of file interrupt_handler.cc.

◆ getDoorbellOffset()

|

inline |

Definition at line 184 of file interrupt_handler.hh.

References gem5::AMDGPUIHRegs::IH_Doorbell, and regs.

Referenced by writeMMIO().

◆ intrPost()

| void gem5::AMDGPUInterruptHandler::intrPost | ( | ) |

Definition at line 68 of file interrupt_handler.cc.

References gpuDevice, and gem5::AMDGPUDevice::intrPost().

Referenced by gem5::AMDGPUInterruptHandler::DmaEvent::process().

◆ prepareInterruptCookie()

| void gem5::AMDGPUInterruptHandler::prepareInterruptCookie | ( | ContextID | cntxtId, |

| uint32_t | ring_id, | ||

| uint32_t | client_id, | ||

| uint32_t | source_id | ||

| ) |

Setup the fields in the interrupt cookie (see header file for more detail on the fields). The timestamp here is a bogus value. It seems the driver does not really care what this value is. Additionally the model does not currently have anything to keep track of time. It is possible that tick/cycle count can be used in the future if this ends up being important. The remaining fields are passed from whichever block is sending the interrupt.

Definition at line 75 of file interrupt_handler.cc.

References gem5::AMDGPUInterruptCookie::clientId, gem5::CP_EOP, interruptQueue, gem5::AMDGPUInterruptCookie::pasid, gem5::AMDGPUInterruptCookie::ringId, gem5::SOC15_IH_CLIENTID_GRBM_CP, gem5::SOC15_IH_CLIENTID_RLC, gem5::SOC15_IH_CLIENTID_SDMA0, gem5::SOC15_IH_CLIENTID_SDMA1, gem5::SOC15_IH_CLIENTID_SDMA2, gem5::SOC15_IH_CLIENTID_SDMA3, gem5::SOC15_IH_CLIENTID_SDMA4, gem5::SOC15_IH_CLIENTID_SDMA5, gem5::SOC15_IH_CLIENTID_SDMA6, gem5::SOC15_IH_CLIENTID_SDMA7, gem5::AMDGPUInterruptCookie::source_data_dw1, gem5::AMDGPUInterruptCookie::sourceId, gem5::AMDGPUInterruptCookie::timestamp_Lo, and gem5::TRAP_ID.

Referenced by gem5::PM4PacketProcessor::releaseMemDone(), and gem5::SDMAEngine::trap().

◆ read()

Pure virtual function that the device must implement.

Called when a read command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 167 of file interrupt_handler.hh.

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 260 of file interrupt_handler.cc.

References gem5::AMDGPUIHRegs::baseAddr, gem5::AMDGPUIHRegs::IH_Base, gem5::AMDGPUIHRegs::IH_Base_Hi, gem5::AMDGPUIHRegs::IH_Cntl, gem5::AMDGPUIHRegs::IH_Doorbell, gem5::AMDGPUIHRegs::IH_Rptr, gem5::AMDGPUIHRegs::IH_Wptr, gem5::AMDGPUIHRegs::IH_Wptr_Addr_Hi, gem5::AMDGPUIHRegs::IH_Wptr_Addr_Lo, regs, SERIALIZE_SCALAR, and gem5::AMDGPUIHRegs::WptrAddr.

◆ setBase()

| void gem5::AMDGPUInterruptHandler::setBase | ( | const uint32_t & | data | ) |

Definition at line 209 of file interrupt_handler.cc.

References gem5::AMDGPUIHRegs::baseAddr, data, and regs.

Referenced by writeMMIO().

◆ setBaseHi()

| void gem5::AMDGPUInterruptHandler::setBaseHi | ( | const uint32_t & | data | ) |

Definition at line 216 of file interrupt_handler.cc.

References gem5::AMDGPUIHRegs::baseAddr, data, and regs.

Referenced by writeMMIO().

◆ setCntl()

| void gem5::AMDGPUInterruptHandler::setCntl | ( | const uint32_t & | data | ) |

Definition at line 203 of file interrupt_handler.cc.

References data, gem5::AMDGPUIHRegs::IH_Cntl, and regs.

Referenced by writeMMIO().

◆ setDoorbellOffset()

| void gem5::AMDGPUInterruptHandler::setDoorbellOffset | ( | const uint32_t & | data | ) |

Definition at line 248 of file interrupt_handler.cc.

References data, gem5::AMDGPUIHRegs::IH_Doorbell, and regs.

Referenced by writeMMIO().

◆ setGPUDevice()

|

inline |

Definition at line 172 of file interrupt_handler.hh.

References gpuDevice.

Referenced by gem5::AMDGPUDevice::AMDGPUDevice().

◆ setRptr()

| void gem5::AMDGPUInterruptHandler::setRptr | ( | const uint32_t & | data | ) |

Definition at line 222 of file interrupt_handler.cc.

References data, gem5::AMDGPUIHRegs::IH_Rptr, and regs.

Referenced by writeMMIO().

◆ setWptr()

| void gem5::AMDGPUInterruptHandler::setWptr | ( | const uint32_t & | data | ) |

Definition at line 228 of file interrupt_handler.cc.

References data, gem5::AMDGPUIHRegs::IH_Wptr, and regs.

Referenced by writeMMIO().

◆ setWptrAddrHi()

| void gem5::AMDGPUInterruptHandler::setWptrAddrHi | ( | const uint32_t & | data | ) |

Definition at line 241 of file interrupt_handler.cc.

References data, gem5::AMDGPUIHRegs::IH_Wptr_Addr_Hi, regs, and gem5::AMDGPUIHRegs::WptrAddr.

Referenced by writeMMIO().

◆ setWptrAddrLo()

| void gem5::AMDGPUInterruptHandler::setWptrAddrLo | ( | const uint32_t & | data | ) |

Definition at line 234 of file interrupt_handler.cc.

References data, gem5::AMDGPUIHRegs::IH_Wptr_Addr_Lo, regs, and gem5::AMDGPUIHRegs::WptrAddr.

Referenced by writeMMIO().

◆ submitInterruptCookie()

| void gem5::AMDGPUInterruptHandler::submitInterruptCookie | ( | ) |

Definition at line 146 of file interrupt_handler.cc.

References gem5::AMDGPUIHRegs::baseAddr, dmaEvent, gem5::DmaDevice::dmaWrite(), DPRINTF, gem5::AMDGPUIHRegs::IH_Rptr, gem5::AMDGPUIHRegs::IH_Wptr, interruptQueue, and regs.

Referenced by gem5::PM4PacketProcessor::releaseMemDone(), and gem5::SDMAEngine::trap().

◆ submitWritePointer()

| void gem5::AMDGPUInterruptHandler::submitWritePointer | ( | ) |

Definition at line 134 of file interrupt_handler.cc.

References dmaEvent, gem5::DmaDevice::dmaWrite(), gem5::AMDGPUIHRegs::IH_Wptr, regs, and gem5::AMDGPUIHRegs::WptrAddr.

Referenced by gem5::AMDGPUInterruptHandler::DmaEvent::process().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 286 of file interrupt_handler.cc.

References gem5::AMDGPUIHRegs::baseAddr, gem5::AMDGPUIHRegs::IH_Base, gem5::AMDGPUIHRegs::IH_Base_Hi, gem5::AMDGPUIHRegs::IH_Cntl, gem5::AMDGPUIHRegs::IH_Doorbell, gem5::AMDGPUIHRegs::IH_Rptr, gem5::AMDGPUIHRegs::IH_Wptr, gem5::AMDGPUIHRegs::IH_Wptr_Addr_Hi, gem5::AMDGPUIHRegs::IH_Wptr_Addr_Lo, regs, UNSERIALIZE_SCALAR, and gem5::AMDGPUIHRegs::WptrAddr.

◆ updateRptr()

| void gem5::AMDGPUInterruptHandler::updateRptr | ( | const uint32_t & | data | ) |

Definition at line 254 of file interrupt_handler.cc.

References data, gem5::AMDGPUIHRegs::IH_Rptr, and regs.

Referenced by gem5::AMDGPUDevice::writeDoorbell().

◆ write()

Pure virtual function that the device must implement.

Called when a write command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 166 of file interrupt_handler.hh.

◆ writeMMIO()

Methods for setting the values of interrupt handler MMIO registers.

Definition at line 165 of file interrupt_handler.cc.

References gem5::bits(), DPRINTF, getDoorbellOffset(), gem5::Packet::getLE(), gpuDevice, gem5::InterruptHandler, mmIH_DOORBELL_RPTR, mmIH_RB_BASE, mmIH_RB_BASE_HI, mmIH_RB_CNTL, mmIH_RB_RPTR, mmIH_RB_WPTR, mmIH_RB_WPTR_ADDR_HI, mmIH_RB_WPTR_ADDR_LO, setBase(), setBaseHi(), setCntl(), setDoorbellOffset(), gem5::AMDGPUDevice::setDoorbellType(), setRptr(), setWptr(), setWptrAddrHi(), and setWptrAddrLo().

Referenced by gem5::AMDGPUDevice::writeMMIO().

Member Data Documentation

◆ dmaEvent

|

private |

Definition at line 199 of file interrupt_handler.hh.

Referenced by submitInterruptCookie(), and submitWritePointer().

◆ gpuDevice

|

private |

Definition at line 196 of file interrupt_handler.hh.

Referenced by intrPost(), setGPUDevice(), and writeMMIO().

◆ interruptQueue

|

private |

Definition at line 198 of file interrupt_handler.hh.

Referenced by prepareInterruptCookie(), and submitInterruptCookie().

◆ regs

|

private |

Definition at line 197 of file interrupt_handler.hh.

Referenced by AMDGPUInterruptHandler(), getDoorbellOffset(), serialize(), setBase(), setBaseHi(), setCntl(), setDoorbellOffset(), setRptr(), setWptr(), setWptrAddrHi(), setWptrAddrLo(), submitInterruptCookie(), submitWritePointer(), unserialize(), and updateRptr().

The documentation for this class was generated from the following files:

- dev/amdgpu/interrupt_handler.hh

- dev/amdgpu/interrupt_handler.cc