PM4 packets. More...

#include <pm4_defines.hh>

Public Attributes | |

| union { | |

| struct { | |

| uint16_t predicated: 1 | |

| uint16_t shader: 1 | |

| uint16_t reserved: 6 | |

| uint16_t opcode: 8 | |

| uint16_t count: 14 | |

| uint16_t type: 2 | |

| } | |

| uint32_t ordinal | |

| }; | |

| uint32_t | reserved1: 8 |

| uint32_t | destSel: 4 |

| uint32_t | reserved2: 4 |

| uint32_t | addrIncr: 1 |

| uint32_t | reserved3: 2 |

| uint32_t | resume: 1 |

| uint32_t | writeConfirm: 1 |

| uint32_t | reserved4: 4 |

| uint32_t | cachePolicy: 2 |

| uint32_t | reserved5: 5 |

| union { | |

| struct { | |

| uint32_t destAddrLo | |

| uint32_t destAddrHi | |

| } | |

| uint64_t destAddr | |

| }; | |

| uint32_t | data |

| uint32_t | queueSel: 2 |

| uint32_t | vmid: 4 |

| uint32_t | queueSlot: 3 |

| uint32_t | pipe: 2 |

| uint32_t | me: 1 |

| uint32_t | reserved6: 2 |

| uint32_t | queueType: 3 |

| uint32_t | allocFormat: 2 |

| uint32_t | engineSel: 3 |

| uint32_t | numQueues: 3 |

| uint32_t | checkDisable: 1 |

| uint32_t | doorbellOffset: 26 |

| union { | |

| struct { | |

| uint32_t mqdAddrLo: 32 | |

| uint32_t mqdAddrHi: 32 | |

| } | |

| uint64_t mqdAddr | |

| }; | |

| union { | |

| struct { | |

| uint32_t wptrAddrLo: 32 | |

| uint32_t wptrAddrHi: 32 | |

| } | |

| uint64_t wptrAddr | |

| }; | |

| uint32_t | action: 2 |

| uint32_t | reserved: 2 |

| union { | |

| struct { | |

| uint32_t pasid: 16 | |

| uint32_t reserved2: 16 | |

| } | |

| struct { | |

| uint32_t reserved3: 2 | |

| uint32_t doorbellOffset0: 26 | |

| uint32_t reserved4: 4 | |

| } | |

| }; | |

| uint32_t | doorbellOffset1: 26 |

| uint32_t | reserved7: 2 |

| uint32_t | doorbellOffset2: 26 |

| uint32_t | reserved8: 4 |

| uint32_t | reserved9: 2 |

| uint32_t | doorbellOffset3: 26 |

| uint32_t | reserved10: 4 |

| uint32_t | vmidMask: 16 |

| uint32_t | unmapLatency: 8 |

| union { | |

| struct { | |

| uint32_t queueMaskLo | |

| uint32_t queueMaskHi | |

| } | |

| uint64_t queueMask | |

| }; | |

| union { | |

| struct { | |

| uint32_t gwsMaskLo | |

| uint32_t gwsMaskHi | |

| } | |

| uint64_t gwsMask | |

| }; | |

| uint16_t | oacMask |

| uint16_t | reserved1 |

| uint32_t | gdsHeapBase: 6 |

| uint32_t | gdsHeapSize: 6 |

| uint32_t | reserved0: 8 |

| uint32_t | diq: 1 |

| uint32_t | processQuantum: 7 |

| union { | |

| struct { | |

| uint32_t ptBaseLo | |

| uint32_t ptBaseHi | |

| } | |

| uint64_t ptBase | |

| }; | |

| uint32_t | shMemBases |

| uint32_t | shMemConfig |

| union { | |

| struct { | |

| uint32_t gdsAddrLo | |

| uint32_t gdsAddrHi | |

| } | |

| uint64_t gdsAddr | |

| }; | |

| uint32_t | numGws: 6 |

| uint32_t | numOac: 4 |

| uint32_t | gdsSize: 6 |

| union { | |

| struct { | |

| uint32_t completionSignalLo | |

| uint32_t completionSignalHi | |

| } | |

| uint64_t completionSignal | |

| }; | |

| union { | |

| struct { | |

| uint32_t ptBaseLo | |

| uint32_t ptBaseHi | |

| } | |

| uint64_t ptBase | |

| }; | |

| uint32_t | sqShaderTbaLo |

| uint32_t | sqShaderTbaHi |

| uint32_t | sqShaderTmaLo |

| uint32_t | sqShaderTmaHi |

| union { | |

| struct { | |

| uint32_t gdsAddrLo | |

| uint32_t gdsAddrHi | |

| } | |

| uint64_t gdsAddr | |

| }; | |

| union { | |

| struct { | |

| uint32_t numGws: 7 | |

| uint32_t sdma_enable: 1 | |

| uint32_t numOac: 4 | |

| uint32_t reserved3: 4 | |

| uint32_t gdsSize: 6 | |

| uint32_t numQueues: 10 | |

| } | |

| uint32_t ordinal14 | |

| }; | |

| uint32_t | spiGdbgPerVmidCntl |

| uint32_t | tcpWatchCntl [4] |

| union { | |

| struct { | |

| uint32_t completionSignalLo | |

| uint32_t completionSignalHi | |

| } | |

| uint64_t completionSignal | |

| }; | |

| uint32_t | function: 4 |

| uint32_t | memSpace: 2 |

| uint32_t | operation: 2 |

| union { | |

| struct { | |

| uint32_t regAddr1: 18 | |

| uint32_t reserved2: 14 | |

| } | |

| uint32_t memAddrLo | |

| }; | |

| union { | |

| struct { | |

| uint32_t regAddr2: 18 | |

| uint32_t reserved3: 14 | |

| } | |

| uint32_t memAddrHi | |

| }; | |

| uint32_t | reference |

| uint32_t | mask |

| uint32_t | pollInterval |

| uint32_t | regOffset: 16 |

| uint32_t | regData |

| union { | |

| struct { | |

| uint32_t ibBaseLo | |

| uint32_t ibBaseHi | |

| } | |

| uint64_t ibBase | |

| }; | |

| uint32_t | ibSize: 20 |

| uint32_t | chain: 1 |

| uint32_t | poll: 1 |

| uint32_t | valid: 1 |

| uint32_t | priv: 1 |

| union { | |

| struct { | |

| uint32_t tmz: 1 | |

| uint32_t reserved: 31 | |

| } | |

| uint32_t dummy | |

| }; | |

| union { | |

| struct { | |

| uint32_t ibBaseLo | |

| uint32_t ibBaseHi | |

| } | |

| uint64_t ibBase | |

| }; | |

| uint32_t | ena: 1 |

| uint32_t | preResume: 1 |

| uint32_t | command: 4 |

| uint32_t | event: 6 |

| uint32_t | eventIdx: 4 |

| uint32_t | l1Volatile: 1 |

| uint32_t | l2Volatile: 1 |

| uint32_t | l2WB: 1 |

| uint32_t | l1Inv: 1 |

| uint32_t | l2Inv: 1 |

| uint32_t | l2NC: 1 |

| uint32_t | l2WC: 1 |

| uint32_t | l2Meta: 1 |

| uint32_t | execute: 1 |

| uint32_t | destSelect: 2 |

| uint32_t | intSelect: 3 |

| uint32_t | dataSelect: 3 |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| uint64_t addr | |

| }; | |

| union { | |

| struct { | |

| union { | |

| struct { | |

| uint32_t dwOffset: 16 | |

| uint32_t numDws: 16 | |

| } | |

| uint32_t dataLo: 32 | |

| } | |

| uint32_t dataHi | |

| } | |

| uint64_t data | |

| }; | |

| uint32_t | intCtxId |

| uint32_t | offset: 16 |

| union { | |

| struct { | |

| uint32_t ibBaseLo | |

| uint32_t ibBaseHi | |

| } | |

| uint64_t ibBase | |

| }; | |

| uint32_t | offleadPolling: 1 |

| uint32_t | processCnt: 4 |

| uint32_t | contextId: 28 |

| uint32_t | interruptSel: 2 |

| union { | |

| struct { | |

| uint32_t pasid: 16 | |

| uint32_t reserved0: 16 | |

| } | |

| struct { | |

| uint32_t reserved1: 2 | |

| uint32_t doorbellOffset: 26 | |

| uint32_t engineSel: 3 | |

| uint32_t reserved2: 1 | |

| } | |

| }; | |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| uint64_t addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t dataLo | |

| uint32_t dataHi | |

| } | |

| uint64_t data | |

| }; | |

| union { | |

| struct { | |

| uint32_t cp_mqd_readindex_lo | |

| uint32_t cp_mqd_readindex_hi | |

| } | |

| uint64_t mqdReadIndex | |

| }; | |

| uint32_t | cp_mqd_save_start_time_lo |

| uint32_t | cp_mqd_save_start_time_hi |

| uint32_t | cp_mqd_save_end_time_lo |

| uint32_t | cp_mqd_save_end_time_hi |

| uint32_t | cp_mqd_restore_start_time_lo |

| uint32_t | cp_mqd_restore_start_time_hi |

| uint32_t | cp_mqd_restore_end_time_lo |

| uint32_t | cp_mqd_restore_end_time_hi |

| uint32_t | disable_queue |

| uint32_t | reserved_107 |

| uint32_t | gds_cs_ctxsw_cnt0 |

| uint32_t | gds_cs_ctxsw_cnt1 |

| uint32_t | gds_cs_ctxsw_cnt2 |

| uint32_t | gds_cs_ctxsw_cnt3 |

| uint32_t | reserved_112 |

| uint32_t | reserved_113 |

| uint32_t | cp_pq_exe_status_lo |

| uint32_t | cp_pq_exe_status_hi |

| uint32_t | cp_packet_id_lo |

| uint32_t | cp_packet_id_hi |

| uint32_t | cp_packet_exe_status_lo |

| uint32_t | cp_packet_exe_status_hi |

| uint32_t | gds_save_base_addr_lo |

| uint32_t | gds_save_base_addr_hi |

| uint32_t | gds_save_mask_lo |

| uint32_t | gds_save_mask_hi |

| uint32_t | ctx_save_base_addr_lo |

| uint32_t | ctx_save_base_addr_hi |

| uint32_t | dynamic_cu_mask_addr_lo |

| uint32_t | dynamic_cu_mask_addr_hi |

| union { | |

| struct { | |

| uint32_t mqd_base_addr_lo | |

| uint32_t mqd_base_addr_hi | |

| } | |

| uint64_t mqdBase | |

| }; | |

| uint32_t | hqd_active |

| uint32_t | hqd_vmid |

| uint32_t | hqd_persistent_state |

| uint32_t | hqd_pipe_priority |

| uint32_t | hqd_queue_priority |

| uint32_t | hqd_quantum |

| union { | |

| struct { | |

| uint32_t hqd_pq_base_lo | |

| uint32_t hqd_pq_base_hi | |

| } | |

| uint64_t base | |

| }; | |

| union { | |

| uint32_t hqd_pq_rptr | |

| uint32_t rptr | |

| }; | |

| union { | |

| struct { | |

| uint32_t hqd_pq_rptr_report_addr_lo | |

| uint32_t hqd_pq_rptr_report_addr_hi | |

| } | |

| uint64_t aqlRptr | |

| }; | |

| uint32_t | hqd_pq_wptr_poll_addr_lo |

| uint32_t | hqd_pq_wptr_poll_addr_hi |

| union { | |

| uint32_t hqd_pq_doorbell_control | |

| uint32_t doorbell | |

| }; | |

| uint32_t | reserved_144 |

| uint32_t | hqd_pq_control |

| union { | |

| struct { | |

| uint32_t hqd_ib_base_addr_lo | |

| uint32_t hqd_ib_base_addr_hi | |

| } | |

| Addr ibBase | |

| }; | |

| union { | |

| uint32_t hqd_ib_rptr | |

| uint32_t ibRptr | |

| }; | |

| uint32_t | hqd_ib_control |

| uint32_t | hqd_iq_timer |

| uint32_t | hqd_iq_rptr |

| uint32_t | cp_hqd_dequeue_request |

| uint32_t | cp_hqd_dma_offload |

| uint32_t | cp_hqd_sema_cmd |

| uint32_t | cp_hqd_msg_type |

| uint32_t | cp_hqd_atomic0_preop_lo |

| uint32_t | cp_hqd_atomic0_preop_hi |

| uint32_t | cp_hqd_atomic1_preop_lo |

| uint32_t | cp_hqd_atomic1_preop_hi |

| uint32_t | cp_hqd_hq_status0 |

| uint32_t | cp_hqd_hq_control0 |

| uint32_t | cp_mqd_control |

| uint32_t | cp_hqd_hq_status1 |

| uint32_t | cp_hqd_hq_control1 |

| uint32_t | cp_hqd_eop_base_addr_lo |

| uint32_t | cp_hqd_eop_base_addr_hi |

| uint32_t | cp_hqd_eop_control |

| uint32_t | cp_hqd_eop_rptr |

| uint32_t | cp_hqd_eop_wptr |

| uint32_t | cp_hqd_eop_done_events |

| uint32_t | cp_hqd_ctx_save_base_addr_lo |

| uint32_t | cp_hqd_ctx_save_base_addr_hi |

| uint32_t | cp_hqd_ctx_save_control |

| uint32_t | cp_hqd_cntl_stack_offset |

| uint32_t | cp_hqd_cntl_stack_size |

| uint32_t | cp_hqd_wg_state_offset |

| uint32_t | cp_hqd_ctx_save_size |

| uint32_t | cp_hqd_gds_resource_state |

| uint32_t | cp_hqd_error |

| uint32_t | cp_hqd_eop_wptr_mem |

| union { | |

| uint32_t cp_hqd_aql_control | |

| uint32_t aql | |

| }; | |

| uint32_t | cp_hqd_pq_wptr_lo |

| uint32_t | cp_hqd_pq_wptr_hi |

| uint32_t | sdmax_rlcx_rb_cntl |

| union { | |

| struct { | |

| uint32_t sdmax_rlcx_rb_base | |

| uint32_t sdmax_rlcx_rb_base_hi | |

| } | |

| uint64_t rb_base | |

| }; | |

| union { | |

| struct { | |

| uint32_t sdmax_rlcx_rb_rptr | |

| uint32_t sdmax_rlcx_rb_rptr_hi | |

| } | |

| uint64_t rptr | |

| }; | |

| union { | |

| struct { | |

| uint32_t sdmax_rlcx_rb_wptr | |

| uint32_t sdmax_rlcx_rb_wptr_hi | |

| } | |

| uint64_t wptr | |

| }; | |

| uint32_t | sdmax_rlcx_rb_wptr_poll_cntl |

| uint32_t | sdmax_rlcx_rb_rptr_addr_hi |

| uint32_t | sdmax_rlcx_rb_rptr_addr_lo |

| uint32_t | sdmax_rlcx_ib_cntl |

| uint32_t | sdmax_rlcx_ib_rptr |

| uint32_t | sdmax_rlcx_ib_offset |

| uint32_t | sdmax_rlcx_ib_base_lo |

| uint32_t | sdmax_rlcx_ib_base_hi |

| uint32_t | sdmax_rlcx_ib_size |

| uint32_t | sdmax_rlcx_skip_cntl |

| uint32_t | sdmax_rlcx_context_status |

| uint32_t | sdmax_rlcx_doorbell |

| uint32_t | sdmax_rlcx_status |

| uint32_t | sdmax_rlcx_doorbell_log |

| uint32_t | sdmax_rlcx_watermark |

| uint32_t | sdmax_rlcx_doorbell_offset |

| uint32_t | sdmax_rlcx_csa_addr_lo |

| uint32_t | sdmax_rlcx_csa_addr_hi |

| uint32_t | sdmax_rlcx_ib_sub_remain |

| uint32_t | sdmax_rlcx_preempt |

| uint32_t | sdmax_rlcx_dummy_reg |

| uint32_t | sdmax_rlcx_rb_wptr_poll_addr_hi |

| uint32_t | sdmax_rlcx_rb_wptr_poll_addr_lo |

| uint32_t | sdmax_rlcx_rb_aql_cntl |

| uint32_t | sdmax_rlcx_minor_ptr_update |

| uint32_t | sdmax_rlcx_midcmd_data0 |

| uint32_t | sdmax_rlcx_midcmd_data1 |

| uint32_t | sdmax_rlcx_midcmd_data2 |

| uint32_t | sdmax_rlcx_midcmd_data3 |

| uint32_t | sdmax_rlcx_midcmd_data4 |

| uint32_t | sdmax_rlcx_midcmd_data5 |

| uint32_t | sdmax_rlcx_midcmd_data6 |

| uint32_t | sdmax_rlcx_midcmd_data7 |

| uint32_t | sdmax_rlcx_midcmd_data8 |

| uint32_t | sdmax_rlcx_midcmd_cntl |

| uint32_t | reserved_42 |

| uint32_t | reserved_43 |

| uint32_t | reserved_44 |

| uint32_t | reserved_45 |

| uint32_t | reserved_46 |

| uint32_t | reserved_47 |

| uint32_t | reserved_48 |

| uint32_t | reserved_49 |

| uint32_t | reserved_50 |

| uint32_t | reserved_51 |

| uint32_t | reserved_52 |

| uint32_t | reserved_53 |

| uint32_t | reserved_54 |

| uint32_t | reserved_55 |

| uint32_t | reserved_56 |

| uint32_t | reserved_57 |

| uint32_t | reserved_58 |

| uint32_t | reserved_59 |

| uint32_t | reserved_60 |

| uint32_t | reserved_61 |

| uint32_t | reserved_62 |

| uint32_t | reserved_63 |

| uint32_t | reserved_64 |

| uint32_t | reserved_65 |

| uint32_t | reserved_66 |

| uint32_t | reserved_67 |

| uint32_t | reserved_68 |

| uint32_t | reserved_69 |

| uint32_t | reserved_70 |

| uint32_t | reserved_71 |

| uint32_t | reserved_72 |

| uint32_t | reserved_73 |

| uint32_t | reserved_74 |

| uint32_t | reserved_75 |

| uint32_t | reserved_76 |

| uint32_t | reserved_77 |

| uint32_t | reserved_78 |

| uint32_t | reserved_79 |

| uint32_t | reserved_80 |

| uint32_t | reserved_81 |

| uint32_t | reserved_82 |

| uint32_t | reserved_83 |

| uint32_t | reserved_84 |

| uint32_t | reserved_85 |

| uint32_t | reserved_86 |

| uint32_t | reserved_87 |

| uint32_t | reserved_88 |

| uint32_t | reserved_89 |

| uint32_t | reserved_90 |

| uint32_t | reserved_91 |

| uint32_t | reserved_92 |

| uint32_t | reserved_93 |

| uint32_t | reserved_94 |

| uint32_t | reserved_95 |

| uint32_t | reserved_96 |

| uint32_t | reserved_97 |

| uint32_t | reserved_98 |

| uint32_t | reserved_99 |

| uint32_t | reserved_100 |

| uint32_t | reserved_101 |

| uint32_t | reserved_102 |

| uint32_t | reserved_103 |

| uint32_t | reserved_104 |

| uint32_t | reserved_105 |

| uint32_t | reserved_106 |

| uint32_t | reserved_108 |

| uint32_t | reserved_109 |

| uint32_t | reserved_110 |

| uint32_t | reserved_111 |

| uint32_t | reserved_114 |

| uint32_t | reserved_115 |

| uint32_t | reserved_116 |

| uint32_t | reserved_117 |

| uint32_t | reserved_118 |

| uint32_t | reserved_119 |

| uint32_t | reserved_120 |

| uint32_t | reserved_121 |

| uint32_t | reserved_122 |

| uint32_t | reserved_123 |

| uint32_t | reserved_124 |

| uint32_t | reserved_125 |

| uint32_t | sdma_engine_id |

| uint32_t | sdma_queue_id |

| uint32_t | count: 30 |

| uint32_t | res0: 2 |

| uint32_t | res1: 16 |

| uint32_t | sdw: 2 |

| uint32_t | res2: 6 |

| uint32_t | ddw: 2 |

| uint32_t | res3: 6 |

| uint64_t | source |

| uint64_t | dest |

| uint32_t | sw: 2 |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| uint32_t | srcData |

| uint32_t | unused: 10 |

| uint32_t | key0 |

| uint32_t | key1 |

| uint32_t | key2 |

| uint32_t | key3 |

| uint32_t | count0 |

| uint32_t | count1 |

| uint32_t | count2 |

| uint32_t | count3 |

| uint32_t | countData0 |

| uint32_t | countData1 |

| uint32_t | countData2 |

| uint32_t | countData3 |

| uint32_t | countKey0 |

| uint32_t | countKey1 |

| uint32_t | countKey2 |

| uint32_t | countKey3 |

| uint32_t | size: 20 |

| uint64_t | csaAddr |

| union { | |

| struct { | |

| uint32_t contextId: 3 | |

| uint32_t rbRptr: 13 | |

| uint32_t ibOffset: 12 | |

| uint32_t reserved: 4 | |

| } | |

| uint32_t intrContext | |

| }; | |

| union { | |

| struct { | |

| uint32_t reserved: 3 | |

| uint32_t addrLo: 29 | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t reserved: 3 | |

| uint32_t addrLo: 29 | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| uint32_t | regAddr: 18 |

| uint32_t | apertureId: 12 |

| uint32_t | byteEnable: 4 |

| uint64_t | address |

| uint32_t | ref |

| uint32_t | pollInt: 16 |

| uint32_t | retryCount: 12 |

| uint32_t | op: 2 |

| uint32_t | func: 3 |

| uint32_t | mode: 1 |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t execCount: 14 | |

| uint32_t unused: 18 | |

| } | |

| uint32_t ordinal | |

| }; | |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t srcDataLo | |

| uint32_t srdDataHi | |

| } | |

| uint64_t srcData | |

| }; | |

| union { | |

| struct { | |

| uint32_t cmpDataLo | |

| uint32_t cmpDataHi | |

| } | |

| uint64_t cmpData | |

| }; | |

| uint32_t | loopInt: 13 |

| int | unused2: 16 |

| int | loop: 1 |

| int | unused1: 8 |

| int | opcode: 7 |

| uint64_t | mask |

| uint64_t | initValue |

| uint64_t | increment |

| union { | |

| struct { | |

| uint32_t initDataLo | |

| uint32_t initDataHi | |

| } | |

| uint64_t initData | |

| }; | |

| uint32_t | opcode: 8 |

| uint32_t | subOpcode: 8 |

| uint32_t | device: 8 |

| uint32_t | byteStride |

| uint32_t | dmaCount |

| union { | |

| struct { | |

| uint32_t destLo | |

| uint32_t destHi | |

| } | |

| uint64_t dest | |

| }; | |

| uint32_t | byteCount: 26 |

| uint16_t | format: 8 |

| uint16_t | barrier: 1 |

| uint16_t | acqFenceScope: 2 |

| uint16_t | relFenceScope: 2 |

| sdmaHeaderAgentDisp | header |

| uint16_t | res0 |

| union { | |

| struct { | |

| uint32_t retLo | |

| uint32_t retHi | |

| } | |

| Addr ret | |

| }; | |

| uint32_t | swDest: 2 |

| uint32_t | res4: 6 |

| uint32_t | swSrc: 2 |

| union { | |

| struct { | |

| uint32_t srcLo | |

| uint32_t srcHi | |

| } | |

| Addr src | |

| }; | |

| union { | |

| struct { | |

| uint32_t destLo | |

| uint32_t destHi | |

| } | |

| Addr dest | |

| }; | |

| uint64_t | res5 |

| uint64_t | res6 |

| union { | |

| struct { | |

| uint32_t compSignalLo | |

| uint32_t compSignalHi | |

| } | |

| Addr compSignal | |

| }; | |

| Addr | depSignal0 |

| Addr | depSignal1 |

| Addr | depSignal2 |

| Addr | depSignal3 |

| Addr | depSignal4 |

| uint64_t | res2 |

| union { | |

| struct { | |

| uint32_t compSignalLo | |

| uint32_t compSignalHi | |

| } | |

| Addr compSignal | |

| }; | |

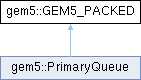

Detailed Description

PM4 packets.

SDMA packets.

Queue descriptor for SDMA-based user queues (RLC queues).

Queue descriptor with relevant MQD attributes.

Taken from https://github.com/RadeonOpenCompute/ROCK-Kernel-Driver/blob/roc-4.3.x/ drivers/gpu/drm/amd/include/v9_structs.h

Definition at line 77 of file pm4_defines.hh.

Member Data Documentation

◆ @101

| union { ... } |

◆ @111

| union { ... } |

◆ @113

| union { ... } |

◆ @119

| union { ... } |

◆ @123

| union { ... } |

◆ @127

| union { ... } |

◆ @131

| union { ... } |

◆ @133

| union { ... } |

◆ @143

| union { ... } |

◆ @147

| union { ... } |

◆ @149

| union { ... } |

◆ @151

| union { ... } |

◆ @161

| union { ... } |

◆ @163

| union { ... } |

◆ @165

| union { ... } |

◆ @167

| union { ... } |

◆ @169

| union { ... } |

◆ @171

| union { ... } |

◆ @173

| union { ... } |

◆ @175

| union { ... } |

◆ @177

| union { ... } |

◆ @189

| union { ... } |

◆ @191

| union { ... } |

◆ @193

| union { ... } |

◆ @209

| union { ... } |

◆ @213

| union { ... } |

◆ @217

| union { ... } |

◆ @221

| union { ... } |

◆ @225

| union { ... } |

◆ @227

| union { ... } |

◆ @233

| union { ... } |

◆ @235

| union { ... } |

◆ @237

| union { ... } |

◆ @245

| union { ... } |

◆ @249

| union { ... } |

◆ @253

| union { ... } |

◆ @255

| union { ... } |

◆ @257

| union { ... } |

◆ @259

| union { ... } |

◆ @269

| union { ... } |

◆ @53

| union { ... } |

◆ @57

| union { ... } |

◆ @61

| union { ... } |

◆ @63

| union { ... } |

◆ @69

| union { ... } |

◆ @75

| union { ... } |

◆ @77

| union { ... } |

◆ @83

| union { ... } |

◆ @85

| union { ... } |

◆ @87

| union { ... } |

◆ @95

| union { ... } |

◆ @97

| union { ... } |

◆ @99

| union { ... } |

◆ acqFenceScope

| uint16_t gem5::GEM5_PACKED::acqFenceScope |

Definition at line 368 of file sdma_packets.hh.

◆ action

| uint32_t gem5::GEM5_PACKED::action |

Definition at line 162 of file pm4_defines.hh.

◆ addr [1/2]

| Addr gem5::GEM5_PACKED::addr |

Definition at line 75 of file sdma_packets.hh.

◆ addr [2/2]

| uint64_t gem5::GEM5_PACKED::addr |

Definition at line 472 of file pm4_defines.hh.

Referenced by gem5::SDMAEngine::atomic(), gem5::SDMAEngine::atomicData(), gem5::SDMAEngine::atomicDone(), gem5::PM4PacketProcessor::queryStatus(), and gem5::PM4PacketProcessor::releaseMem().

◆ address

| uint64_t gem5::GEM5_PACKED::address |

Definition at line 210 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::pollRegMem(), and gem5::SDMAEngine::pollRegMemRead().

◆ addrHi

| uint32_t gem5::GEM5_PACKED::addrHi |

Definition at line 470 of file pm4_defines.hh.

◆ addrIncr

| uint32_t gem5::GEM5_PACKED::addrIncr |

Definition at line 100 of file pm4_defines.hh.

◆ addrLo

| uint32_t gem5::GEM5_PACKED::addrLo |

Definition at line 469 of file pm4_defines.hh.

◆ allocFormat

| uint32_t gem5::GEM5_PACKED::allocFormat |

Definition at line 132 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues().

◆ apertureId

| uint32_t gem5::GEM5_PACKED::apertureId |

Definition at line 196 of file sdma_packets.hh.

◆ aql

| uint32_t gem5::GEM5_PACKED::aql |

Definition at line 183 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::newQueue(), and gem5::PM4PacketProcessor::processMQD().

◆ aqlRptr

| uint64_t gem5::GEM5_PACKED::aqlRptr |

Definition at line 123 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::processMQD().

◆ barrier

| uint16_t gem5::GEM5_PACKED::barrier |

Definition at line 367 of file sdma_packets.hh.

◆ base

| uint64_t gem5::GEM5_PACKED::base |

Definition at line 109 of file pm4_queues.hh.

Referenced by gem5::PM4Queue::base(), gem5::SDMAEngine::indirectBuffer(), gem5::PM4PacketProcessor::newQueue(), gem5::PM4PacketProcessor::processMQD(), gem5::PM4Queue::rptr(), gem5::PM4PacketProcessor::unmapQueues(), gem5::PM4PacketProcessor::unserialize(), and gem5::PM4Queue::wptr().

◆ byteCount

| uint32_t gem5::GEM5_PACKED::byteCount |

Definition at line 360 of file sdma_packets.hh.

◆ byteEnable

| uint32_t gem5::GEM5_PACKED::byteEnable |

Definition at line 204 of file sdma_packets.hh.

◆ byteStride

| uint32_t gem5::GEM5_PACKED::byteStride |

Definition at line 349 of file sdma_packets.hh.

◆ cachePolicy

| uint32_t gem5::GEM5_PACKED::cachePolicy |

Definition at line 105 of file pm4_defines.hh.

◆ chain

| uint32_t gem5::GEM5_PACKED::chain |

Definition at line 384 of file pm4_defines.hh.

◆ checkDisable

| uint32_t gem5::GEM5_PACKED::checkDisable |

Definition at line 136 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues().

◆ cmpData

| uint64_t gem5::GEM5_PACKED::cmpData |

Definition at line 279 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::atomic().

◆ cmpDataHi

| uint32_t gem5::GEM5_PACKED::cmpDataHi |

Definition at line 277 of file sdma_packets.hh.

◆ cmpDataLo

| uint32_t gem5::GEM5_PACKED::cmpDataLo |

Definition at line 276 of file sdma_packets.hh.

◆ command

| uint32_t gem5::GEM5_PACKED::command |

Definition at line 435 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::queryStatus().

◆ completionSignal

| uint64_t gem5::GEM5_PACKED::completionSignal |

Definition at line 271 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapProcessGfx9(), and gem5::PM4PacketProcessor::mapProcessGfx90a().

◆ completionSignalHi

| uint32_t gem5::GEM5_PACKED::completionSignalHi |

Definition at line 269 of file pm4_defines.hh.

◆ completionSignalLo

| uint32_t gem5::GEM5_PACKED::completionSignalLo |

Definition at line 268 of file pm4_defines.hh.

◆ compSignal

| Addr gem5::GEM5_PACKED::compSignal |

Definition at line 422 of file sdma_packets.hh.

◆ compSignalHi

| uint32_t gem5::GEM5_PACKED::compSignalHi |

Definition at line 420 of file sdma_packets.hh.

◆ compSignalLo

| uint32_t gem5::GEM5_PACKED::compSignalLo |

Definition at line 419 of file sdma_packets.hh.

◆ contextId

| uint32_t gem5::GEM5_PACKED::contextId |

Definition at line 526 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::queryStatus().

◆ count [1/2]

| uint32_t gem5::GEM5_PACKED::count |

Definition at line 44 of file sdma_packets.hh.

◆ count [2/2]

| uint32_t gem5::GEM5_PACKED::count |

Definition at line 87 of file pm4_defines.hh.

Referenced by gem5::SDMAEngine::copy(), gem5::SDMAEngine::copyDone(), gem5::SDMAEngine::copyReadData(), gem5::SDMAEngine::ptePde(), gem5::SDMAEngine::ptePdeDone(), gem5::SDMAEngine::write(), gem5::SDMAEngine::writeDone(), and gem5::SDMAEngine::writeReadData().

◆ count0

| uint32_t gem5::GEM5_PACKED::count0 |

Definition at line 89 of file sdma_packets.hh.

◆ count1

| uint32_t gem5::GEM5_PACKED::count1 |

Definition at line 90 of file sdma_packets.hh.

◆ count2

| uint32_t gem5::GEM5_PACKED::count2 |

Definition at line 91 of file sdma_packets.hh.

◆ count3

| uint32_t gem5::GEM5_PACKED::count3 |

Definition at line 92 of file sdma_packets.hh.

◆ countData0

| uint32_t gem5::GEM5_PACKED::countData0 |

Definition at line 98 of file sdma_packets.hh.

◆ countData1

| uint32_t gem5::GEM5_PACKED::countData1 |

Definition at line 99 of file sdma_packets.hh.

◆ countData2

| uint32_t gem5::GEM5_PACKED::countData2 |

Definition at line 100 of file sdma_packets.hh.

◆ countData3

| uint32_t gem5::GEM5_PACKED::countData3 |

Definition at line 101 of file sdma_packets.hh.

◆ countKey0

| uint32_t gem5::GEM5_PACKED::countKey0 |

Definition at line 107 of file sdma_packets.hh.

◆ countKey1

| uint32_t gem5::GEM5_PACKED::countKey1 |

Definition at line 108 of file sdma_packets.hh.

◆ countKey2

| uint32_t gem5::GEM5_PACKED::countKey2 |

Definition at line 109 of file sdma_packets.hh.

◆ countKey3

| uint32_t gem5::GEM5_PACKED::countKey3 |

Definition at line 110 of file sdma_packets.hh.

◆ cp_hqd_aql_control

| uint32_t gem5::GEM5_PACKED::cp_hqd_aql_control |

Definition at line 182 of file pm4_queues.hh.

◆ cp_hqd_atomic0_preop_hi

| uint32_t gem5::GEM5_PACKED::cp_hqd_atomic0_preop_hi |

Definition at line 156 of file pm4_queues.hh.

◆ cp_hqd_atomic0_preop_lo

| uint32_t gem5::GEM5_PACKED::cp_hqd_atomic0_preop_lo |

Definition at line 155 of file pm4_queues.hh.

◆ cp_hqd_atomic1_preop_hi

| uint32_t gem5::GEM5_PACKED::cp_hqd_atomic1_preop_hi |

Definition at line 158 of file pm4_queues.hh.

◆ cp_hqd_atomic1_preop_lo

| uint32_t gem5::GEM5_PACKED::cp_hqd_atomic1_preop_lo |

Definition at line 157 of file pm4_queues.hh.

◆ cp_hqd_cntl_stack_offset

| uint32_t gem5::GEM5_PACKED::cp_hqd_cntl_stack_offset |

Definition at line 173 of file pm4_queues.hh.

◆ cp_hqd_cntl_stack_size

| uint32_t gem5::GEM5_PACKED::cp_hqd_cntl_stack_size |

Definition at line 174 of file pm4_queues.hh.

◆ cp_hqd_ctx_save_base_addr_hi

| uint32_t gem5::GEM5_PACKED::cp_hqd_ctx_save_base_addr_hi |

Definition at line 171 of file pm4_queues.hh.

◆ cp_hqd_ctx_save_base_addr_lo

| uint32_t gem5::GEM5_PACKED::cp_hqd_ctx_save_base_addr_lo |

Definition at line 170 of file pm4_queues.hh.

◆ cp_hqd_ctx_save_control

| uint32_t gem5::GEM5_PACKED::cp_hqd_ctx_save_control |

Definition at line 172 of file pm4_queues.hh.

◆ cp_hqd_ctx_save_size

| uint32_t gem5::GEM5_PACKED::cp_hqd_ctx_save_size |

Definition at line 176 of file pm4_queues.hh.

◆ cp_hqd_dequeue_request

| uint32_t gem5::GEM5_PACKED::cp_hqd_dequeue_request |

Definition at line 151 of file pm4_queues.hh.

◆ cp_hqd_dma_offload

| uint32_t gem5::GEM5_PACKED::cp_hqd_dma_offload |

Definition at line 152 of file pm4_queues.hh.

◆ cp_hqd_eop_base_addr_hi

| uint32_t gem5::GEM5_PACKED::cp_hqd_eop_base_addr_hi |

Definition at line 165 of file pm4_queues.hh.

◆ cp_hqd_eop_base_addr_lo

| uint32_t gem5::GEM5_PACKED::cp_hqd_eop_base_addr_lo |

Definition at line 164 of file pm4_queues.hh.

◆ cp_hqd_eop_control

| uint32_t gem5::GEM5_PACKED::cp_hqd_eop_control |

Definition at line 166 of file pm4_queues.hh.

◆ cp_hqd_eop_done_events

| uint32_t gem5::GEM5_PACKED::cp_hqd_eop_done_events |

Definition at line 169 of file pm4_queues.hh.

◆ cp_hqd_eop_rptr

| uint32_t gem5::GEM5_PACKED::cp_hqd_eop_rptr |

Definition at line 167 of file pm4_queues.hh.

◆ cp_hqd_eop_wptr

| uint32_t gem5::GEM5_PACKED::cp_hqd_eop_wptr |

Definition at line 168 of file pm4_queues.hh.

◆ cp_hqd_eop_wptr_mem

| uint32_t gem5::GEM5_PACKED::cp_hqd_eop_wptr_mem |

Definition at line 179 of file pm4_queues.hh.

◆ cp_hqd_error

| uint32_t gem5::GEM5_PACKED::cp_hqd_error |

Definition at line 178 of file pm4_queues.hh.

◆ cp_hqd_gds_resource_state

| uint32_t gem5::GEM5_PACKED::cp_hqd_gds_resource_state |

Definition at line 177 of file pm4_queues.hh.

◆ cp_hqd_hq_control0

| uint32_t gem5::GEM5_PACKED::cp_hqd_hq_control0 |

Definition at line 160 of file pm4_queues.hh.

◆ cp_hqd_hq_control1

| uint32_t gem5::GEM5_PACKED::cp_hqd_hq_control1 |

Definition at line 163 of file pm4_queues.hh.

◆ cp_hqd_hq_status0

| uint32_t gem5::GEM5_PACKED::cp_hqd_hq_status0 |

Definition at line 159 of file pm4_queues.hh.

◆ cp_hqd_hq_status1

| uint32_t gem5::GEM5_PACKED::cp_hqd_hq_status1 |

Definition at line 162 of file pm4_queues.hh.

◆ cp_hqd_msg_type

| uint32_t gem5::GEM5_PACKED::cp_hqd_msg_type |

Definition at line 154 of file pm4_queues.hh.

◆ cp_hqd_pq_wptr_hi

| uint32_t gem5::GEM5_PACKED::cp_hqd_pq_wptr_hi |

Definition at line 186 of file pm4_queues.hh.

◆ cp_hqd_pq_wptr_lo

| uint32_t gem5::GEM5_PACKED::cp_hqd_pq_wptr_lo |

Definition at line 185 of file pm4_queues.hh.

◆ cp_hqd_sema_cmd

| uint32_t gem5::GEM5_PACKED::cp_hqd_sema_cmd |

Definition at line 153 of file pm4_queues.hh.

◆ cp_hqd_wg_state_offset

| uint32_t gem5::GEM5_PACKED::cp_hqd_wg_state_offset |

Definition at line 175 of file pm4_queues.hh.

◆ cp_mqd_control

| uint32_t gem5::GEM5_PACKED::cp_mqd_control |

Definition at line 161 of file pm4_queues.hh.

◆ cp_mqd_readindex_hi

| uint32_t gem5::GEM5_PACKED::cp_mqd_readindex_hi |

Definition at line 53 of file pm4_queues.hh.

◆ cp_mqd_readindex_lo

| uint32_t gem5::GEM5_PACKED::cp_mqd_readindex_lo |

Definition at line 52 of file pm4_queues.hh.

◆ cp_mqd_restore_end_time_hi

| uint32_t gem5::GEM5_PACKED::cp_mqd_restore_end_time_hi |

Definition at line 64 of file pm4_queues.hh.

◆ cp_mqd_restore_end_time_lo

| uint32_t gem5::GEM5_PACKED::cp_mqd_restore_end_time_lo |

Definition at line 63 of file pm4_queues.hh.

◆ cp_mqd_restore_start_time_hi

| uint32_t gem5::GEM5_PACKED::cp_mqd_restore_start_time_hi |

Definition at line 62 of file pm4_queues.hh.

◆ cp_mqd_restore_start_time_lo

| uint32_t gem5::GEM5_PACKED::cp_mqd_restore_start_time_lo |

Definition at line 61 of file pm4_queues.hh.

◆ cp_mqd_save_end_time_hi

| uint32_t gem5::GEM5_PACKED::cp_mqd_save_end_time_hi |

Definition at line 60 of file pm4_queues.hh.

◆ cp_mqd_save_end_time_lo

| uint32_t gem5::GEM5_PACKED::cp_mqd_save_end_time_lo |

Definition at line 59 of file pm4_queues.hh.

◆ cp_mqd_save_start_time_hi

| uint32_t gem5::GEM5_PACKED::cp_mqd_save_start_time_hi |

Definition at line 58 of file pm4_queues.hh.

◆ cp_mqd_save_start_time_lo

| uint32_t gem5::GEM5_PACKED::cp_mqd_save_start_time_lo |

Definition at line 57 of file pm4_queues.hh.

◆ cp_packet_exe_status_hi

| uint32_t gem5::GEM5_PACKED::cp_packet_exe_status_hi |

Definition at line 78 of file pm4_queues.hh.

◆ cp_packet_exe_status_lo

| uint32_t gem5::GEM5_PACKED::cp_packet_exe_status_lo |

Definition at line 77 of file pm4_queues.hh.

◆ cp_packet_id_hi

| uint32_t gem5::GEM5_PACKED::cp_packet_id_hi |

Definition at line 76 of file pm4_queues.hh.

◆ cp_packet_id_lo

| uint32_t gem5::GEM5_PACKED::cp_packet_id_lo |

Definition at line 75 of file pm4_queues.hh.

◆ cp_pq_exe_status_hi

| uint32_t gem5::GEM5_PACKED::cp_pq_exe_status_hi |

Definition at line 74 of file pm4_queues.hh.

◆ cp_pq_exe_status_lo

| uint32_t gem5::GEM5_PACKED::cp_pq_exe_status_lo |

Definition at line 73 of file pm4_queues.hh.

◆ csaAddr

| uint64_t gem5::GEM5_PACKED::csaAddr |

Definition at line 126 of file sdma_packets.hh.

◆ ctx_save_base_addr_hi

| uint32_t gem5::GEM5_PACKED::ctx_save_base_addr_hi |

Definition at line 84 of file pm4_queues.hh.

◆ ctx_save_base_addr_lo

| uint32_t gem5::GEM5_PACKED::ctx_save_base_addr_lo |

Definition at line 83 of file pm4_queues.hh.

◆ data [1/2]

| uint32_t gem5::GEM5_PACKED::data |

Definition at line 116 of file pm4_defines.hh.

Referenced by gem5::SDMAEngine::fence(), gem5::SDMAEngine::fenceDone(), gem5::PM4PacketProcessor::queryStatus(), gem5::PM4PacketProcessor::setUconfigReg(), gem5::SDMAEngine::srbmWrite(), gem5::PM4PacketProcessor::writeData(), and gem5::PM4PacketProcessor::writeDataDone().

◆ data [2/2]

| uint64_t gem5::GEM5_PACKED::data |

Definition at line 489 of file pm4_defines.hh.

◆ dataHi

| uint32_t gem5::GEM5_PACKED::dataHi |

Definition at line 487 of file pm4_defines.hh.

◆ dataLo

| uint32_t gem5::GEM5_PACKED::dataLo |

Definition at line 485 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::releaseMem(), and gem5::PM4PacketProcessor::releaseMemDone().

◆ dataSelect

| uint32_t gem5::GEM5_PACKED::dataSelect |

Definition at line 464 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::releaseMem().

◆ ddw

| uint32_t gem5::GEM5_PACKED::ddw |

Definition at line 49 of file sdma_packets.hh.

◆ depSignal0

| Addr gem5::GEM5_PACKED::depSignal0 |

Definition at line 432 of file sdma_packets.hh.

◆ depSignal1

| Addr gem5::GEM5_PACKED::depSignal1 |

Definition at line 433 of file sdma_packets.hh.

◆ depSignal2

| Addr gem5::GEM5_PACKED::depSignal2 |

Definition at line 434 of file sdma_packets.hh.

◆ depSignal3

| Addr gem5::GEM5_PACKED::depSignal3 |

Definition at line 435 of file sdma_packets.hh.

◆ depSignal4

| Addr gem5::GEM5_PACKED::depSignal4 |

Definition at line 436 of file sdma_packets.hh.

◆ dest [1/2]

| uint64_t gem5::GEM5_PACKED::dest |

Definition at line 52 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::copy(), gem5::SDMAEngine::copyDone(), gem5::SDMAEngine::copyReadData(), gem5::SDMAEngine::fence(), gem5::SDMAEngine::fenceDone(), gem5::SDMAEngine::ptePde(), gem5::SDMAEngine::ptePdeDone(), gem5::SDMAEngine::write(), gem5::SDMAEngine::writeDone(), and gem5::SDMAEngine::writeReadData().

◆ dest [2/2]

| Addr gem5::GEM5_PACKED::dest |

Definition at line 411 of file sdma_packets.hh.

◆ destAddr

| uint64_t gem5::GEM5_PACKED::destAddr |

Definition at line 114 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::writeData().

◆ destAddrHi

| uint32_t gem5::GEM5_PACKED::destAddrHi |

Definition at line 112 of file pm4_defines.hh.

◆ destAddrLo

| uint32_t gem5::GEM5_PACKED::destAddrLo |

Definition at line 111 of file pm4_defines.hh.

◆ destHi

| uint32_t gem5::GEM5_PACKED::destHi |

Definition at line 356 of file sdma_packets.hh.

◆ destLo

| uint32_t gem5::GEM5_PACKED::destLo |

Definition at line 355 of file sdma_packets.hh.

◆ destSel

| uint32_t gem5::GEM5_PACKED::destSel |

Definition at line 98 of file pm4_defines.hh.

◆ destSelect

| uint32_t gem5::GEM5_PACKED::destSelect |

Definition at line 460 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::releaseMem().

◆ device

| uint32_t gem5::GEM5_PACKED::device |

Definition at line 333 of file sdma_packets.hh.

◆ diq

| uint32_t gem5::GEM5_PACKED::diq |

Definition at line 231 of file pm4_defines.hh.

◆ disable_queue

| uint32_t gem5::GEM5_PACKED::disable_queue |

Definition at line 65 of file pm4_queues.hh.

◆ dmaCount

| uint32_t gem5::GEM5_PACKED::dmaCount |

Definition at line 350 of file sdma_packets.hh.

◆ doorbell

| uint32_t gem5::GEM5_PACKED::doorbell |

Definition at line 130 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::getKiqDoorbellOffset(), and gem5::PM4PacketProcessor::processMQD().

◆ doorbellOffset

| uint32_t gem5::GEM5_PACKED::doorbellOffset |

Definition at line 137 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues(), gem5::PM4PacketProcessor::processSDMAMQD(), and gem5::PM4PacketProcessor::queryStatus().

◆ doorbellOffset0

| uint32_t gem5::GEM5_PACKED::doorbellOffset0 |

Definition at line 178 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::unmapQueues().

◆ doorbellOffset1

| uint32_t gem5::GEM5_PACKED::doorbellOffset1 |

Definition at line 183 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::unmapQueues().

◆ doorbellOffset2

| uint32_t gem5::GEM5_PACKED::doorbellOffset2 |

Definition at line 186 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::unmapQueues().

◆ doorbellOffset3

| uint32_t gem5::GEM5_PACKED::doorbellOffset3 |

Definition at line 189 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::unmapQueues().

◆ dummy

| uint32_t gem5::GEM5_PACKED::dummy |

Definition at line 404 of file pm4_defines.hh.

◆ dwOffset

| uint32_t gem5::GEM5_PACKED::dwOffset |

Definition at line 482 of file pm4_defines.hh.

◆ dynamic_cu_mask_addr_hi

| uint32_t gem5::GEM5_PACKED::dynamic_cu_mask_addr_hi |

Definition at line 86 of file pm4_queues.hh.

◆ dynamic_cu_mask_addr_lo

| uint32_t gem5::GEM5_PACKED::dynamic_cu_mask_addr_lo |

Definition at line 85 of file pm4_queues.hh.

◆ ena

| uint32_t gem5::GEM5_PACKED::ena |

Definition at line 422 of file pm4_defines.hh.

◆ engineSel

| uint32_t gem5::GEM5_PACKED::engineSel |

Definition at line 133 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues(), gem5::PM4PacketProcessor::processSDMAMQD(), and gem5::PM4PacketProcessor::queryStatus().

◆ event

| uint32_t gem5::GEM5_PACKED::event |

Definition at line 441 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::releaseMem().

◆ eventIdx

| uint32_t gem5::GEM5_PACKED::eventIdx |

Definition at line 443 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::releaseMem().

◆ execCount

| uint32_t gem5::GEM5_PACKED::execCount |

Definition at line 244 of file sdma_packets.hh.

◆ execute

| uint32_t gem5::GEM5_PACKED::execute |

Definition at line 457 of file pm4_defines.hh.

◆ format

| uint16_t gem5::GEM5_PACKED::format |

Definition at line 366 of file sdma_packets.hh.

◆ func

| uint32_t gem5::GEM5_PACKED::func |

Definition at line 223 of file sdma_packets.hh.

◆ function

| uint32_t gem5::GEM5_PACKED::function |

Definition at line 336 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::waitRegMem().

◆ gds_cs_ctxsw_cnt0

| uint32_t gem5::GEM5_PACKED::gds_cs_ctxsw_cnt0 |

Definition at line 67 of file pm4_queues.hh.

◆ gds_cs_ctxsw_cnt1

| uint32_t gem5::GEM5_PACKED::gds_cs_ctxsw_cnt1 |

Definition at line 68 of file pm4_queues.hh.

◆ gds_cs_ctxsw_cnt2

| uint32_t gem5::GEM5_PACKED::gds_cs_ctxsw_cnt2 |

Definition at line 69 of file pm4_queues.hh.

◆ gds_cs_ctxsw_cnt3

| uint32_t gem5::GEM5_PACKED::gds_cs_ctxsw_cnt3 |

Definition at line 70 of file pm4_queues.hh.

◆ gds_save_base_addr_hi

| uint32_t gem5::GEM5_PACKED::gds_save_base_addr_hi |

Definition at line 80 of file pm4_queues.hh.

◆ gds_save_base_addr_lo

| uint32_t gem5::GEM5_PACKED::gds_save_base_addr_lo |

Definition at line 79 of file pm4_queues.hh.

◆ gds_save_mask_hi

| uint32_t gem5::GEM5_PACKED::gds_save_mask_hi |

Definition at line 82 of file pm4_queues.hh.

◆ gds_save_mask_lo

| uint32_t gem5::GEM5_PACKED::gds_save_mask_lo |

Definition at line 81 of file pm4_queues.hh.

◆ gdsAddr

| uint64_t gem5::GEM5_PACKED::gdsAddr |

Definition at line 256 of file pm4_defines.hh.

◆ gdsAddrHi

| uint32_t gem5::GEM5_PACKED::gdsAddrHi |

Definition at line 254 of file pm4_defines.hh.

◆ gdsAddrLo

| uint32_t gem5::GEM5_PACKED::gdsAddrLo |

Definition at line 253 of file pm4_defines.hh.

◆ gdsHeapBase

| uint32_t gem5::GEM5_PACKED::gdsHeapBase |

Definition at line 220 of file pm4_defines.hh.

◆ gdsHeapSize

| uint32_t gem5::GEM5_PACKED::gdsHeapSize |

Definition at line 222 of file pm4_defines.hh.

◆ gdsSize

| uint32_t gem5::GEM5_PACKED::gdsSize |

Definition at line 262 of file pm4_defines.hh.

◆ gwsMask

| uint64_t gem5::GEM5_PACKED::gwsMask |

Definition at line 216 of file pm4_defines.hh.

◆ gwsMaskHi

| uint32_t gem5::GEM5_PACKED::gwsMaskHi |

Definition at line 214 of file pm4_defines.hh.

◆ gwsMaskLo

| uint32_t gem5::GEM5_PACKED::gwsMaskLo |

Definition at line 213 of file pm4_defines.hh.

◆ header

| sdmaHeaderAgentDisp gem5::GEM5_PACKED::header |

Definition at line 376 of file sdma_packets.hh.

◆ hqd_active

| uint32_t gem5::GEM5_PACKED::hqd_active |

Definition at line 96 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::processMQD(), and gem5::PM4PacketProcessor::setHqdActive().

◆ hqd_ib_base_addr_hi

| uint32_t gem5::GEM5_PACKED::hqd_ib_base_addr_hi |

Definition at line 139 of file pm4_queues.hh.

◆ hqd_ib_base_addr_lo

| uint32_t gem5::GEM5_PACKED::hqd_ib_base_addr_lo |

Definition at line 138 of file pm4_queues.hh.

◆ hqd_ib_control

| uint32_t gem5::GEM5_PACKED::hqd_ib_control |

Definition at line 148 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdIbCtrl().

◆ hqd_ib_rptr

| uint32_t gem5::GEM5_PACKED::hqd_ib_rptr |

Definition at line 145 of file pm4_queues.hh.

◆ hqd_iq_rptr

| uint32_t gem5::GEM5_PACKED::hqd_iq_rptr |

Definition at line 150 of file pm4_queues.hh.

◆ hqd_iq_timer

| uint32_t gem5::GEM5_PACKED::hqd_iq_timer |

Definition at line 149 of file pm4_queues.hh.

◆ hqd_persistent_state

| uint32_t gem5::GEM5_PACKED::hqd_persistent_state |

Definition at line 98 of file pm4_queues.hh.

◆ hqd_pipe_priority

| uint32_t gem5::GEM5_PACKED::hqd_pipe_priority |

Definition at line 99 of file pm4_queues.hh.

◆ hqd_pq_base_hi

| uint32_t gem5::GEM5_PACKED::hqd_pq_base_hi |

Definition at line 107 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdPqBaseHi(), and gem5::PM4PacketProcessor::setRbBaseHi().

◆ hqd_pq_base_lo

| uint32_t gem5::GEM5_PACKED::hqd_pq_base_lo |

Definition at line 106 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdPqBase(), and gem5::PM4PacketProcessor::setRbBaseLo().

◆ hqd_pq_control

| uint32_t gem5::GEM5_PACKED::hqd_pq_control |

Definition at line 133 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::processMQD(), gem5::PM4PacketProcessor::setHqdPqControl(), gem5::PM4PacketProcessor::setRbCntl(), and gem5::PM4Queue::size().

◆ hqd_pq_doorbell_control

| uint32_t gem5::GEM5_PACKED::hqd_pq_doorbell_control |

Definition at line 129 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdPqDoorbellCtrl(), and gem5::PM4PacketProcessor::setRbDoorbellCntrl().

◆ hqd_pq_rptr

| uint32_t gem5::GEM5_PACKED::hqd_pq_rptr |

Definition at line 113 of file pm4_queues.hh.

◆ hqd_pq_rptr_report_addr_hi

| uint32_t gem5::GEM5_PACKED::hqd_pq_rptr_report_addr_hi |

Definition at line 121 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdPqRptrReportAddrHi().

◆ hqd_pq_rptr_report_addr_lo

| uint32_t gem5::GEM5_PACKED::hqd_pq_rptr_report_addr_lo |

Definition at line 120 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdPqRptrReportAddr().

◆ hqd_pq_wptr_poll_addr_hi

| uint32_t gem5::GEM5_PACKED::hqd_pq_wptr_poll_addr_hi |

Definition at line 126 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdPqWptrPollAddrHi(), and gem5::PM4PacketProcessor::setRbWptrPollAddrHi().

◆ hqd_pq_wptr_poll_addr_lo

| uint32_t gem5::GEM5_PACKED::hqd_pq_wptr_poll_addr_lo |

Definition at line 125 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::setHqdPqWptrPollAddr(), and gem5::PM4PacketProcessor::setRbWptrPollAddrLo().

◆ hqd_quantum

| uint32_t gem5::GEM5_PACKED::hqd_quantum |

Definition at line 101 of file pm4_queues.hh.

◆ hqd_queue_priority

| uint32_t gem5::GEM5_PACKED::hqd_queue_priority |

Definition at line 100 of file pm4_queues.hh.

◆ hqd_vmid

| uint32_t gem5::GEM5_PACKED::hqd_vmid |

Definition at line 97 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::processMQD(), gem5::PM4PacketProcessor::setHqdVmid(), and gem5::PM4PacketProcessor::setRbVmid().

◆ ibBase [1/2]

| Addr gem5::GEM5_PACKED::ibBase |

Definition at line 141 of file pm4_queues.hh.

◆ ibBase [2/2]

| uint64_t gem5::GEM5_PACKED::ibBase |

Definition at line 381 of file pm4_defines.hh.

Referenced by gem5::PM4Queue::ibBase(), gem5::PM4PacketProcessor::indirectBuffer(), gem5::PM4Queue::rptr(), gem5::PM4PacketProcessor::runList(), gem5::PM4PacketProcessor::unserialize(), and gem5::PM4Queue::wptr().

◆ ibBaseHi

| uint32_t gem5::GEM5_PACKED::ibBaseHi |

Definition at line 379 of file pm4_defines.hh.

◆ ibBaseLo

| uint32_t gem5::GEM5_PACKED::ibBaseLo |

Definition at line 378 of file pm4_defines.hh.

◆ ibOffset

| uint32_t gem5::GEM5_PACKED::ibOffset |

Definition at line 154 of file sdma_packets.hh.

◆ ibRptr

| uint32_t gem5::GEM5_PACKED::ibRptr |

Definition at line 146 of file pm4_queues.hh.

Referenced by gem5::PM4Queue::fastforwardRptr(), gem5::PM4Queue::getRptr(), gem5::PM4Queue::incRptr(), gem5::PM4Queue::rptr(), and gem5::PM4PacketProcessor::unserialize().

◆ ibSize

| uint32_t gem5::GEM5_PACKED::ibSize |

Definition at line 383 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::indirectBuffer(), and gem5::PM4PacketProcessor::runList().

◆ increment

| uint64_t gem5::GEM5_PACKED::increment |

Definition at line 302 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::ptePde().

◆ initData

| uint64_t gem5::GEM5_PACKED::initData |

Definition at line 317 of file sdma_packets.hh.

◆ initDataHi

| uint32_t gem5::GEM5_PACKED::initDataHi |

Definition at line 315 of file sdma_packets.hh.

◆ initDataLo

| uint32_t gem5::GEM5_PACKED::initDataLo |

Definition at line 314 of file sdma_packets.hh.

◆ initValue

| uint64_t gem5::GEM5_PACKED::initValue |

Definition at line 301 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::ptePde().

◆ intCtxId

| uint32_t gem5::GEM5_PACKED::intCtxId |

Definition at line 491 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::releaseMem(), and gem5::PM4PacketProcessor::releaseMemDone().

◆ interruptSel

| uint32_t gem5::GEM5_PACKED::interruptSel |

Definition at line 527 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::queryStatus().

◆ intrContext

| uint32_t gem5::GEM5_PACKED::intrContext |

Definition at line 157 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::trap().

◆ intSelect

| uint32_t gem5::GEM5_PACKED::intSelect |

Definition at line 462 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::releaseMem(), and gem5::PM4PacketProcessor::releaseMemDone().

◆ key0

| uint32_t gem5::GEM5_PACKED::key0 |

Definition at line 85 of file sdma_packets.hh.

◆ key1

| uint32_t gem5::GEM5_PACKED::key1 |

Definition at line 86 of file sdma_packets.hh.

◆ key2

| uint32_t gem5::GEM5_PACKED::key2 |

Definition at line 87 of file sdma_packets.hh.

◆ key3

| uint32_t gem5::GEM5_PACKED::key3 |

Definition at line 88 of file sdma_packets.hh.

◆ l1Inv

| uint32_t gem5::GEM5_PACKED::l1Inv |

Definition at line 448 of file pm4_defines.hh.

◆ l1Volatile

| uint32_t gem5::GEM5_PACKED::l1Volatile |

Definition at line 444 of file pm4_defines.hh.

◆ l2Inv

| uint32_t gem5::GEM5_PACKED::l2Inv |

Definition at line 449 of file pm4_defines.hh.

◆ l2Meta

| uint32_t gem5::GEM5_PACKED::l2Meta |

Definition at line 453 of file pm4_defines.hh.

◆ l2NC

| uint32_t gem5::GEM5_PACKED::l2NC |

Definition at line 451 of file pm4_defines.hh.

◆ l2Volatile

| uint32_t gem5::GEM5_PACKED::l2Volatile |

Definition at line 445 of file pm4_defines.hh.

◆ l2WB

| uint32_t gem5::GEM5_PACKED::l2WB |

Definition at line 447 of file pm4_defines.hh.

◆ l2WC

| uint32_t gem5::GEM5_PACKED::l2WC |

Definition at line 452 of file pm4_defines.hh.

◆ loop

| int gem5::GEM5_PACKED::loop |

Definition at line 289 of file sdma_packets.hh.

◆ loopInt

| uint32_t gem5::GEM5_PACKED::loopInt |

Definition at line 281 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::atomic().

◆ mask [1/2]

| uint64_t gem5::GEM5_PACKED::mask |

Definition at line 300 of file sdma_packets.hh.

◆ mask [2/2]

| uint32_t gem5::GEM5_PACKED::mask |

Definition at line 359 of file pm4_defines.hh.

Referenced by gem5::SDMAEngine::pollRegMem(), gem5::SDMAEngine::ptePde(), and gem5::PM4PacketProcessor::waitRegMem().

◆ me

| uint32_t gem5::GEM5_PACKED::me |

Definition at line 129 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues(), gem5::PM4Queue::me(), and gem5::PM4Queue::setPkt().

◆ memAddrHi

| uint32_t gem5::GEM5_PACKED::memAddrHi |

Definition at line 356 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::waitRegMem().

◆ memAddrLo

| uint32_t gem5::GEM5_PACKED::memAddrLo |

Definition at line 347 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::waitRegMem().

◆ memSpace

| uint32_t gem5::GEM5_PACKED::memSpace |

Definition at line 337 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::waitRegMem().

◆ mode

| uint32_t gem5::GEM5_PACKED::mode |

Definition at line 224 of file sdma_packets.hh.

◆ mqd_base_addr_hi

| uint32_t gem5::GEM5_PACKED::mqd_base_addr_hi |

Definition at line 92 of file pm4_queues.hh.

◆ mqd_base_addr_lo

| uint32_t gem5::GEM5_PACKED::mqd_base_addr_lo |

Definition at line 91 of file pm4_queues.hh.

◆ mqdAddr

| uint64_t gem5::GEM5_PACKED::mqdAddr |

Definition at line 146 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues().

◆ mqdAddrHi

| uint32_t gem5::GEM5_PACKED::mqdAddrHi |

Definition at line 144 of file pm4_defines.hh.

◆ mqdAddrLo

| uint32_t gem5::GEM5_PACKED::mqdAddrLo |

Definition at line 143 of file pm4_defines.hh.

◆ mqdBase

| uint64_t gem5::GEM5_PACKED::mqdBase |

Definition at line 94 of file pm4_queues.hh.

Referenced by gem5::PM4Queue::mqdBase(), gem5::PM4PacketProcessor::processMQD(), and gem5::PM4PacketProcessor::unserialize().

◆ mqdReadIndex

| uint64_t gem5::GEM5_PACKED::mqdReadIndex |

Definition at line 55 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::processMQD(), and gem5::PM4PacketProcessor::unmapQueues().

◆ numDws

| uint32_t gem5::GEM5_PACKED::numDws |

Definition at line 483 of file pm4_defines.hh.

◆ numGws

| uint32_t gem5::GEM5_PACKED::numGws |

Definition at line 258 of file pm4_defines.hh.

◆ numOac

| uint32_t gem5::GEM5_PACKED::numOac |

Definition at line 260 of file pm4_defines.hh.

◆ numQueues

| uint32_t gem5::GEM5_PACKED::numQueues |

Definition at line 134 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues(), and gem5::PM4PacketProcessor::unmapQueues().

◆ oacMask

| uint16_t gem5::GEM5_PACKED::oacMask |

Definition at line 218 of file pm4_defines.hh.

◆ offleadPolling

| uint32_t gem5::GEM5_PACKED::offleadPolling |

Definition at line 516 of file pm4_defines.hh.

◆ offset

| uint32_t gem5::GEM5_PACKED::offset |

Definition at line 497 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::setUconfigReg().

◆ op

| uint32_t gem5::GEM5_PACKED::op |

Definition at line 222 of file sdma_packets.hh.

◆ opcode [1/3]

| uint16_t gem5::GEM5_PACKED::opcode |

Definition at line 86 of file pm4_defines.hh.

◆ opcode [2/3]

| int gem5::GEM5_PACKED::opcode |

Definition at line 291 of file sdma_packets.hh.

◆ opcode [3/3]

| uint32_t gem5::GEM5_PACKED::opcode |

Definition at line 331 of file sdma_packets.hh.

◆ operation

| uint32_t gem5::GEM5_PACKED::operation |

Definition at line 338 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::waitRegMem().

◆ ordinal

| uint32_t gem5::GEM5_PACKED::ordinal |

Definition at line 90 of file pm4_defines.hh.

◆ ordinal14

| uint32_t gem5::GEM5_PACKED::ordinal14 |

Definition at line 318 of file pm4_defines.hh.

◆ pasid

| uint32_t gem5::GEM5_PACKED::pasid |

Definition at line 172 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapProcessGfx9(), gem5::PM4PacketProcessor::mapProcessGfx90a(), gem5::PM4PacketProcessor::queryStatus(), and gem5::PM4PacketProcessor::unmapQueues().

◆ pipe

| uint32_t gem5::GEM5_PACKED::pipe |

Definition at line 128 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues(), gem5::PM4Queue::pipe(), and gem5::PM4Queue::setPkt().

◆ poll

| uint32_t gem5::GEM5_PACKED::poll |

Definition at line 385 of file pm4_defines.hh.

◆ pollInt

| uint32_t gem5::GEM5_PACKED::pollInt |

Definition at line 213 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::pollRegMem().

◆ pollInterval

| uint32_t gem5::GEM5_PACKED::pollInterval |

Definition at line 360 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::waitRegMem().

◆ predicated

| uint16_t gem5::GEM5_PACKED::predicated |

Definition at line 83 of file pm4_defines.hh.

◆ preResume

| uint32_t gem5::GEM5_PACKED::preResume |

Definition at line 426 of file pm4_defines.hh.

◆ priv

| uint32_t gem5::GEM5_PACKED::priv |

Definition at line 391 of file pm4_defines.hh.

◆ processCnt

| uint32_t gem5::GEM5_PACKED::processCnt |

Definition at line 519 of file pm4_defines.hh.

◆ processQuantum

| uint32_t gem5::GEM5_PACKED::processQuantum |

Definition at line 232 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapProcessGfx9(), and gem5::PM4PacketProcessor::mapProcessGfx90a().

◆ ptBase

| uint64_t gem5::GEM5_PACKED::ptBase |

Definition at line 240 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapProcessGfx9(), and gem5::PM4PacketProcessor::mapProcessGfx90a().

◆ ptBaseHi

| uint32_t gem5::GEM5_PACKED::ptBaseHi |

Definition at line 238 of file pm4_defines.hh.

◆ ptBaseLo

| uint32_t gem5::GEM5_PACKED::ptBaseLo |

Definition at line 237 of file pm4_defines.hh.

◆ queueMask

| uint64_t gem5::GEM5_PACKED::queueMask |

Definition at line 207 of file pm4_defines.hh.

◆ queueMaskHi

| uint32_t gem5::GEM5_PACKED::queueMaskHi |

Definition at line 205 of file pm4_defines.hh.

◆ queueMaskLo

| uint32_t gem5::GEM5_PACKED::queueMaskLo |

Definition at line 204 of file pm4_defines.hh.

◆ queueSel

| uint32_t gem5::GEM5_PACKED::queueSel |

Definition at line 123 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues(), gem5::PM4Queue::privileged(), gem5::PM4Queue::setPkt(), and gem5::PM4PacketProcessor::unmapQueues().

◆ queueSlot

| uint32_t gem5::GEM5_PACKED::queueSlot |

Definition at line 127 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues(), gem5::PM4Queue::queue(), and gem5::PM4Queue::setPkt().

◆ queueType

| uint32_t gem5::GEM5_PACKED::queueType |

Definition at line 131 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::mapQueues().

◆ rb_base

| uint64_t gem5::GEM5_PACKED::rb_base |

Definition at line 204 of file pm4_queues.hh.

Referenced by gem5::PM4PacketProcessor::processSDMAMQD(), and gem5::SDMAEngine::registerRLCQueue().

◆ rbRptr

| uint32_t gem5::GEM5_PACKED::rbRptr |

Definition at line 153 of file sdma_packets.hh.

◆ ref

| uint32_t gem5::GEM5_PACKED::ref |

Definition at line 211 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::pollRegMem(), and gem5::SDMAEngine::pollRegMemRead().

◆ reference

| uint32_t gem5::GEM5_PACKED::reference |

Definition at line 358 of file pm4_defines.hh.

Referenced by gem5::PM4PacketProcessor::waitRegMem().

◆ regAddr

| uint32_t gem5::GEM5_PACKED::regAddr |

Definition at line 194 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::srbmWrite().

◆ regAddr1

| uint32_t gem5::GEM5_PACKED::regAddr1 |

Definition at line 344 of file pm4_defines.hh.

◆ regAddr2

| uint32_t gem5::GEM5_PACKED::regAddr2 |

Definition at line 353 of file pm4_defines.hh.

◆ regData

| uint32_t gem5::GEM5_PACKED::regData |

Definition at line 368 of file pm4_defines.hh.

◆ regOffset

| uint32_t gem5::GEM5_PACKED::regOffset |

Definition at line 366 of file pm4_defines.hh.

◆ relFenceScope

| uint16_t gem5::GEM5_PACKED::relFenceScope |

Definition at line 369 of file sdma_packets.hh.

◆ res0 [1/2]

| uint16_t gem5::GEM5_PACKED::res0 |

Definition at line 45 of file sdma_packets.hh.

◆ res0 [2/2]

| uint16_t gem5::GEM5_PACKED::res0 |

Definition at line 377 of file sdma_packets.hh.

◆ res1

| uint32_t gem5::GEM5_PACKED::res1 |

Definition at line 46 of file sdma_packets.hh.

◆ res2 [1/2]

| uint32_t gem5::GEM5_PACKED::res2 |

Definition at line 48 of file sdma_packets.hh.

◆ res2 [2/2]

| uint64_t gem5::GEM5_PACKED::res2 |

Definition at line 437 of file sdma_packets.hh.

◆ res3

| uint32_t gem5::GEM5_PACKED::res3 |

Definition at line 50 of file sdma_packets.hh.

◆ res4

| uint32_t gem5::GEM5_PACKED::res4 |

Definition at line 392 of file sdma_packets.hh.

◆ res5

| uint64_t gem5::GEM5_PACKED::res5 |

Definition at line 413 of file sdma_packets.hh.

◆ res6

| uint64_t gem5::GEM5_PACKED::res6 |

Definition at line 414 of file sdma_packets.hh.

◆ reserved [1/2]

| uint16_t gem5::GEM5_PACKED::reserved |

Definition at line 85 of file pm4_defines.hh.

◆ reserved [2/2]

| uint32_t gem5::GEM5_PACKED::reserved |

Definition at line 163 of file pm4_defines.hh.

◆ reserved0

| uint32_t gem5::GEM5_PACKED::reserved0 |

Definition at line 230 of file pm4_defines.hh.

◆ reserved1 [1/2]

| uint32_t gem5::GEM5_PACKED::reserved1 |

Definition at line 97 of file pm4_defines.hh.

◆ reserved1 [2/2]

| uint16_t gem5::GEM5_PACKED::reserved1 |

Definition at line 219 of file pm4_defines.hh.

◆ reserved10

| uint32_t gem5::GEM5_PACKED::reserved10 |

Definition at line 190 of file pm4_defines.hh.

◆ reserved2

| uint32_t gem5::GEM5_PACKED::reserved2 |

Definition at line 99 of file pm4_defines.hh.

◆ reserved3

| uint32_t gem5::GEM5_PACKED::reserved3 |

Definition at line 101 of file pm4_defines.hh.

◆ reserved4

| uint32_t gem5::GEM5_PACKED::reserved4 |

Definition at line 104 of file pm4_defines.hh.

◆ reserved5

| uint32_t gem5::GEM5_PACKED::reserved5 |

Definition at line 106 of file pm4_defines.hh.

◆ reserved6

| uint32_t gem5::GEM5_PACKED::reserved6 |

Definition at line 130 of file pm4_defines.hh.

◆ reserved7

| uint32_t gem5::GEM5_PACKED::reserved7 |

Definition at line 185 of file pm4_defines.hh.

◆ reserved8

| uint32_t gem5::GEM5_PACKED::reserved8 |

Definition at line 187 of file pm4_defines.hh.

◆ reserved9

| uint32_t gem5::GEM5_PACKED::reserved9 |

Definition at line 188 of file pm4_defines.hh.

◆ reserved_100

| uint32_t gem5::GEM5_PACKED::reserved_100 |

Definition at line 317 of file pm4_queues.hh.

◆ reserved_101

| uint32_t gem5::GEM5_PACKED::reserved_101 |

Definition at line 318 of file pm4_queues.hh.

◆ reserved_102

| uint32_t gem5::GEM5_PACKED::reserved_102 |

Definition at line 319 of file pm4_queues.hh.

◆ reserved_103

| uint32_t gem5::GEM5_PACKED::reserved_103 |

Definition at line 320 of file pm4_queues.hh.

◆ reserved_104

| uint32_t gem5::GEM5_PACKED::reserved_104 |

Definition at line 321 of file pm4_queues.hh.

◆ reserved_105

| uint32_t gem5::GEM5_PACKED::reserved_105 |

Definition at line 322 of file pm4_queues.hh.

◆ reserved_106

| uint32_t gem5::GEM5_PACKED::reserved_106 |

Definition at line 323 of file pm4_queues.hh.

◆ reserved_107

| uint32_t gem5::GEM5_PACKED::reserved_107 |

Definition at line 66 of file pm4_queues.hh.

◆ reserved_108

| uint32_t gem5::GEM5_PACKED::reserved_108 |

Definition at line 325 of file pm4_queues.hh.

◆ reserved_109

| uint32_t gem5::GEM5_PACKED::reserved_109 |

Definition at line 326 of file pm4_queues.hh.

◆ reserved_110

| uint32_t gem5::GEM5_PACKED::reserved_110 |

Definition at line 327 of file pm4_queues.hh.

◆ reserved_111

| uint32_t gem5::GEM5_PACKED::reserved_111 |

Definition at line 328 of file pm4_queues.hh.

◆ reserved_112

| uint32_t gem5::GEM5_PACKED::reserved_112 |

Definition at line 71 of file pm4_queues.hh.

◆ reserved_113

| uint32_t gem5::GEM5_PACKED::reserved_113 |

Definition at line 72 of file pm4_queues.hh.

◆ reserved_114

| uint32_t gem5::GEM5_PACKED::reserved_114 |

Definition at line 331 of file pm4_queues.hh.

◆ reserved_115

| uint32_t gem5::GEM5_PACKED::reserved_115 |

Definition at line 332 of file pm4_queues.hh.

◆ reserved_116

| uint32_t gem5::GEM5_PACKED::reserved_116 |

Definition at line 333 of file pm4_queues.hh.

◆ reserved_117

| uint32_t gem5::GEM5_PACKED::reserved_117 |

Definition at line 334 of file pm4_queues.hh.

◆ reserved_118

| uint32_t gem5::GEM5_PACKED::reserved_118 |

Definition at line 335 of file pm4_queues.hh.

◆ reserved_119

| uint32_t gem5::GEM5_PACKED::reserved_119 |

Definition at line 336 of file pm4_queues.hh.

◆ reserved_120

| uint32_t gem5::GEM5_PACKED::reserved_120 |

Definition at line 337 of file pm4_queues.hh.

◆ reserved_121

| uint32_t gem5::GEM5_PACKED::reserved_121 |

Definition at line 338 of file pm4_queues.hh.

◆ reserved_122

| uint32_t gem5::GEM5_PACKED::reserved_122 |

Definition at line 339 of file pm4_queues.hh.

◆ reserved_123

| uint32_t gem5::GEM5_PACKED::reserved_123 |

Definition at line 340 of file pm4_queues.hh.

◆ reserved_124

| uint32_t gem5::GEM5_PACKED::reserved_124 |

Definition at line 341 of file pm4_queues.hh.

◆ reserved_125

| uint32_t gem5::GEM5_PACKED::reserved_125 |

Definition at line 342 of file pm4_queues.hh.

◆ reserved_144

| uint32_t gem5::GEM5_PACKED::reserved_144 |

Definition at line 132 of file pm4_queues.hh.

◆ reserved_42

| uint32_t gem5::GEM5_PACKED::reserved_42 |

Definition at line 259 of file pm4_queues.hh.

◆ reserved_43

| uint32_t gem5::GEM5_PACKED::reserved_43 |

Definition at line 260 of file pm4_queues.hh.

◆ reserved_44

| uint32_t gem5::GEM5_PACKED::reserved_44 |

Definition at line 261 of file pm4_queues.hh.

◆ reserved_45

| uint32_t gem5::GEM5_PACKED::reserved_45 |

Definition at line 262 of file pm4_queues.hh.

◆ reserved_46

| uint32_t gem5::GEM5_PACKED::reserved_46 |

Definition at line 263 of file pm4_queues.hh.

◆ reserved_47

| uint32_t gem5::GEM5_PACKED::reserved_47 |

Definition at line 264 of file pm4_queues.hh.

◆ reserved_48

| uint32_t gem5::GEM5_PACKED::reserved_48 |

Definition at line 265 of file pm4_queues.hh.

◆ reserved_49

| uint32_t gem5::GEM5_PACKED::reserved_49 |

Definition at line 266 of file pm4_queues.hh.

◆ reserved_50

| uint32_t gem5::GEM5_PACKED::reserved_50 |

Definition at line 267 of file pm4_queues.hh.

◆ reserved_51

| uint32_t gem5::GEM5_PACKED::reserved_51 |

Definition at line 268 of file pm4_queues.hh.

◆ reserved_52

| uint32_t gem5::GEM5_PACKED::reserved_52 |

Definition at line 269 of file pm4_queues.hh.

◆ reserved_53

| uint32_t gem5::GEM5_PACKED::reserved_53 |

Definition at line 270 of file pm4_queues.hh.

◆ reserved_54

| uint32_t gem5::GEM5_PACKED::reserved_54 |

Definition at line 271 of file pm4_queues.hh.

◆ reserved_55

| uint32_t gem5::GEM5_PACKED::reserved_55 |

Definition at line 272 of file pm4_queues.hh.

◆ reserved_56

| uint32_t gem5::GEM5_PACKED::reserved_56 |

Definition at line 273 of file pm4_queues.hh.

◆ reserved_57

| uint32_t gem5::GEM5_PACKED::reserved_57 |

Definition at line 274 of file pm4_queues.hh.

◆ reserved_58

| uint32_t gem5::GEM5_PACKED::reserved_58 |

Definition at line 275 of file pm4_queues.hh.

◆ reserved_59

| uint32_t gem5::GEM5_PACKED::reserved_59 |

Definition at line 276 of file pm4_queues.hh.

◆ reserved_60

| uint32_t gem5::GEM5_PACKED::reserved_60 |

Definition at line 277 of file pm4_queues.hh.

◆ reserved_61

| uint32_t gem5::GEM5_PACKED::reserved_61 |

Definition at line 278 of file pm4_queues.hh.

◆ reserved_62

| uint32_t gem5::GEM5_PACKED::reserved_62 |

Definition at line 279 of file pm4_queues.hh.

◆ reserved_63

| uint32_t gem5::GEM5_PACKED::reserved_63 |

Definition at line 280 of file pm4_queues.hh.

◆ reserved_64

| uint32_t gem5::GEM5_PACKED::reserved_64 |

Definition at line 281 of file pm4_queues.hh.

◆ reserved_65

| uint32_t gem5::GEM5_PACKED::reserved_65 |

Definition at line 282 of file pm4_queues.hh.

◆ reserved_66

| uint32_t gem5::GEM5_PACKED::reserved_66 |

Definition at line 283 of file pm4_queues.hh.

◆ reserved_67

| uint32_t gem5::GEM5_PACKED::reserved_67 |

Definition at line 284 of file pm4_queues.hh.

◆ reserved_68

| uint32_t gem5::GEM5_PACKED::reserved_68 |

Definition at line 285 of file pm4_queues.hh.

◆ reserved_69

| uint32_t gem5::GEM5_PACKED::reserved_69 |

Definition at line 286 of file pm4_queues.hh.

◆ reserved_70

| uint32_t gem5::GEM5_PACKED::reserved_70 |

Definition at line 287 of file pm4_queues.hh.

◆ reserved_71

| uint32_t gem5::GEM5_PACKED::reserved_71 |

Definition at line 288 of file pm4_queues.hh.

◆ reserved_72

| uint32_t gem5::GEM5_PACKED::reserved_72 |

Definition at line 289 of file pm4_queues.hh.

◆ reserved_73

| uint32_t gem5::GEM5_PACKED::reserved_73 |

Definition at line 290 of file pm4_queues.hh.

◆ reserved_74

| uint32_t gem5::GEM5_PACKED::reserved_74 |

Definition at line 291 of file pm4_queues.hh.

◆ reserved_75

| uint32_t gem5::GEM5_PACKED::reserved_75 |

Definition at line 292 of file pm4_queues.hh.

◆ reserved_76

| uint32_t gem5::GEM5_PACKED::reserved_76 |

Definition at line 293 of file pm4_queues.hh.

◆ reserved_77

| uint32_t gem5::GEM5_PACKED::reserved_77 |

Definition at line 294 of file pm4_queues.hh.

◆ reserved_78

| uint32_t gem5::GEM5_PACKED::reserved_78 |

Definition at line 295 of file pm4_queues.hh.

◆ reserved_79

| uint32_t gem5::GEM5_PACKED::reserved_79 |

Definition at line 296 of file pm4_queues.hh.

◆ reserved_80

| uint32_t gem5::GEM5_PACKED::reserved_80 |

Definition at line 297 of file pm4_queues.hh.

◆ reserved_81

| uint32_t gem5::GEM5_PACKED::reserved_81 |

Definition at line 298 of file pm4_queues.hh.

◆ reserved_82

| uint32_t gem5::GEM5_PACKED::reserved_82 |

Definition at line 299 of file pm4_queues.hh.

◆ reserved_83

| uint32_t gem5::GEM5_PACKED::reserved_83 |

Definition at line 300 of file pm4_queues.hh.

◆ reserved_84

| uint32_t gem5::GEM5_PACKED::reserved_84 |

Definition at line 301 of file pm4_queues.hh.

◆ reserved_85

| uint32_t gem5::GEM5_PACKED::reserved_85 |

Definition at line 302 of file pm4_queues.hh.

◆ reserved_86

| uint32_t gem5::GEM5_PACKED::reserved_86 |

Definition at line 303 of file pm4_queues.hh.

◆ reserved_87

| uint32_t gem5::GEM5_PACKED::reserved_87 |

Definition at line 304 of file pm4_queues.hh.

◆ reserved_88

| uint32_t gem5::GEM5_PACKED::reserved_88 |

Definition at line 305 of file pm4_queues.hh.

◆ reserved_89

| uint32_t gem5::GEM5_PACKED::reserved_89 |

Definition at line 306 of file pm4_queues.hh.

◆ reserved_90

| uint32_t gem5::GEM5_PACKED::reserved_90 |

Definition at line 307 of file pm4_queues.hh.

◆ reserved_91

| uint32_t gem5::GEM5_PACKED::reserved_91 |

Definition at line 308 of file pm4_queues.hh.

◆ reserved_92

| uint32_t gem5::GEM5_PACKED::reserved_92 |

Definition at line 309 of file pm4_queues.hh.

◆ reserved_93

| uint32_t gem5::GEM5_PACKED::reserved_93 |

Definition at line 310 of file pm4_queues.hh.

◆ reserved_94

| uint32_t gem5::GEM5_PACKED::reserved_94 |

Definition at line 311 of file pm4_queues.hh.

◆ reserved_95

| uint32_t gem5::GEM5_PACKED::reserved_95 |

Definition at line 312 of file pm4_queues.hh.

◆ reserved_96

| uint32_t gem5::GEM5_PACKED::reserved_96 |

Definition at line 313 of file pm4_queues.hh.

◆ reserved_97

| uint32_t gem5::GEM5_PACKED::reserved_97 |

Definition at line 314 of file pm4_queues.hh.

◆ reserved_98

| uint32_t gem5::GEM5_PACKED::reserved_98 |

Definition at line 315 of file pm4_queues.hh.

◆ reserved_99

| uint32_t gem5::GEM5_PACKED::reserved_99 |

Definition at line 316 of file pm4_queues.hh.

◆ resume

| uint32_t gem5::GEM5_PACKED::resume |

Definition at line 102 of file pm4_defines.hh.

◆ ret

| Addr gem5::GEM5_PACKED::ret |

Definition at line 386 of file sdma_packets.hh.

◆ retHi

| uint32_t gem5::GEM5_PACKED::retHi |

Definition at line 384 of file sdma_packets.hh.

◆ retLo

| uint32_t gem5::GEM5_PACKED::retLo |

Definition at line 383 of file sdma_packets.hh.

◆ retryCount

| uint32_t gem5::GEM5_PACKED::retryCount |

Definition at line 214 of file sdma_packets.hh.

Referenced by gem5::SDMAEngine::pollRegMem(), and gem5::SDMAEngine::pollRegMemRead().

◆ rptr [1/2]

| uint32_t gem5::GEM5_PACKED::rptr |

Definition at line 114 of file pm4_queues.hh.

Referenced by gem5::PM4Queue::fastforwardRptr(), gem5::PM4Queue::getRptr(), gem5::PM4Queue::incRptr(), gem5::PM4PacketProcessor::processMQD(), gem5::SDMAEngine::registerRLCQueue(), gem5::PM4Queue::rptr(), gem5::PM4PacketProcessor::setHqdPqPtr(), gem5::SDMAEngine::unregisterRLCQueue(), and gem5::PM4PacketProcessor::unserialize().

◆ rptr [2/2]

| uint64_t gem5::GEM5_PACKED::rptr |

Definition at line 213 of file pm4_queues.hh.

◆ sdma_enable

| uint32_t gem5::GEM5_PACKED::sdma_enable |

Definition at line 312 of file pm4_defines.hh.

◆ sdma_engine_id

| uint32_t gem5::GEM5_PACKED::sdma_engine_id |