#include <exported_clock_rate_control.hh>

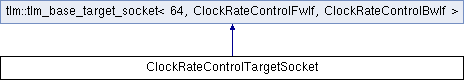

Inheritance diagram for ClockRateControlTargetSocket:

Public Types | |

| typedef tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > | Base |

Public Types inherited from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > Public Types inherited from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > | |

| typedef ClockRateControlFwIf | fw_interface_type |

| typedef ClockRateControlBwIf | bw_interface_type |

| typedef sc_core::sc_port< bw_interface_type, 1, sc_core::SC_ONE_OR_MORE_BOUND > | port_type |

| typedef sc_core::sc_export< fw_interface_type > | export_type |

| typedef tlm_base_initiator_socket_b< BUSWIDTH, fw_interface_type, bw_interface_type > | base_initiator_socket_type |

| typedef tlm_base_target_socket_b< BUSWIDTH, fw_interface_type, bw_interface_type > | base_type |

Additional Inherited Members | |

Protected Attributes inherited from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > Protected Attributes inherited from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > | |

| port_type | m_port |

Detailed Description

Definition at line 96 of file exported_clock_rate_control.hh.

Member Typedef Documentation

◆ Base

| typedef tlm::tlm_base_target_socket<64, ClockRateControlFwIf, ClockRateControlBwIf> ClockRateControlTargetSocket::Base |

Definition at line 102 of file exported_clock_rate_control.hh.

Member Function Documentation

◆ get_protocol_types()

|

inlineoverride |

Definition at line 116 of file exported_clock_rate_control.hh.

◆ kind()

|

inlineoverride |

Definition at line 110 of file exported_clock_rate_control.hh.

The documentation for this class was generated from the following file:

- arch/arm/fastmodel/protocol/exported_clock_rate_control.hh