#include <dyn_inst.hh>

Classes | |

| struct | Regs |

| Collect register related information into a single struct. More... | |

Public Types | |

| typedef std::list< DynInstPtr >::iterator | ListIt |

Public Member Functions | |

| DynInst (const StaticInstPtr &staticInst, const StaticInstPtr ¯oop, TheISA::PCState pc, TheISA::PCState predPC, InstSeqNum seq_num, CPU *cpu) | |

| BaseDynInst constructor given a binary instruction. More... | |

| DynInst (const StaticInstPtr &_staticInst, const StaticInstPtr &_macroop) | |

| BaseDynInst constructor given a static inst pointer. More... | |

| ~DynInst () | |

| Fault | execute () |

| Executes the instruction. More... | |

| Fault | initiateAcc () |

| Initiates the access. More... | |

| Fault | completeAcc (PacketPtr pkt) |

| Completes the access. More... | |

| BaseCPU * | getCpuPtr () |

| void | recordResult (bool f) |

| Records changes to result? More... | |

| bool | effAddrValid () const |

| Is the effective virtual address valid. More... | |

| void | effAddrValid (bool b) |

| bool | memOpDone () const |

| Whether or not the memory operation is done. More... | |

| void | memOpDone (bool f) |

| bool | notAnInst () const |

| void | setNotAnInst () |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. More... | |

| Fault | initiateMemRead (Addr addr, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable) override |

| Fault | initiateHtmCmd (Request::Flags flags) override |

| Initiate an HTM command, e.g. More... | |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable) override |

| Fault | initiateMemAMO (Addr addr, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| bool | translationStarted () const |

| True if the DTB address translation has started. More... | |

| void | translationStarted (bool f) |

| bool | translationCompleted () const |

| True if the DTB address translation has completed. More... | |

| void | translationCompleted (bool f) |

| bool | possibleLoadViolation () const |

| True if this address was found to match a previous load and they issued out of order. More... | |

| void | possibleLoadViolation (bool f) |

| bool | hitExternalSnoop () const |

| True if the address hit a external snoop while sitting in the LSQ. More... | |

| void | hitExternalSnoop (bool f) |

| bool | isTranslationDelayed () const |

| Returns true if the DTB address translation is being delayed due to a hw page table walk. More... | |

| void | renameDestReg (int idx, PhysRegIdPtr renamed_dest, PhysRegIdPtr previous_rename) |

| Renames a destination register to a physical register. More... | |

| void | renameSrcReg (int idx, PhysRegIdPtr renamed_src) |

| Renames a source logical register to the physical register which has/will produce that logical register's result. More... | |

| void | dump () |

| Dumps out contents of this BaseDynInst. More... | |

| void | dump (std::string &outstring) |

| Dumps out contents of this BaseDynInst into given string. More... | |

| int | cpuId () const |

| Read this CPU's ID. More... | |

| uint32_t | socketId () const |

| Read this CPU's Socket ID. More... | |

| RequestorID | requestorId () const |

| Read this CPU's data requestor ID. More... | |

| ContextID | contextId () const |

| Read this context's system-wide ID. More... | |

| Fault | getFault () const |

| Returns the fault type. More... | |

| Fault & | getFault () |

| TODO: This I added for the LSQRequest side to be able to modify the fault. More... | |

| bool | doneTargCalc () |

| Checks whether or not this instruction has had its branch target calculated yet. More... | |

| void | setPredTarg (const TheISA::PCState &_predPC) |

| Set the predicted target of this current instruction. More... | |

| const TheISA::PCState & | readPredTarg () |

| Addr | predInstAddr () |

| Returns the predicted PC immediately after the branch. More... | |

| Addr | predNextInstAddr () |

| Returns the predicted PC two instructions after the branch. More... | |

| Addr | predMicroPC () |

| Returns the predicted micro PC after the branch. More... | |

| bool | readPredTaken () |

| Returns whether the instruction was predicted taken or not. More... | |

| void | setPredTaken (bool predicted_taken) |

| bool | mispredicted () |

| Returns whether the instruction mispredicted. More... | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isFullMemBarrier () const |

| bool | isReadBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isUnverifiable () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isHtmCmd () const |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| void | setHtmTransactionalState (uint64_t htm_uid, uint64_t htm_depth) |

| void | clearHtmTransactionalState () |

| void | setSerializeBefore () |

| Temporarily sets this instruction as a serialize before instruction. More... | |

| void | clearSerializeBefore () |

| Clears the serializeBefore part of this instruction. More... | |

| bool | isTempSerializeBefore () |

| Checks if this serializeBefore is only temporarily set. More... | |

| void | setSerializeAfter () |

| Temporarily sets this instruction as a serialize after instruction. More... | |

| void | clearSerializeAfter () |

| Clears the serializeAfter part of this instruction. More... | |

| bool | isTempSerializeAfter () |

| Checks if this serializeAfter is only temporarily set. More... | |

| void | setSerializeHandled () |

| Sets the serialization part of this instruction as handled. More... | |

| bool | isSerializeHandled () |

| Checks if the serialization part of this instruction has been handled. More... | |

| OpClass | opClass () const |

| Returns the opclass of this instruction. More... | |

| TheISA::PCState | branchTarget () const |

| Returns the branch target address. More... | |

| size_t | numSrcRegs () const |

| Returns the number of source registers. More... | |

| size_t | numDestRegs () const |

| Returns the number of destination registers. More... | |

| int8_t | numFPDestRegs () const |

| int8_t | numIntDestRegs () const |

| int8_t | numCCDestRegs () const |

| int8_t | numVecDestRegs () const |

| int8_t | numVecElemDestRegs () const |

| int8_t | numVecPredDestRegs () const |

| const RegId & | destRegIdx (int i) const |

| Returns the logical register index of the i'th destination register. More... | |

| const RegId & | srcRegIdx (int i) const |

| Returns the logical register index of the i'th source register. More... | |

| uint8_t | resultSize () |

| Return the size of the instResult queue. More... | |

| InstResult | popResult (InstResult dflt=InstResult()) |

| Pops a result off the instResult queue. More... | |

| void | markSrcRegReady () |

| Records that one of the source registers is ready. More... | |

| void | markSrcRegReady (RegIndex src_idx) |

| Marks a specific register as ready. More... | |

| void | setCompleted () |

| Sets this instruction as completed. More... | |

| bool | isCompleted () const |

| Returns whether or not this instruction is completed. More... | |

| void | setResultReady () |

| Marks the result as ready. More... | |

| bool | isResultReady () const |

| Returns whether or not the result is ready. More... | |

| void | setCanIssue () |

| Sets this instruction as ready to issue. More... | |

| bool | readyToIssue () const |

| Returns whether or not this instruction is ready to issue. More... | |

| void | clearCanIssue () |

| Clears this instruction being able to issue. More... | |

| void | setIssued () |

| Sets this instruction as issued from the IQ. More... | |

| bool | isIssued () const |

| Returns whether or not this instruction has issued. More... | |

| void | clearIssued () |

| Clears this instruction as being issued. More... | |

| void | setExecuted () |

| Sets this instruction as executed. More... | |

| bool | isExecuted () const |

| Returns whether or not this instruction has executed. More... | |

| void | setCanCommit () |

| Sets this instruction as ready to commit. More... | |

| void | clearCanCommit () |

| Clears this instruction as being ready to commit. More... | |

| bool | readyToCommit () const |

| Returns whether or not this instruction is ready to commit. More... | |

| void | setAtCommit () |

| bool | isAtCommit () |

| void | setCommitted () |

| Sets this instruction as committed. More... | |

| bool | isCommitted () const |

| Returns whether or not this instruction is committed. More... | |

| void | setSquashed () |

| Sets this instruction as squashed. More... | |

| bool | isSquashed () const |

| Returns whether or not this instruction is squashed. More... | |

| void | setInIQ () |

| Sets this instruction as a entry the IQ. More... | |

| void | clearInIQ () |

| Sets this instruction as a entry the IQ. More... | |

| bool | isInIQ () const |

| Returns whether or not this instruction has issued. More... | |

| void | setSquashedInIQ () |

| Sets this instruction as squashed in the IQ. More... | |

| bool | isSquashedInIQ () const |

| Returns whether or not this instruction is squashed in the IQ. More... | |

| void | setInLSQ () |

| Sets this instruction as a entry the LSQ. More... | |

| void | removeInLSQ () |

| Sets this instruction as a entry the LSQ. More... | |

| bool | isInLSQ () const |

| Returns whether or not this instruction is in the LSQ. More... | |

| void | setSquashedInLSQ () |

| Sets this instruction as squashed in the LSQ. More... | |

| bool | isSquashedInLSQ () const |

| Returns whether or not this instruction is squashed in the LSQ. More... | |

| void | setInROB () |

| Sets this instruction as a entry the ROB. More... | |

| void | clearInROB () |

| Sets this instruction as a entry the ROB. More... | |

| bool | isInROB () const |

| Returns whether or not this instruction is in the ROB. More... | |

| void | setSquashedInROB () |

| Sets this instruction as squashed in the ROB. More... | |

| bool | isSquashedInROB () const |

| Returns whether or not this instruction is squashed in the ROB. More... | |

| bool | isPinnedRegsRenamed () const |

| Returns whether pinned registers are renamed. More... | |

| void | setPinnedRegsRenamed () |

| Sets the destination registers as renamed. More... | |

| bool | isPinnedRegsWritten () const |

| Returns whether destination registers are written. More... | |

| void | setPinnedRegsWritten () |

| Sets destination registers as written. More... | |

| bool | isPinnedRegsSquashDone () const |

| Return whether dest registers' pinning status updated after squash. More... | |

| void | setPinnedRegsSquashDone () |

| Sets dest registers' status updated after squash. More... | |

| TheISA::PCState | pcState () const override |

| Read the PC state of this instruction. More... | |

| void | pcState (const TheISA::PCState &val) override |

| Set the PC state of this instruction. More... | |

| Addr | instAddr () const |

| Read the PC of this instruction. More... | |

| Addr | nextInstAddr () const |

| Read the PC of the next instruction. More... | |

| Addr | microPC () const |

| Read the micro PC of this instruction. More... | |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| void | setTid (ThreadID tid) |

| Sets the thread id. More... | |

| void | setThreadState (ThreadState *state) |

| Sets the pointer to the thread state. More... | |

| gem5::ThreadContext * | tcBase () const override |

| Returns the thread context. More... | |

| bool | strictlyOrdered () const |

| Is this instruction's memory access strictly ordered? More... | |

| void | strictlyOrdered (bool so) |

| bool | hasRequest () const |

| Has this instruction generated a memory request. More... | |

| void | setRequest () |

| Assert this instruction has generated a memory request. More... | |

| ListIt & | getInstListIt () |

| Returns iterator to this instruction in the list of all insts. More... | |

| void | setInstListIt (ListIt _instListIt) |

| Sets iterator for this instruction in the list of all insts. More... | |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. More... | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. More... | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (gem5::ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a misc. More... | |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a misc. More... | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| Reads a misc. More... | |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| Sets a misc. More... | |

| void | updateMiscRegs () |

| Called at the commit stage to update the misc. More... | |

| void | forwardOldRegs () |

| void | trap (const Fault &fault) |

| Traps to handle specified fault. More... | |

| RegVal | readIntRegOperand (const StaticInst *si, int idx) override |

| Reads an integer register. More... | |

| RegVal | readFloatRegOperandBits (const StaticInst *si, int idx) override |

| Reads a floating point register in its binary format, instead of by value. More... | |

| const TheISA::VecRegContainer & | readVecRegOperand (const StaticInst *si, int idx) const override |

| Vector Register Interfaces. More... | |

| TheISA::VecRegContainer & | getWritableVecRegOperand (const StaticInst *si, int idx) override |

| Read destination vector register operand for modification. More... | |

| TheISA::VecElem | readVecElemOperand (const StaticInst *si, int idx) const override |

| Vector Elem Interfaces. More... | |

| const TheISA::VecPredRegContainer & | readVecPredRegOperand (const StaticInst *si, int idx) const override |

| Predicate registers interface. More... | |

| TheISA::VecPredRegContainer & | getWritableVecPredRegOperand (const StaticInst *si, int idx) override |

| Gets destination predicate register operand for modification. More... | |

| RegVal | readCCRegOperand (const StaticInst *si, int idx) override |

| void | setIntRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setFloatRegOperandBits (const StaticInst *si, int idx, RegVal val) override |

| Sets the bits of a floating point register of single width to a binary value. More... | |

| void | setVecRegOperand (const StaticInst *si, int idx, const TheISA::VecRegContainer &val) override |

| Sets a destination vector register operand to a value. More... | |

| void | setVecElemOperand (const StaticInst *si, int idx, const TheISA::VecElem val) override |

| Sets a vector register to a value. More... | |

| void | setVecPredRegOperand (const StaticInst *si, int idx, const TheISA::VecPredRegContainer &val) override |

| Sets a destination predicate register operand to a value. More... | |

| void | setCCRegOperand (const StaticInst *si, int idx, RegVal val) override |

| template<typename T > | |

| void | setScalarResult (T &&t) |

| Pushes a result onto the instResult queue. More... | |

| template<typename T > | |

| void | setVecResult (T &&t) |

| Full vector result. More... | |

| template<typename T > | |

| void | setVecElemResult (T &&t) |

| Vector element result. More... | |

| template<typename T > | |

| void | setVecPredResult (T &&t) |

| Predicate result. More... | |

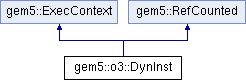

Public Member Functions inherited from gem5::ExecContext Public Member Functions inherited from gem5::ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Perform an atomic memory read operation. More... | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Initiate a timing memory read operation. More... | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable)=0 |

| For atomic-mode contexts, perform an atomic memory write operation. More... | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More... | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More... | |

Public Member Functions inherited from gem5::RefCounted Public Member Functions inherited from gem5::RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. More... | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. More... | |

| void | incref () const |

| Increment the reference count. More... | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. More... | |

Public Attributes | |

| InstSeqNum | seqNum = 0 |

| The sequence number of the instruction. More... | |

| const StaticInstPtr | staticInst |

| The StaticInst used by this BaseDynInst. More... | |

| CPU * | cpu = nullptr |

| Pointer to the Impl's CPU object. More... | |

| ThreadState * | thread = nullptr |

| Pointer to the thread state. More... | |

| Fault | fault = NoFault |

| The kind of fault this instruction has generated. More... | |

| Trace::InstRecord * | traceData = nullptr |

| InstRecord that tracks this instructions. More... | |

| Regs | regs |

| ThreadID | threadNumber = 0 |

| The thread this instruction is from. More... | |

| ListIt | instListIt |

| Iterator pointing to this BaseDynInst in the list of all insts. More... | |

| TheISA::PCState | predPC |

| Predicted PC state after this instruction. More... | |

| const StaticInstPtr | macroop |

| The Macroop if one exists. More... | |

| uint8_t | readyRegs = 0 |

| How many source registers are ready. More... | |

| Addr | effAddr = 0 |

| The effective virtual address (lds & stores only). More... | |

| Addr | physEffAddr = 0 |

| The effective physical address. More... | |

| unsigned | memReqFlags = 0 |

| The memory request flags (from translation). More... | |

| unsigned | effSize |

| The size of the request. More... | |

| uint8_t * | memData = nullptr |

| Pointer to the data for the memory access. More... | |

| ssize_t | lqIdx = -1 |

| Load queue index. More... | |

| LSQUnit::LQIterator | lqIt |

| ssize_t | sqIdx = -1 |

| Store queue index. More... | |

| LSQUnit::SQIterator | sqIt |

| LSQ::LSQRequest * | savedReq |

| Saved memory request (needed when the DTB address translation is delayed due to a hw page table walk). More... | |

| RequestPtr | reqToVerify |

| Tick | firstIssue = -1 |

| Tick | lastWakeDependents = -1 |

Protected Attributes | |

| std::queue< InstResult > | instResult |

| The result of the instruction; assumes an instruction can have many destination registers. More... | |

| TheISA::PCState | pc |

| PC state for this instruction. More... | |

| std::vector< RegVal > | _destMiscRegVal |

| Values to be written to the destination misc. More... | |

| std::vector< short > | _destMiscRegIdx |

| Indexes of the destination misc. More... | |

Private Attributes | |

| std::bitset< MaxFlags > | instFlags |

| std::bitset< NumStatus > | status |

| The status of this BaseDynInst. More... | |

| uint64_t | htmUid = -1 |

| uint64_t | htmDepth = 0 |

Detailed Description

Definition at line 76 of file dyn_inst.hh.

Member Typedef Documentation

◆ ListIt

| typedef std::list<DynInstPtr>::iterator gem5::o3::DynInst::ListIt |

Definition at line 80 of file dyn_inst.hh.

Member Enumeration Documentation

◆ Flags

|

protected |

Definition at line 152 of file dyn_inst.hh.

◆ Status

|

protected |

| Enumerator | |

|---|---|

| IqEntry | |

| RobEntry | Instruction is in the IQ. |

| LsqEntry | Instruction is in the ROB. |

| Completed | Instruction is in the LSQ. |

| ResultReady | Instruction has completed. |

| CanIssue | Instruction has its result. |

| Issued | Instruction can issue and execute. |

| Executed | Instruction has issued. |

| CanCommit | Instruction has executed. |

| AtCommit | Instruction can commit. |

| Committed | Instruction has reached commit. |

| Squashed | Instruction has committed. |

| SquashedInIQ | Instruction is squashed. |

| SquashedInLSQ | Instruction is squashed in the IQ. |

| SquashedInROB | Instruction is squashed in the LSQ. |

| PinnedRegsRenamed | Instruction is squashed in the ROB. |

| PinnedRegsWritten | Pinned registers are renamed. |

| PinnedRegsSquashDone | Pinned registers are written back. |

| RecoverInst | Regs pinning status updated after squash. |

| BlockingInst | Is a recover instruction. |

| ThreadsyncWait | Is a blocking instruction. |

| SerializeBefore | Is a thread synchronization instruction. |

| SerializeAfter | Needs to serialize on instructions ahead of it. |

| SerializeHandled | Needs to serialize instructions behind it. |

| NumStatus | Serialization has been handled. |

Definition at line 122 of file dyn_inst.hh.

Constructor & Destructor Documentation

◆ DynInst() [1/2]

| gem5::o3::DynInst::DynInst | ( | const StaticInstPtr & | staticInst, |

| const StaticInstPtr & | macroop, | ||

| TheISA::PCState | pc, | ||

| TheISA::PCState | predPC, | ||

| InstSeqNum | seq_num, | ||

| CPU * | cpu | ||

| ) |

BaseDynInst constructor given a binary instruction.

Definition at line 55 of file dyn_inst.cc.

References cpu, DPRINTF, gem5::o3::CPU::dumpInsts(), gem5::o3::DynInst::Regs::init(), gem5::o3::CPU::instcount, instFlags, MemAccPredicate, gem5::Named::name(), Predicate, RecordResult, regs, seqNum, and status.

◆ DynInst() [2/2]

| gem5::o3::DynInst::DynInst | ( | const StaticInstPtr & | _staticInst, |

| const StaticInstPtr & | _macroop | ||

| ) |

BaseDynInst constructor given a static inst pointer.

Definition at line 93 of file dyn_inst.cc.

◆ ~DynInst()

| gem5::o3::DynInst::~DynInst | ( | ) |

Definition at line 98 of file dyn_inst.cc.

References cpu, gem5::StaticInst::disassemble(), DPRINTF, DPRINTFR, fault, instAddr(), gem5::o3::CPU::instcount, memData, microPC(), gem5::Named::name(), gem5::NoFault, seqNum, staticInst, traceData, and gem5::X86ISA::val.

Member Function Documentation

◆ armMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1060 of file dyn_inst.hh.

References gem5::BaseCPU::armMonitor(), cpu, and threadNumber.

◆ branchTarget()

|

inline |

Returns the branch target address.

Definition at line 721 of file dyn_inst.hh.

References gem5::StaticInst::branchTarget(), pc, and staticInst.

◆ clearCanCommit()

|

inline |

Clears this instruction as being ready to commit.

Definition at line 865 of file dyn_inst.hh.

◆ clearCanIssue()

|

inline |

Clears this instruction being able to issue.

Definition at line 844 of file dyn_inst.hh.

◆ clearHtmTransactionalState()

|

inline |

Definition at line 675 of file dyn_inst.hh.

References DPRINTF, getHtmTransactionUid(), htmDepth, HtmFromTransaction, htmUid, inHtmTransactionalState(), and instFlags.

◆ clearInIQ()

|

inline |

Sets this instruction as a entry the IQ.

Definition at line 892 of file dyn_inst.hh.

◆ clearInROB()

|

inline |

Sets this instruction as a entry the ROB.

Definition at line 928 of file dyn_inst.hh.

◆ clearIssued()

|

inline |

Clears this instruction as being issued.

Definition at line 853 of file dyn_inst.hh.

◆ clearSerializeAfter()

|

inline |

Clears the serializeAfter part of this instruction.

Definition at line 701 of file dyn_inst.hh.

References SerializeAfter, and status.

◆ clearSerializeBefore()

|

inline |

Clears the serializeBefore part of this instruction.

Definition at line 692 of file dyn_inst.hh.

References SerializeBefore, and status.

◆ completeAcc()

Completes the access.

Only valid for memory operations.

Definition at line 262 of file dyn_inst.cc.

References gem5::o3::CPU::checker, gem5::StaticInst::completeAcc(), cpu, fault, isStoreConditional(), gem5::o3::ThreadState::noSquashFromTC, gem5::Packet::req, reqToVerify, staticInst, thread, and traceData.

◆ contextId()

|

inline |

Read this context's system-wide ID.

Definition at line 538 of file dyn_inst.hh.

References gem5::ThreadState::contextId(), and thread.

◆ cpuId()

|

inline |

Read this CPU's ID.

Definition at line 529 of file dyn_inst.hh.

References cpu, and gem5::BaseCPU::cpuId().

◆ demapPage()

|

inlineoverridevirtual |

Invalidate a page in the DTLB and ITLB.

Implements gem5::ExecContext.

Definition at line 432 of file dyn_inst.hh.

References cpu, gem5::o3::CPU::demapPage(), and gem5::MipsISA::vaddr.

◆ destRegIdx()

|

inline |

Returns the logical register index of the i'th destination register.

Definition at line 750 of file dyn_inst.hh.

References gem5::StaticInst::destRegIdx(), gem5::ArmISA::i, and staticInst.

◆ doneTargCalc()

|

inline |

Checks whether or not this instruction has had its branch target calculated yet.

For now it is not utilized and is hacked to be always false.

- Todo:

- : Actually use this instruction.

Definition at line 551 of file dyn_inst.hh.

◆ dump() [1/2]

| void gem5::o3::DynInst::dump | ( | ) |

Dumps out contents of this BaseDynInst.

Definition at line 167 of file dyn_inst.cc.

References gem5::cprintf(), gem5::StaticInst::disassemble(), pc, staticInst, and threadNumber.

◆ dump() [2/2]

| void gem5::o3::DynInst::dump | ( | std::string & | outstring | ) |

Dumps out contents of this BaseDynInst into given string.

Definition at line 175 of file dyn_inst.cc.

References gem5::StaticInst::disassemble(), pc, gem5::ArmISA::s, staticInst, and threadNumber.

◆ effAddrValid() [1/2]

|

inline |

Is the effective virtual address valid.

Definition at line 414 of file dyn_inst.hh.

References EffAddrValid, and instFlags.

◆ effAddrValid() [2/2]

|

inline |

Definition at line 415 of file dyn_inst.hh.

References gem5::ArmISA::b, EffAddrValid, and instFlags.

◆ execute()

| Fault gem5::o3::DynInst::execute | ( | ) |

Executes the instruction.

Definition at line 228 of file dyn_inst.cc.

References gem5::StaticInst::execute(), fault, gem5::o3::ThreadState::noSquashFromTC, staticInst, thread, and traceData.

◆ forwardOldRegs()

|

inline |

Definition at line 1175 of file dyn_inst.hh.

References gem5::CCRegClass, gem5::RegId::classValue(), gem5::StaticInst::destRegIdx(), gem5::FloatRegClass, gem5::RefCountingPtr< T >::get(), gem5::IntRegClass, gem5::MiscRegClass, numDestRegs(), panic, gem5::o3::DynInst::Regs::prevDestIdx(), setCCRegOperand(), setFloatRegOperandBits(), setIntRegOperand(), setVecElemOperand(), setVecPredRegOperand(), setVecRegOperand(), gem5::VecElemClass, gem5::VecPredRegClass, and gem5::VecRegClass.

◆ getAddrMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1075 of file dyn_inst.hh.

References cpu, gem5::BaseCPU::getCpuAddrMonitor(), and threadNumber.

◆ getCpuPtr()

|

inline |

Definition at line 110 of file dyn_inst.hh.

References cpu.

◆ getFault() [1/2]

|

inline |

TODO: This I added for the LSQRequest side to be able to modify the fault.

There should be a better mechanism in place.

Definition at line 544 of file dyn_inst.hh.

References fault.

◆ getFault() [2/2]

|

inline |

◆ getHtmTransactionalDepth()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 658 of file dyn_inst.hh.

References htmDepth, and inHtmTransactionalState().

◆ getHtmTransactionUid()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 638 of file dyn_inst.hh.

References HtmFromTransaction, htmUid, and instFlags.

Referenced by clearHtmTransactionalState().

◆ getInstListIt()

|

inline |

Returns iterator to this instruction in the list of all insts.

Definition at line 1037 of file dyn_inst.hh.

References instListIt.

◆ getWritableVecPredRegOperand()

|

inlineoverridevirtual |

Gets destination predicate register operand for modification.

Implements gem5::ExecContext.

Definition at line 1271 of file dyn_inst.hh.

References gem5::o3::CPU::getWritableVecPredReg(), and gem5::o3::DynInst::Regs::renamedDestIdx().

◆ getWritableVecRegOperand()

|

inlineoverridevirtual |

Read destination vector register operand for modification.

Implements gem5::ExecContext.

Definition at line 1253 of file dyn_inst.hh.

References gem5::o3::CPU::getWritableVecReg(), and gem5::o3::DynInst::Regs::renamedDestIdx().

◆ hasRequest()

|

inline |

Has this instruction generated a memory request.

Definition at line 1032 of file dyn_inst.hh.

◆ hitExternalSnoop() [1/2]

|

inline |

True if the address hit a external snoop while sitting in the LSQ.

If this is true and a older instruction sees it, this instruction must reexecute

Definition at line 481 of file dyn_inst.hh.

References HitExternalSnoop, and instFlags.

◆ hitExternalSnoop() [2/2]

|

inline |

Definition at line 482 of file dyn_inst.hh.

References gem5::ArmISA::f, HitExternalSnoop, and instFlags.

◆ inHtmTransactionalState()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 652 of file dyn_inst.hh.

References HtmFromTransaction, and instFlags.

Referenced by clearHtmTransactionalState(), and getHtmTransactionalDepth().

◆ initiateAcc()

| Fault gem5::o3::DynInst::initiateAcc | ( | ) |

Initiates the access.

Only valid for memory operations.

Definition at line 245 of file dyn_inst.cc.

References fault, gem5::StaticInst::initiateAcc(), gem5::o3::ThreadState::noSquashFromTC, staticInst, thread, and traceData.

◆ initiateHtmCmd()

|

overridevirtual |

Initiate an HTM command, e.g.

tell Ruby we're starting/stopping a transaction

Implements gem5::ExecContext.

Definition at line 302 of file dyn_inst.cc.

References cpu, and gem5::o3::CPU::pushRequest().

◆ initiateMemAMO()

|

override |

Definition at line 322 of file dyn_inst.cc.

References gem5::X86ISA::addr, cpu, and gem5::o3::CPU::pushRequest().

◆ initiateMemRead()

|

override |

Definition at line 291 of file dyn_inst.cc.

References gem5::X86ISA::addr, cpu, and gem5::o3::CPU::pushRequest().

◆ instAddr()

|

inline |

Read the PC of this instruction.

Definition at line 985 of file dyn_inst.hh.

References pc.

Referenced by ~DynInst().

◆ isAtCommit()

|

inline |

Definition at line 872 of file dyn_inst.hh.

◆ isAtomic()

|

inline |

Definition at line 592 of file dyn_inst.hh.

References gem5::StaticInst::isAtomic(), and staticInst.

◆ isCall()

|

inline |

Definition at line 601 of file dyn_inst.hh.

References gem5::StaticInst::isCall(), and staticInst.

◆ isCommitted()

|

inline |

Returns whether or not this instruction is committed.

Definition at line 878 of file dyn_inst.hh.

◆ isCompleted()

|

inline |

Returns whether or not this instruction is completed.

Definition at line 829 of file dyn_inst.hh.

◆ isCondCtrl()

|

inline |

Definition at line 605 of file dyn_inst.hh.

References gem5::StaticInst::isCondCtrl(), and staticInst.

◆ isControl()

|

inline |

Definition at line 600 of file dyn_inst.hh.

References gem5::StaticInst::isControl(), and staticInst.

◆ isDataPrefetch()

|

inline |

Definition at line 596 of file dyn_inst.hh.

References gem5::StaticInst::isDataPrefetch(), and staticInst.

◆ isDelayedCommit()

|

inline |

Definition at line 628 of file dyn_inst.hh.

References gem5::StaticInst::isDelayedCommit(), and staticInst.

◆ isDirectCtrl()

|

inline |

Definition at line 603 of file dyn_inst.hh.

References gem5::StaticInst::isDirectCtrl(), and staticInst.

◆ isExecuted()

|

inline |

Returns whether or not this instruction has executed.

Definition at line 859 of file dyn_inst.hh.

◆ isFirstMicroop()

|

inline |

Definition at line 630 of file dyn_inst.hh.

References gem5::StaticInst::isFirstMicroop(), and staticInst.

◆ isFloating()

|

inline |

Definition at line 598 of file dyn_inst.hh.

References gem5::StaticInst::isFloating(), and staticInst.

◆ isFullMemBarrier()

|

inline |

Definition at line 619 of file dyn_inst.hh.

References gem5::StaticInst::isFullMemBarrier(), and staticInst.

◆ isHtmCancel()

|

inline |

Definition at line 634 of file dyn_inst.hh.

References gem5::StaticInst::isHtmCancel(), and staticInst.

◆ isHtmCmd()

|

inline |

Definition at line 635 of file dyn_inst.hh.

References gem5::StaticInst::isHtmCmd(), and staticInst.

◆ isHtmStart()

|

inline |

Definition at line 632 of file dyn_inst.hh.

References gem5::StaticInst::isHtmStart(), and staticInst.

◆ isHtmStop()

|

inline |

Definition at line 633 of file dyn_inst.hh.

References gem5::StaticInst::isHtmStop(), and staticInst.

◆ isIndirectCtrl()

|

inline |

Definition at line 604 of file dyn_inst.hh.

References gem5::StaticInst::isIndirectCtrl(), and staticInst.

◆ isInIQ()

|

inline |

Returns whether or not this instruction has issued.

Definition at line 895 of file dyn_inst.hh.

◆ isInLSQ()

|

inline |

Returns whether or not this instruction is in the LSQ.

Definition at line 913 of file dyn_inst.hh.

◆ isInROB()

|

inline |

Returns whether or not this instruction is in the ROB.

Definition at line 931 of file dyn_inst.hh.

◆ isInstPrefetch()

|

inline |

Definition at line 595 of file dyn_inst.hh.

References gem5::StaticInst::isInstPrefetch(), and staticInst.

◆ isInteger()

|

inline |

Definition at line 597 of file dyn_inst.hh.

References gem5::StaticInst::isInteger(), and staticInst.

◆ isIssued()

|

inline |

Returns whether or not this instruction has issued.

Definition at line 850 of file dyn_inst.hh.

◆ isLastMicroop()

|

inline |

Definition at line 629 of file dyn_inst.hh.

References gem5::StaticInst::isLastMicroop(), and staticInst.

◆ isLoad()

|

inline |

Definition at line 590 of file dyn_inst.hh.

References gem5::StaticInst::isLoad(), and staticInst.

◆ isMacroop()

|

inline |

Definition at line 626 of file dyn_inst.hh.

References gem5::StaticInst::isMacroop(), and staticInst.

◆ isMemRef()

|

inline |

Definition at line 589 of file dyn_inst.hh.

References gem5::StaticInst::isMemRef(), and staticInst.

◆ isMicroop()

|

inline |

Definition at line 627 of file dyn_inst.hh.

References gem5::StaticInst::isMicroop(), and staticInst.

◆ isNonSpeculative()

|

inline |

Definition at line 622 of file dyn_inst.hh.

References gem5::StaticInst::isNonSpeculative(), and staticInst.

◆ isNop()

|

inline |

Definition at line 588 of file dyn_inst.hh.

References gem5::StaticInst::isNop(), and staticInst.

◆ isPinnedRegsRenamed()

|

inline |

Returns whether pinned registers are renamed.

Definition at line 940 of file dyn_inst.hh.

References PinnedRegsRenamed, and status.

Referenced by setSquashed().

◆ isPinnedRegsSquashDone()

|

inline |

Return whether dest registers' pinning status updated after squash.

Definition at line 965 of file dyn_inst.hh.

References PinnedRegsSquashDone, and status.

Referenced by setSquashed().

◆ isPinnedRegsWritten()

|

inline |

Returns whether destination registers are written.

Definition at line 952 of file dyn_inst.hh.

References PinnedRegsWritten, and status.

Referenced by setSquashed().

◆ isQuiesce()

|

inline |

Definition at line 623 of file dyn_inst.hh.

References gem5::StaticInst::isQuiesce(), and staticInst.

◆ isReadBarrier()

|

inline |

Definition at line 620 of file dyn_inst.hh.

References gem5::StaticInst::isReadBarrier(), and staticInst.

◆ isResultReady()

|

inline |

Returns whether or not the result is ready.

Definition at line 835 of file dyn_inst.hh.

References ResultReady, and status.

◆ isReturn()

|

inline |

Definition at line 602 of file dyn_inst.hh.

References gem5::StaticInst::isReturn(), and staticInst.

◆ isSerializeAfter()

|

inline |

Definition at line 614 of file dyn_inst.hh.

References gem5::StaticInst::isSerializeAfter(), SerializeAfter, staticInst, and status.

◆ isSerializeBefore()

|

inline |

Definition at line 609 of file dyn_inst.hh.

References gem5::StaticInst::isSerializeBefore(), SerializeBefore, staticInst, and status.

◆ isSerializeHandled()

|

inline |

Checks if the serialization part of this instruction has been handled.

This does not apply to the temporary serializing state; it only applies to this instruction's own permanent serializing state.

Definition at line 714 of file dyn_inst.hh.

References SerializeHandled, and status.

◆ isSerializing()

|

inline |

Definition at line 607 of file dyn_inst.hh.

References gem5::StaticInst::isSerializing(), and staticInst.

◆ isSquashAfter()

|

inline |

Definition at line 618 of file dyn_inst.hh.

References gem5::StaticInst::isSquashAfter(), and staticInst.

◆ isSquashed()

|

inline |

Returns whether or not this instruction is squashed.

Definition at line 884 of file dyn_inst.hh.

◆ isSquashedInIQ()

|

inline |

Returns whether or not this instruction is squashed in the IQ.

Definition at line 901 of file dyn_inst.hh.

References SquashedInIQ, and status.

◆ isSquashedInLSQ()

|

inline |

Returns whether or not this instruction is squashed in the LSQ.

Definition at line 919 of file dyn_inst.hh.

References SquashedInLSQ, and status.

◆ isSquashedInROB()

|

inline |

Returns whether or not this instruction is squashed in the ROB.

Definition at line 937 of file dyn_inst.hh.

References SquashedInROB, and status.

◆ isStore()

|

inline |

Definition at line 591 of file dyn_inst.hh.

References gem5::StaticInst::isStore(), and staticInst.

◆ isStoreConditional()

|

inline |

Definition at line 593 of file dyn_inst.hh.

References gem5::StaticInst::isStoreConditional(), and staticInst.

Referenced by completeAcc().

◆ isSyscall()

|

inline |

Definition at line 625 of file dyn_inst.hh.

References gem5::StaticInst::isSyscall(), and staticInst.

◆ isTempSerializeAfter()

|

inline |

Checks if this serializeAfter is only temporarily set.

Definition at line 704 of file dyn_inst.hh.

References SerializeAfter, and status.

◆ isTempSerializeBefore()

|

inline |

Checks if this serializeBefore is only temporarily set.

Definition at line 695 of file dyn_inst.hh.

References SerializeBefore, and status.

◆ isTranslationDelayed()

|

inline |

Returns true if the DTB address translation is being delayed due to a hw page table walk.

Definition at line 489 of file dyn_inst.hh.

References translationCompleted(), and translationStarted().

◆ isUncondCtrl()

|

inline |

Definition at line 606 of file dyn_inst.hh.

References gem5::StaticInst::isUncondCtrl(), and staticInst.

◆ isUnverifiable()

|

inline |

Definition at line 624 of file dyn_inst.hh.

References gem5::StaticInst::isUnverifiable(), and staticInst.

◆ isVector()

|

inline |

Definition at line 599 of file dyn_inst.hh.

References gem5::StaticInst::isVector(), and staticInst.

◆ isWriteBarrier()

|

inline |

Definition at line 621 of file dyn_inst.hh.

References gem5::StaticInst::isWriteBarrier(), and staticInst.

◆ markSrcRegReady() [1/2]

| void gem5::o3::DynInst::markSrcRegReady | ( | ) |

Records that one of the source registers is ready.

Definition at line 185 of file dyn_inst.cc.

References DPRINTF, numSrcRegs(), readyRegs, readyToIssue(), seqNum, and setCanIssue().

Referenced by markSrcRegReady().

◆ markSrcRegReady() [2/2]

| void gem5::o3::DynInst::markSrcRegReady | ( | RegIndex | src_idx | ) |

Marks a specific register as ready.

Definition at line 195 of file dyn_inst.cc.

References markSrcRegReady(), gem5::o3::DynInst::Regs::readySrcIdx(), and regs.

◆ memOpDone() [1/2]

|

inline |

Whether or not the memory operation is done.

Definition at line 418 of file dyn_inst.hh.

◆ memOpDone() [2/2]

|

inline |

Definition at line 419 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and MemOpDone.

◆ microPC()

|

inline |

Read the micro PC of this instruction.

Definition at line 991 of file dyn_inst.hh.

References pc.

Referenced by ~DynInst().

◆ mispredicted()

|

inline |

Returns whether the instruction mispredicted.

Definition at line 578 of file dyn_inst.hh.

References gem5::StaticInst::advancePC(), pc, predPC, and staticInst.

◆ mwait()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1065 of file dyn_inst.hh.

References cpu, gem5::BaseCPU::mwait(), and threadNumber.

◆ mwaitAtomic()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1070 of file dyn_inst.hh.

References cpu, gem5::o3::CPU::mmu, gem5::BaseCPU::mwaitAtomic(), and threadNumber.

◆ newHtmTransactionUid()

|

inlineoverridevirtual |

◆ nextInstAddr()

|

inline |

◆ notAnInst()

|

inline |

Definition at line 421 of file dyn_inst.hh.

◆ numCCDestRegs()

|

inline |

Definition at line 736 of file dyn_inst.hh.

References gem5::StaticInst::numCCDestRegs(), and staticInst.

◆ numDestRegs()

|

inline |

Returns the number of destination registers.

Definition at line 730 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::numDests(), and regs.

Referenced by forwardOldRegs(), and setSquashed().

◆ numFPDestRegs()

|

inline |

Definition at line 734 of file dyn_inst.hh.

References gem5::StaticInst::numFPDestRegs(), and staticInst.

◆ numIntDestRegs()

|

inline |

Definition at line 735 of file dyn_inst.hh.

References gem5::StaticInst::numIntDestRegs(), and staticInst.

◆ numSrcRegs()

|

inline |

Returns the number of source registers.

Definition at line 727 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::numSrcs(), and regs.

Referenced by markSrcRegReady().

◆ numVecDestRegs()

|

inline |

Definition at line 737 of file dyn_inst.hh.

References gem5::StaticInst::numVecDestRegs(), and staticInst.

◆ numVecElemDestRegs()

|

inline |

Definition at line 739 of file dyn_inst.hh.

References gem5::StaticInst::numVecElemDestRegs(), and staticInst.

◆ numVecPredDestRegs()

|

inline |

Definition at line 744 of file dyn_inst.hh.

References gem5::StaticInst::numVecPredDestRegs(), and staticInst.

◆ opClass()

|

inline |

Returns the opclass of this instruction.

Definition at line 717 of file dyn_inst.hh.

References gem5::StaticInst::opClass(), and staticInst.

◆ pcState() [1/2]

|

inlineoverridevirtual |

Read the PC state of this instruction.

Implements gem5::ExecContext.

Definition at line 979 of file dyn_inst.hh.

References pc.

Referenced by gem5::o3::DependencyGraph< gem5::RefCountingPtr >::dump().

◆ pcState() [2/2]

|

inlineoverridevirtual |

Set the PC state of this instruction.

Implements gem5::ExecContext.

Definition at line 982 of file dyn_inst.hh.

References pc, and gem5::X86ISA::val.

◆ popResult()

|

inline |

Pops a result off the instResult queue.

If the result stack is empty, return the default value.

Definition at line 762 of file dyn_inst.hh.

References instResult, and gem5::ArmISA::t.

◆ possibleLoadViolation() [1/2]

|

inline |

True if this address was found to match a previous load and they issued out of order.

If that happend, then it's only a problem if an incoming snoop invalidate modifies the line, in which case we need to squash. If nothing modified the line the order doesn't matter.

Definition at line 467 of file dyn_inst.hh.

References instFlags, and PossibleLoadViolation.

◆ possibleLoadViolation() [2/2]

|

inline |

Definition at line 472 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and PossibleLoadViolation.

◆ predInstAddr()

|

inline |

Returns the predicted PC immediately after the branch.

Definition at line 559 of file dyn_inst.hh.

References predPC.

◆ predMicroPC()

|

inline |

Returns the predicted micro PC after the branch.

Definition at line 565 of file dyn_inst.hh.

References predPC.

◆ predNextInstAddr()

|

inline |

Returns the predicted PC two instructions after the branch.

Definition at line 562 of file dyn_inst.hh.

References predPC.

◆ readCCRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1278 of file dyn_inst.hh.

References gem5::o3::CPU::readCCReg(), and gem5::o3::DynInst::Regs::renamedSrcIdx().

◆ readFloatRegOperandBits()

|

inlineoverridevirtual |

Reads a floating point register in its binary format, instead of by value.

Implements gem5::ExecContext.

Definition at line 1238 of file dyn_inst.hh.

References gem5::o3::CPU::readFloatReg(), and gem5::o3::DynInst::Regs::renamedSrcIdx().

◆ readIntRegOperand()

|

inlineoverridevirtual |

Reads an integer register.

Implements gem5::ExecContext.

Definition at line 1232 of file dyn_inst.hh.

References gem5::o3::CPU::readIntReg(), and gem5::o3::DynInst::Regs::renamedSrcIdx().

◆ readMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1006 of file dyn_inst.hh.

References instFlags, and MemAccPredicate.

◆ readMiscReg()

|

inlineoverridevirtual |

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements gem5::ExecContext.

Definition at line 1108 of file dyn_inst.hh.

References gem5::o3::CPU::readMiscReg().

◆ readMiscRegOperand()

|

inlineoverridevirtual |

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements gem5::ExecContext.

Definition at line 1138 of file dyn_inst.hh.

References gem5::MiscRegClass, gem5::o3::CPU::readMiscReg(), gem5::X86ISA::reg, and gem5::ArmISA::si.

◆ readPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 993 of file dyn_inst.hh.

◆ readPredTaken()

|

inline |

Returns whether the instruction was predicted taken or not.

Definition at line 568 of file dyn_inst.hh.

◆ readPredTarg()

|

inline |

Definition at line 556 of file dyn_inst.hh.

References predPC.

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements gem5::ExecContext.

Definition at line 1045 of file dyn_inst.hh.

References gem5::ThreadState::storeCondFailures, and thread.

◆ readVecElemOperand()

|

inlineoverridevirtual |

Vector Elem Interfaces.

Reads an element of a vector register.

Implements gem5::ExecContext.

Definition at line 1259 of file dyn_inst.hh.

References gem5::o3::CPU::readVecElem(), and gem5::o3::DynInst::Regs::renamedSrcIdx().

◆ readVecPredRegOperand()

|

inlineoverridevirtual |

Predicate registers interface.

Reads source predicate register operand.

Implements gem5::ExecContext.

Definition at line 1265 of file dyn_inst.hh.

References gem5::o3::CPU::readVecPredReg(), and gem5::o3::DynInst::Regs::renamedSrcIdx().

◆ readVecRegOperand()

|

inlineoverridevirtual |

Vector Register Interfaces.

Reads source vector register operand.

Implements gem5::ExecContext.

Definition at line 1244 of file dyn_inst.hh.

References gem5::o3::CPU::readVecReg(), and gem5::o3::DynInst::Regs::renamedSrcIdx().

◆ readyToCommit()

|

inline |

Returns whether or not this instruction is ready to commit.

Definition at line 868 of file dyn_inst.hh.

◆ readyToIssue()

|

inline |

Returns whether or not this instruction is ready to issue.

Definition at line 841 of file dyn_inst.hh.

References CanIssue, and status.

Referenced by markSrcRegReady().

◆ recordResult()

|

inline |

Records changes to result?

Definition at line 411 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and RecordResult.

◆ removeInLSQ()

|

inline |

Sets this instruction as a entry the LSQ.

Definition at line 910 of file dyn_inst.hh.

◆ renameDestReg()

|

inline |

Renames a destination register to a physical register.

Also records the previous physical register that the logical register mapped to.

Definition at line 503 of file dyn_inst.hh.

References gem5::PhysRegId::isPinned(), gem5::o3::DynInst::Regs::prevDestIdx(), regs, gem5::o3::DynInst::Regs::renamedDestIdx(), and setPinnedRegsRenamed().

◆ renameSrcReg()

|

inline |

Renames a source logical register to the physical register which has/will produce that logical register's result.

- Todo:

- : add in whether or not the source register is ready.

Definition at line 517 of file dyn_inst.hh.

References regs, and gem5::o3::DynInst::Regs::renamedSrcIdx().

◆ requestorId()

|

inline |

Read this CPU's data requestor ID.

Definition at line 535 of file dyn_inst.hh.

References cpu, and gem5::BaseCPU::dataRequestorId().

◆ resultSize()

|

inline |

Return the size of the instResult queue.

Definition at line 756 of file dyn_inst.hh.

References instResult.

◆ setAtCommit()

|

inline |

Definition at line 870 of file dyn_inst.hh.

◆ setCanCommit()

|

inline |

Sets this instruction as ready to commit.

Definition at line 862 of file dyn_inst.hh.

◆ setCanIssue()

|

inline |

Sets this instruction as ready to issue.

Definition at line 838 of file dyn_inst.hh.

References CanIssue, and status.

Referenced by markSrcRegReady().

◆ setCCRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1326 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::renamedDestIdx(), gem5::o3::CPU::setCCReg(), setScalarResult(), and gem5::X86ISA::val.

Referenced by forwardOldRegs().

◆ setCommitted()

|

inline |

Sets this instruction as committed.

Definition at line 875 of file dyn_inst.hh.

◆ setCompleted()

|

inline |

Sets this instruction as completed.

Definition at line 826 of file dyn_inst.hh.

◆ setExecuted()

|

inline |

Sets this instruction as executed.

Definition at line 856 of file dyn_inst.hh.

◆ setFloatRegOperandBits()

|

inlineoverridevirtual |

Sets the bits of a floating point register of single width to a binary value.

Implements gem5::ExecContext.

Definition at line 1294 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::renamedDestIdx(), gem5::o3::CPU::setFloatReg(), setScalarResult(), and gem5::X86ISA::val.

Referenced by forwardOldRegs().

◆ setHtmTransactionalState()

|

inline |

Definition at line 667 of file dyn_inst.hh.

References htmDepth, HtmFromTransaction, htmUid, and instFlags.

◆ setInIQ()

|

inline |

Sets this instruction as a entry the IQ.

Definition at line 889 of file dyn_inst.hh.

◆ setInLSQ()

|

inline |

Sets this instruction as a entry the LSQ.

Definition at line 907 of file dyn_inst.hh.

◆ setInROB()

|

inline |

Sets this instruction as a entry the ROB.

Definition at line 925 of file dyn_inst.hh.

◆ setInstListIt()

|

inline |

Sets iterator for this instruction in the list of all insts.

Definition at line 1040 of file dyn_inst.hh.

References instListIt.

◆ setIntRegOperand()

|

inlineoverridevirtual |

- Todo:

- : Make results into arrays so they can handle multiple dest registers.

Implements gem5::ExecContext.

Definition at line 1287 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::renamedDestIdx(), gem5::o3::CPU::setIntReg(), setScalarResult(), and gem5::X86ISA::val.

Referenced by forwardOldRegs().

◆ setIssued()

|

inline |

Sets this instruction as issued from the IQ.

Definition at line 847 of file dyn_inst.hh.

◆ setMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1012 of file dyn_inst.hh.

References instFlags, MemAccPredicate, and gem5::X86ISA::val.

◆ setMiscReg()

|

inlineoverridevirtual |

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Writes to misc. registers are recorded and deferred until the commit stage, when updateMiscRegs() is called. First, check if the misc reg has been written before and update its value to be committed instead of making a new entry. If not, make a new entry and record the write.

Implements gem5::ExecContext.

Definition at line 1117 of file dyn_inst.hh.

References _destMiscRegIdx, _destMiscRegVal, and gem5::X86ISA::val.

Referenced by setMiscRegOperand().

◆ setMiscRegOperand()

|

inlineoverridevirtual |

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Implements gem5::ExecContext.

Definition at line 1149 of file dyn_inst.hh.

References gem5::MiscRegClass, gem5::X86ISA::reg, setMiscReg(), gem5::ArmISA::si, and gem5::X86ISA::val.

◆ setNotAnInst()

|

inline |

Definition at line 422 of file dyn_inst.hh.

◆ setPinnedRegsRenamed()

|

inline |

Sets the destination registers as renamed.

Definition at line 944 of file dyn_inst.hh.

References PinnedRegsRenamed, PinnedRegsSquashDone, PinnedRegsWritten, and status.

Referenced by renameDestReg().

◆ setPinnedRegsSquashDone()

|

inline |

Sets dest registers' status updated after squash.

Definition at line 972 of file dyn_inst.hh.

References PinnedRegsSquashDone, and status.

Referenced by setSquashed().

◆ setPinnedRegsWritten()

|

inline |

Sets destination registers as written.

Definition at line 956 of file dyn_inst.hh.

References PinnedRegsRenamed, PinnedRegsSquashDone, PinnedRegsWritten, and status.

◆ setPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 996 of file dyn_inst.hh.

References instFlags, Predicate, gem5::Trace::InstRecord::setPredicate(), traceData, and gem5::X86ISA::val.

◆ setPredTaken()

|

inline |

Definition at line 571 of file dyn_inst.hh.

◆ setPredTarg()

|

inline |

Set the predicted target of this current instruction.

Definition at line 554 of file dyn_inst.hh.

References predPC.

◆ setRequest()

|

inline |

Assert this instruction has generated a memory request.

Definition at line 1034 of file dyn_inst.hh.

◆ setResultReady()

|

inline |

Marks the result as ready.

Definition at line 832 of file dyn_inst.hh.

References ResultReady, and status.

◆ setScalarResult()

|

inline |

Pushes a result onto the instResult queue.

Scalar result.

Definition at line 777 of file dyn_inst.hh.

References instFlags, instResult, RecordResult, gem5::InstResult::Scalar, and gem5::ArmISA::t.

Referenced by setCCRegOperand(), setFloatRegOperandBits(), and setIntRegOperand().

◆ setSerializeAfter()

|

inline |

Temporarily sets this instruction as a serialize after instruction.

Definition at line 698 of file dyn_inst.hh.

References SerializeAfter, and status.

◆ setSerializeBefore()

|

inline |

Temporarily sets this instruction as a serialize before instruction.

Definition at line 689 of file dyn_inst.hh.

References SerializeBefore, and status.

◆ setSerializeHandled()

|

inline |

Sets the serialization part of this instruction as handled.

Definition at line 707 of file dyn_inst.hh.

References SerializeHandled, and status.

◆ setSquashed()

| void gem5::o3::DynInst::setSquashed | ( | ) |

Sets this instruction as squashed.

Definition at line 203 of file dyn_inst.cc.

References gem5::PhysRegId::incrNumPinnedWrites(), gem5::PhysRegId::incrNumPinnedWritesToComplete(), gem5::PhysRegId::isPinned(), isPinnedRegsRenamed(), isPinnedRegsSquashDone(), isPinnedRegsWritten(), numDestRegs(), regs, gem5::o3::DynInst::Regs::renamedDestIdx(), setPinnedRegsSquashDone(), Squashed, and status.

◆ setSquashedInIQ()

|

inline |

Sets this instruction as squashed in the IQ.

Definition at line 898 of file dyn_inst.hh.

References Squashed, SquashedInIQ, and status.

◆ setSquashedInLSQ()

|

inline |

Sets this instruction as squashed in the LSQ.

Definition at line 916 of file dyn_inst.hh.

References Squashed, SquashedInLSQ, and status.

◆ setSquashedInROB()

|

inline |

Sets this instruction as squashed in the ROB.

Definition at line 934 of file dyn_inst.hh.

References SquashedInROB, and status.

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements gem5::ExecContext.

Definition at line 1052 of file dyn_inst.hh.

References gem5::ThreadState::storeCondFailures, and thread.

◆ setThreadState()

|

inline |

Sets the pointer to the thread state.

Definition at line 1021 of file dyn_inst.hh.

References thread.

◆ setTid()

|

inline |

◆ setVecElemOperand()

|

inlineoverridevirtual |

Sets a vector register to a value.

Implements gem5::ExecContext.

Definition at line 1309 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::renamedDestIdx(), gem5::o3::CPU::setVecElem(), setVecElemResult(), and gem5::X86ISA::val.

Referenced by forwardOldRegs().

◆ setVecElemResult()

|

inline |

Vector element result.

Definition at line 799 of file dyn_inst.hh.

References instFlags, instResult, RecordResult, gem5::ArmISA::t, and gem5::InstResult::VecElem.

Referenced by setVecElemOperand().

◆ setVecPredRegOperand()

|

inlineoverridevirtual |

Sets a destination predicate register operand to a value.

Implements gem5::ExecContext.

Definition at line 1318 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::renamedDestIdx(), gem5::o3::CPU::setVecPredReg(), setVecPredResult(), and gem5::X86ISA::val.

Referenced by forwardOldRegs().

◆ setVecPredResult()

|

inline |

Predicate result.

Definition at line 810 of file dyn_inst.hh.

References instFlags, instResult, RecordResult, gem5::ArmISA::t, and gem5::InstResult::VecPredReg.

Referenced by setVecPredRegOperand().

◆ setVecRegOperand()

|

inlineoverridevirtual |

Sets a destination vector register operand to a value.

Implements gem5::ExecContext.

Definition at line 1301 of file dyn_inst.hh.

References gem5::o3::DynInst::Regs::renamedDestIdx(), gem5::o3::CPU::setVecReg(), setVecResult(), and gem5::X86ISA::val.

Referenced by forwardOldRegs().

◆ setVecResult()

|

inline |

Full vector result.

Definition at line 788 of file dyn_inst.hh.

References instFlags, instResult, RecordResult, gem5::ArmISA::t, and gem5::InstResult::VecReg.

Referenced by setVecRegOperand().

◆ socketId()

|

inline |

Read this CPU's Socket ID.

Definition at line 532 of file dyn_inst.hh.

References cpu, and gem5::BaseCPU::socketId().

◆ srcRegIdx()

|

inline |

Returns the logical register index of the i'th source register.

Definition at line 753 of file dyn_inst.hh.

References gem5::ArmISA::i, gem5::StaticInst::srcRegIdx(), and staticInst.

◆ strictlyOrdered() [1/2]

|

inline |

Is this instruction's memory access strictly ordered?

Definition at line 1028 of file dyn_inst.hh.

References instFlags, and IsStrictlyOrdered.

◆ strictlyOrdered() [2/2]

|

inline |

Definition at line 1029 of file dyn_inst.hh.

References instFlags, IsStrictlyOrdered, and gem5::PowerISA::so.

◆ tcBase()

|

inlineoverridevirtual |

Returns the thread context.

Implements gem5::ExecContext.

Definition at line 1024 of file dyn_inst.hh.

References gem5::o3::ThreadState::getTC(), and thread.

◆ translationCompleted() [1/2]

|

inline |

True if the DTB address translation has completed.

Definition at line 455 of file dyn_inst.hh.

References instFlags, and TranslationCompleted.

Referenced by isTranslationDelayed().

◆ translationCompleted() [2/2]

|

inline |

Definition at line 459 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and TranslationCompleted.

◆ translationStarted() [1/2]

|

inline |

True if the DTB address translation has started.

Definition at line 450 of file dyn_inst.hh.

References instFlags, and TranslationStarted.

Referenced by isTranslationDelayed().

◆ translationStarted() [2/2]

|

inline |

Definition at line 451 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and TranslationStarted.

◆ trap()

| void gem5::o3::DynInst::trap | ( | const Fault & | fault | ) |

Traps to handle specified fault.

Definition at line 285 of file dyn_inst.cc.

References cpu, staticInst, threadNumber, and gem5::o3::CPU::trap().

◆ updateMiscRegs()

|

inline |

Called at the commit stage to update the misc.

registers.

Definition at line 1158 of file dyn_inst.hh.

References _destMiscRegIdx, _destMiscRegVal, gem5::ArmISA::i, gem5::o3::ThreadState::noSquashFromTC, and gem5::o3::CPU::setMiscReg().

◆ writeMem()

|

override |

Definition at line 310 of file dyn_inst.cc.

References gem5::X86ISA::addr, cpu, data, and gem5::o3::CPU::pushRequest().

Member Data Documentation

◆ _destMiscRegIdx

|

protected |

Indexes of the destination misc.

registers. They are needed to defer the write accesses to the misc. registers until the commit stage, when the instruction is out of its speculative state.

Definition at line 194 of file dyn_inst.hh.

Referenced by setMiscReg(), and updateMiscRegs().

◆ _destMiscRegVal

|

protected |

Values to be written to the destination misc.

registers.

Definition at line 188 of file dyn_inst.hh.

Referenced by setMiscReg(), and updateMiscRegs().

◆ cpu

| CPU* gem5::o3::DynInst::cpu = nullptr |

Pointer to the Impl's CPU object.

Definition at line 108 of file dyn_inst.hh.

Referenced by armMonitor(), completeAcc(), cpuId(), demapPage(), DynInst(), getAddrMonitor(), getCpuPtr(), initiateHtmCmd(), initiateMemAMO(), initiateMemRead(), mwait(), mwaitAtomic(), requestorId(), socketId(), trap(), writeMem(), and ~DynInst().

◆ effAddr

| Addr gem5::o3::DynInst::effAddr = 0 |

The effective virtual address (lds & stores only).

Definition at line 375 of file dyn_inst.hh.

◆ effSize

| unsigned gem5::o3::DynInst::effSize |

The size of the request.

Definition at line 384 of file dyn_inst.hh.

◆ fault

The kind of fault this instruction has generated.

Definition at line 116 of file dyn_inst.hh.

Referenced by completeAcc(), execute(), getFault(), initiateAcc(), and ~DynInst().

◆ firstIssue

| Tick gem5::o3::DynInst::firstIssue = -1 |

Definition at line 1101 of file dyn_inst.hh.

◆ htmDepth

|

private |

Definition at line 1083 of file dyn_inst.hh.

Referenced by clearHtmTransactionalState(), getHtmTransactionalDepth(), and setHtmTransactionalState().

◆ htmUid

|

private |

Definition at line 1082 of file dyn_inst.hh.

Referenced by clearHtmTransactionalState(), getHtmTransactionUid(), and setHtmTransactionalState().

◆ instFlags

|

private |

Definition at line 173 of file dyn_inst.hh.

Referenced by clearHtmTransactionalState(), DynInst(), effAddrValid(), getHtmTransactionUid(), hasRequest(), hitExternalSnoop(), inHtmTransactionalState(), memOpDone(), notAnInst(), possibleLoadViolation(), readMemAccPredicate(), readPredicate(), readPredTaken(), recordResult(), setHtmTransactionalState(), setMemAccPredicate(), setNotAnInst(), setPredicate(), setPredTaken(), setRequest(), setScalarResult(), setVecElemResult(), setVecPredResult(), setVecResult(), strictlyOrdered(), translationCompleted(), and translationStarted().

◆ instListIt

| ListIt gem5::o3::DynInst::instListIt |

Iterator pointing to this BaseDynInst in the list of all insts.

Definition at line 360 of file dyn_inst.hh.

Referenced by getInstListIt(), and setInstListIt().

◆ instResult

|

protected |

The result of the instruction; assumes an instruction can have many destination registers.

Definition at line 182 of file dyn_inst.hh.

Referenced by popResult(), resultSize(), setScalarResult(), setVecElemResult(), setVecPredResult(), and setVecResult().

◆ lastWakeDependents

| Tick gem5::o3::DynInst::lastWakeDependents = -1 |

Definition at line 1102 of file dyn_inst.hh.

◆ lqIdx

| ssize_t gem5::o3::DynInst::lqIdx = -1 |

Load queue index.

Definition at line 390 of file dyn_inst.hh.

◆ lqIt

| LSQUnit::LQIterator gem5::o3::DynInst::lqIt |

Definition at line 391 of file dyn_inst.hh.

◆ macroop

| const StaticInstPtr gem5::o3::DynInst::macroop |

The Macroop if one exists.

Definition at line 367 of file dyn_inst.hh.

◆ memData

| uint8_t* gem5::o3::DynInst::memData = nullptr |

Pointer to the data for the memory access.

Definition at line 387 of file dyn_inst.hh.

Referenced by ~DynInst().

◆ memReqFlags

| unsigned gem5::o3::DynInst::memReqFlags = 0 |

The memory request flags (from translation).

Definition at line 381 of file dyn_inst.hh.

◆ pc

|

protected |

PC state for this instruction.

Definition at line 185 of file dyn_inst.hh.

Referenced by branchTarget(), dump(), instAddr(), microPC(), mispredicted(), nextInstAddr(), and pcState().

◆ physEffAddr

| Addr gem5::o3::DynInst::physEffAddr = 0 |

The effective physical address.

Definition at line 378 of file dyn_inst.hh.

◆ predPC

| TheISA::PCState gem5::o3::DynInst::predPC |

Predicted PC state after this instruction.

Definition at line 364 of file dyn_inst.hh.

Referenced by mispredicted(), predInstAddr(), predMicroPC(), predNextInstAddr(), readPredTarg(), and setPredTarg().

◆ readyRegs

| uint8_t gem5::o3::DynInst::readyRegs = 0 |

How many source registers are ready.

Definition at line 370 of file dyn_inst.hh.

Referenced by markSrcRegReady().

◆ regs

| Regs gem5::o3::DynInst::regs |

Definition at line 354 of file dyn_inst.hh.

Referenced by DynInst(), markSrcRegReady(), numDestRegs(), numSrcRegs(), renameDestReg(), renameSrcReg(), and setSquashed().

◆ reqToVerify

| RequestPtr gem5::o3::DynInst::reqToVerify |

Definition at line 407 of file dyn_inst.hh.

Referenced by completeAcc().

◆ savedReq

| LSQ::LSQRequest* gem5::o3::DynInst::savedReq |

Saved memory request (needed when the DTB address translation is delayed due to a hw page table walk).

Definition at line 403 of file dyn_inst.hh.

◆ seqNum

| InstSeqNum gem5::o3::DynInst::seqNum = 0 |

The sequence number of the instruction.

Definition at line 102 of file dyn_inst.hh.

Referenced by gem5::o3::DependencyGraph< gem5::RefCountingPtr >::dump(), DynInst(), markSrcRegReady(), and ~DynInst().

◆ sqIdx

| ssize_t gem5::o3::DynInst::sqIdx = -1 |

Store queue index.

Definition at line 394 of file dyn_inst.hh.

◆ sqIt

| LSQUnit::SQIterator gem5::o3::DynInst::sqIt |

Definition at line 395 of file dyn_inst.hh.

◆ staticInst

| const StaticInstPtr gem5::o3::DynInst::staticInst |

The StaticInst used by this BaseDynInst.

Definition at line 105 of file dyn_inst.hh.

Referenced by branchTarget(), completeAcc(), destRegIdx(), dump(), execute(), initiateAcc(), isAtomic(), isCall(), isCondCtrl(), isControl(), isDataPrefetch(), isDelayedCommit(), isDirectCtrl(), isFirstMicroop(), isFloating(), isFullMemBarrier(), isHtmCancel(), isHtmCmd(), isHtmStart(), isHtmStop(), isIndirectCtrl(), isInstPrefetch(), isInteger(), isLastMicroop(), isLoad(), isMacroop(), isMemRef(), isMicroop(), isNonSpeculative(), isNop(), isQuiesce(), isReadBarrier(), isReturn(), isSerializeAfter(), isSerializeBefore(), isSerializing(), isSquashAfter(), isStore(), isStoreConditional(), isSyscall(), isUncondCtrl(), isUnverifiable(), isVector(), isWriteBarrier(), mispredicted(), numCCDestRegs(), numFPDestRegs(), numIntDestRegs(), numVecDestRegs(), numVecElemDestRegs(), numVecPredDestRegs(), opClass(), srcRegIdx(), trap(), and ~DynInst().

◆ status

|

private |

The status of this BaseDynInst.

Several bits can be set.

Definition at line 176 of file dyn_inst.hh.

Referenced by clearCanCommit(), clearCanIssue(), clearInIQ(), clearInROB(), clearIssued(), clearSerializeAfter(), clearSerializeBefore(), DynInst(), isAtCommit(), isCommitted(), isCompleted(), isExecuted(), isInIQ(), isInLSQ(), isInROB(), isIssued(), isPinnedRegsRenamed(), isPinnedRegsSquashDone(), isPinnedRegsWritten(), isResultReady(), isSerializeAfter(), isSerializeBefore(), isSerializeHandled(), isSquashed(), isSquashedInIQ(), isSquashedInLSQ(), isSquashedInROB(), isTempSerializeAfter(), isTempSerializeBefore(), readyToCommit(), readyToIssue(), removeInLSQ(), setAtCommit(), setCanCommit(), setCanIssue(), setCommitted(), setCompleted(), setExecuted(), setInIQ(), setInLSQ(), setInROB(), setIssued(), setPinnedRegsRenamed(), setPinnedRegsSquashDone(), setPinnedRegsWritten(), setResultReady(), setSerializeAfter(), setSerializeBefore(), setSerializeHandled(), setSquashed(), setSquashedInIQ(), setSquashedInLSQ(), and setSquashedInROB().

◆ thread

| ThreadState* gem5::o3::DynInst::thread = nullptr |

Pointer to the thread state.

Definition at line 113 of file dyn_inst.hh.

Referenced by completeAcc(), contextId(), execute(), initiateAcc(), readStCondFailures(), setStCondFailures(), setThreadState(), and tcBase().

◆ threadNumber

| ThreadID gem5::o3::DynInst::threadNumber = 0 |

The thread this instruction is from.

Definition at line 357 of file dyn_inst.hh.

Referenced by armMonitor(), dump(), getAddrMonitor(), mwait(), mwaitAtomic(), setTid(), and trap().

◆ traceData

| Trace::InstRecord* gem5::o3::DynInst::traceData = nullptr |

InstRecord that tracks this instructions.

Definition at line 119 of file dyn_inst.hh.