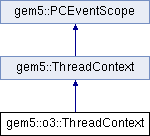

Derived ThreadContext class for use with the O3CPU. More...

#include <thread_context.hh>

Public Member Functions | |

| bool | schedule (PCEvent *e) override |

| bool | remove (PCEvent *e) override |

| void | scheduleInstCountEvent (Event *event, Tick count) override |

| void | descheduleInstCountEvent (Event *event) override |

| Tick | getCurrentInstCount () override |

| BaseMMU * | getMMUPtr () override |

| Returns a pointer to the MMU. More... | |

| CheckerCPU * | getCheckerCpuPtr () override |

| BaseISA * | getIsaPtr () override |

| TheISA::Decoder * | getDecoderPtr () override |

| BaseCPU * | getCpuPtr () override |

| Returns a pointer to this CPU. More... | |

| int | cpuId () const override |

| Reads this CPU's ID. More... | |

| uint32_t | socketId () const override |

| Reads this CPU's Socket ID. More... | |

| ContextID | contextId () const override |

| void | setContextId (ContextID id) override |

| int | threadId () const override |

| Returns this thread's ID number. More... | |

| void | setThreadId (int id) override |

| System * | getSystemPtr () override |

| Returns a pointer to the system. More... | |

| Process * | getProcessPtr () override |

| Returns a pointer to this thread's process. More... | |

| void | setProcessPtr (Process *p) override |

| PortProxy & | getVirtProxy () override |

| void | initMemProxies (gem5::ThreadContext *tc) override |

| Initialise the physical and virtual port proxies and tie them to the data port of the CPU. More... | |

| Status | status () const override |

| Returns this thread's status. More... | |

| void | setStatus (Status new_status) override |

| Sets this thread's status. More... | |

| void | activate () override |

| Set the status to Active. More... | |

| void | suspend () override |

| Set the status to Suspended. More... | |

| void | halt () override |

| Set the status to Halted. More... | |

| void | takeOverFrom (gem5::ThreadContext *old_context) override |

| Takes over execution of a thread from another CPU. More... | |

| Tick | readLastActivate () override |

| Reads the last tick that this thread was activated on. More... | |

| Tick | readLastSuspend () override |

| Reads the last tick that this thread was suspended on. More... | |

| void | copyArchRegs (gem5::ThreadContext *tc) override |

| Copies the architectural registers from another TC into this TC. More... | |

| void | clearArchRegs () override |

| Resets all architectural registers to 0. More... | |

| RegVal | readReg (RegIndex reg_idx) |

| Reads an integer register. More... | |

| RegVal | readIntReg (RegIndex reg_idx) const override |

| RegVal | readFloatReg (RegIndex reg_idx) const override |

| const TheISA::VecRegContainer & | readVecReg (const RegId &id) const override |

| TheISA::VecRegContainer & | getWritableVecReg (const RegId &id) override |

| Read vector register operand for modification, hierarchical indexing. More... | |

| const TheISA::VecElem & | readVecElem (const RegId ®) const override |

| const TheISA::VecPredRegContainer & | readVecPredReg (const RegId &id) const override |

| TheISA::VecPredRegContainer & | getWritableVecPredReg (const RegId &id) override |

| RegVal | readCCReg (RegIndex reg_idx) const override |

| void | setIntReg (RegIndex reg_idx, RegVal val) override |

| Sets an integer register to a value. More... | |

| void | setFloatReg (RegIndex reg_idx, RegVal val) override |

| void | setVecReg (const RegId ®, const TheISA::VecRegContainer &val) override |

| void | setVecElem (const RegId ®, const TheISA::VecElem &val) override |

| void | setVecPredReg (const RegId ®, const TheISA::VecPredRegContainer &val) override |

| void | setCCReg (RegIndex reg_idx, RegVal val) override |

| TheISA::PCState | pcState () const override |

| Reads this thread's PC state. More... | |

| void | pcState (const TheISA::PCState &val) override |

| Sets this thread's PC state. More... | |

| void | pcStateNoRecord (const TheISA::PCState &val) override |

| Addr | instAddr () const override |

| Reads this thread's PC. More... | |

| Addr | nextInstAddr () const override |

| Reads this thread's next PC. More... | |

| MicroPC | microPC () const override |

| Reads this thread's next PC. More... | |

| RegVal | readMiscRegNoEffect (RegIndex misc_reg) const override |

| Reads a miscellaneous register. More... | |

| RegVal | readMiscReg (RegIndex misc_reg) override |

| Reads a misc. More... | |

| void | setMiscRegNoEffect (RegIndex misc_reg, RegVal val) override |

| Sets a misc. More... | |

| void | setMiscReg (RegIndex misc_reg, RegVal val) override |

| Sets a misc. More... | |

| RegId | flattenRegId (const RegId ®Id) const override |

| unsigned | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. More... | |

| void | setStCondFailures (unsigned sc_failures) override |

| Sets the number of consecutive store conditional failures. More... | |

| void | conditionalSquash () |

| check if the cpu is currently in state update mode and squash if not. More... | |

| RegVal | readIntRegFlat (RegIndex idx) const override |

| Flat register interfaces. More... | |

| void | setIntRegFlat (RegIndex idx, RegVal val) override |

| RegVal | readFloatRegFlat (RegIndex idx) const override |

| void | setFloatRegFlat (RegIndex idx, RegVal val) override |

| const TheISA::VecRegContainer & | readVecRegFlat (RegIndex idx) const override |

| TheISA::VecRegContainer & | getWritableVecRegFlat (RegIndex idx) override |

| Read vector register operand for modification, flat indexing. More... | |

| void | setVecRegFlat (RegIndex idx, const TheISA::VecRegContainer &val) override |

| const TheISA::VecElem & | readVecElemFlat (RegIndex idx, const ElemIndex &elemIndex) const override |

| void | setVecElemFlat (RegIndex idx, const ElemIndex &elemIdx, const TheISA::VecElem &val) override |

| const TheISA::VecPredRegContainer & | readVecPredRegFlat (RegIndex idx) const override |

| TheISA::VecPredRegContainer & | getWritableVecPredRegFlat (RegIndex idx) override |

| void | setVecPredRegFlat (RegIndex idx, const TheISA::VecPredRegContainer &val) override |

| RegVal | readCCRegFlat (RegIndex idx) const override |

| void | setCCRegFlat (RegIndex idx, RegVal val) override |

| void | htmAbortTransaction (uint64_t htm_uid, HtmFailureFaultCause cause) override |

| BaseHTMCheckpointPtr & | getHtmCheckpointPtr () override |

| void | setHtmCheckpointPtr (BaseHTMCheckpointPtr new_cpt) override |

Public Member Functions inherited from gem5::ThreadContext Public Member Functions inherited from gem5::ThreadContext | |

| bool | getUseForClone () |

| void | setUseForClone (bool new_val) |

| virtual | ~ThreadContext () |

| virtual void | sendFunctional (PacketPtr pkt) |

| void | quiesce () |

| Quiesce thread context. More... | |

| void | quiesceTick (Tick resume) |

| Quiesce, suspend, and schedule activate at resume. More... | |

| virtual void | regStats (const std::string &name) |

| void | setNPC (Addr val) |

| virtual int | exit () |

Public Attributes | |

| CPU * | cpu |

| Pointer to the CPU. More... | |

| ThreadState * | thread |

| Pointer to the thread state that this TC corrseponds to. More... | |

Public Attributes inherited from gem5::ThreadContext Public Attributes inherited from gem5::ThreadContext | |

| int | intResult = DefaultIntResult |

| double | floatResult = DefaultFloatResult |

| int | intOffset = 0 |

Additional Inherited Members | |

Public Types inherited from gem5::ThreadContext Public Types inherited from gem5::ThreadContext | |

| enum | Status { Active, Suspended, Halting, Halted } |

Static Public Member Functions inherited from gem5::ThreadContext Static Public Member Functions inherited from gem5::ThreadContext | |

| static void | compare (ThreadContext *one, ThreadContext *two) |

| function to compare two thread contexts (for debugging) More... | |

Static Public Attributes inherited from gem5::ThreadContext Static Public Attributes inherited from gem5::ThreadContext | |

| static const int | ints [] |

| static const double | floats [] |

| static const int | DefaultIntResult = 0 |

| static const double | DefaultFloatResult = 0.0 |

Protected Attributes inherited from gem5::ThreadContext Protected Attributes inherited from gem5::ThreadContext | |

| bool | useForClone = false |

Detailed Description

Derived ThreadContext class for use with the O3CPU.

It provides the interface for any external objects to access a single thread's state and some general CPU state. Any time external objects try to update state through this interface, the CPU will create an event to squash all in-flight instructions in order to ensure state is maintained correctly. It must be defined specifically for the O3CPU because not all architectural state is located within the ThreadState (such as the commit PC, and registers), and specific actions must be taken when using this interface (such as squashing all in-flight instructions when doing a write to this interface).

Definition at line 68 of file thread_context.hh.

Member Function Documentation

◆ activate()

|

overridevirtual |

Set the status to Active.

Implements gem5::ThreadContext.

Definition at line 76 of file thread_context.cc.

References gem5::o3::CPU::activateContext(), gem5::ThreadContext::Active, cpu, gem5::curTick(), DPRINTF, gem5::ThreadState::lastActivate, gem5::ThreadState::setStatus(), gem5::ThreadState::status(), thread, gem5::ThreadState::threadId(), and threadId().

◆ clearArchRegs()

|

overridevirtual |

Resets all architectural registers to 0.

Implements gem5::ThreadContext.

Definition at line 156 of file thread_context.cc.

References cpu, gem5::o3::CPU::isa, thread, and gem5::ThreadState::threadId().

◆ conditionalSquash()

|

inline |

check if the cpu is currently in state update mode and squash if not.

This function will return true if a trap is pending or if a fault or similar is currently writing to the thread context and doesn't want reset all the state (see noSquashFromTC).

Definition at line 365 of file thread_context.hh.

References cpu, gem5::o3::ThreadState::noSquashFromTC, gem5::o3::CPU::squashFromTC(), thread, gem5::ThreadState::threadId(), and gem5::o3::ThreadState::trapPending.

Referenced by htmAbortTransaction(), pcState(), pcStateNoRecord(), setCCRegFlat(), setFloatRegFlat(), setIntRegFlat(), setMiscReg(), setMiscRegNoEffect(), setVecElemFlat(), setVecPredRegFlat(), and setVecRegFlat().

◆ contextId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 130 of file thread_context.hh.

References gem5::ThreadState::contextId(), and thread.

◆ copyArchRegs()

|

overridevirtual |

Copies the architectural registers from another TC into this TC.

Implements gem5::ThreadContext.

Definition at line 144 of file thread_context.cc.

References gem5::BaseISA::copyRegsFrom(), cpu, getIsaPtr(), gem5::ThreadContext::getIsaPtr(), gem5::o3::ThreadState::noSquashFromTC, thread, gem5::BaseISA::vecRegRenameMode(), and gem5::o3::CPU::vecRenameMode().

◆ cpuId()

|

inlineoverridevirtual |

Reads this CPU's ID.

Implements gem5::ThreadContext.

Definition at line 125 of file thread_context.hh.

References cpu, and gem5::BaseCPU::cpuId().

◆ descheduleInstCountEvent()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 91 of file thread_context.hh.

References gem5::o3::ThreadState::comInstEventQueue, gem5::EventQueue::deschedule(), gem5::MipsISA::event, and thread.

◆ flattenRegId()

Implements gem5::ThreadContext.

Definition at line 276 of file thread_context.cc.

References cpu, gem5::o3::CPU::isa, thread, and gem5::ThreadState::threadId().

Referenced by getWritableVecPredReg(), getWritableVecReg(), readCCReg(), readFloatReg(), readIntReg(), readReg(), readVecElem(), readVecPredReg(), readVecReg(), setCCReg(), setFloatReg(), setIntReg(), setVecElem(), setVecPredReg(), and setVecReg().

◆ getCheckerCpuPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 107 of file thread_context.hh.

◆ getCpuPtr()

|

inlineoverridevirtual |

Returns a pointer to this CPU.

Implements gem5::ThreadContext.

Definition at line 122 of file thread_context.hh.

References cpu.

◆ getCurrentInstCount()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 96 of file thread_context.hh.

References gem5::o3::ThreadState::comInstEventQueue, gem5::EventQueue::getCurTick(), and thread.

◆ getDecoderPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 116 of file thread_context.hh.

References cpu, gem5::o3::Fetch::decoder, gem5::o3::CPU::fetch, thread, and gem5::ThreadState::threadId().

Referenced by takeOverFrom().

◆ getHtmCheckpointPtr()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 308 of file thread_context.cc.

References gem5::o3::ThreadState::htmCheckpoint, and thread.

◆ getIsaPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 110 of file thread_context.hh.

References cpu, gem5::o3::CPU::isa, thread, and gem5::ThreadState::threadId().

Referenced by copyArchRegs(), and takeOverFrom().

◆ getMMUPtr()

|

inlineoverridevirtual |

Returns a pointer to the MMU.

Implements gem5::ThreadContext.

Definition at line 105 of file thread_context.hh.

References cpu, and gem5::o3::CPU::mmu.

◆ getProcessPtr()

|

inlineoverridevirtual |

Returns a pointer to this thread's process.

Implements gem5::ThreadContext.

Definition at line 142 of file thread_context.hh.

References gem5::ThreadState::getProcessPtr(), and thread.

◆ getSystemPtr()

|

inlineoverridevirtual |

Returns a pointer to the system.

Implements gem5::ThreadContext.

Definition at line 139 of file thread_context.hh.

References cpu, and gem5::o3::CPU::system.

◆ getVirtProxy()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 55 of file thread_context.cc.

References gem5::ThreadState::getVirtProxy(), and thread.

◆ getWritableVecPredReg()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 236 of file thread_context.hh.

References flattenRegId(), getWritableVecPredRegFlat(), and gem5::MipsISA::index.

◆ getWritableVecPredRegFlat()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 198 of file thread_context.cc.

References cpu, gem5::o3::CPU::getWritableArchVecPredReg(), thread, and gem5::ThreadState::threadId().

Referenced by getWritableVecPredReg().

◆ getWritableVecReg()

|

inlineoverridevirtual |

Read vector register operand for modification, hierarchical indexing.

Implements gem5::ThreadContext.

Definition at line 218 of file thread_context.hh.

References flattenRegId(), getWritableVecRegFlat(), and gem5::MipsISA::index.

◆ getWritableVecRegFlat()

|

overridevirtual |

Read vector register operand for modification, flat indexing.

Implements gem5::ThreadContext.

Definition at line 180 of file thread_context.cc.

References cpu, gem5::o3::CPU::getWritableArchVecReg(), thread, and gem5::ThreadState::threadId().

Referenced by getWritableVecReg().

◆ halt()

|

overridevirtual |

Set the status to Halted.

Implements gem5::ThreadContext.

Definition at line 113 of file thread_context.cc.

References gem5::o3::CPU::addThreadToExitingList(), cpu, DPRINTF, gem5::ThreadContext::Halted, gem5::ThreadContext::Halting, gem5::ThreadState::setStatus(), gem5::ThreadState::status(), thread, gem5::ThreadState::threadId(), and threadId().

◆ htmAbortTransaction()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 299 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::htmSendAbortSignal(), thread, and gem5::ThreadState::threadId().

◆ initMemProxies()

|

inlineoverridevirtual |

Initialise the physical and virtual port proxies and tie them to the data port of the CPU.

tc ThreadContext for the virtual-to-physical translation

Implements gem5::ThreadContext.

Definition at line 149 of file thread_context.hh.

References gem5::ThreadState::initMemProxies(), and thread.

◆ instAddr()

|

inlineoverridevirtual |

Reads this thread's PC.

Implements gem5::ThreadContext.

Definition at line 301 of file thread_context.hh.

References cpu, gem5::o3::CPU::instAddr(), thread, and gem5::ThreadState::threadId().

◆ microPC()

|

inlineoverridevirtual |

Reads this thread's next PC.

Implements gem5::ThreadContext.

Definition at line 315 of file thread_context.hh.

References cpu, gem5::o3::CPU::microPC(), thread, and gem5::ThreadState::threadId().

◆ nextInstAddr()

|

inlineoverridevirtual |

Reads this thread's next PC.

Implements gem5::ThreadContext.

Definition at line 308 of file thread_context.hh.

References cpu, gem5::o3::CPU::nextInstAddr(), thread, and gem5::ThreadState::threadId().

◆ pcState() [1/2]

|

inlineoverridevirtual |

Reads this thread's PC state.

Implements gem5::ThreadContext.

Definition at line 289 of file thread_context.hh.

References cpu, gem5::o3::CPU::pcState(), thread, and gem5::ThreadState::threadId().

◆ pcState() [2/2]

|

overridevirtual |

Sets this thread's PC state.

Implements gem5::ThreadContext.

Definition at line 260 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::pcState(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

◆ pcStateNoRecord()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 268 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::pcState(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

◆ readCCReg()

Implements gem5::ThreadContext.

Definition at line 242 of file thread_context.hh.

References gem5::CCRegClass, flattenRegId(), gem5::MipsISA::index, and readCCRegFlat().

◆ readCCRegFlat()

Implements gem5::ThreadContext.

Definition at line 204 of file thread_context.cc.

References cpu, gem5::o3::CPU::readArchCCReg(), thread, and gem5::ThreadState::threadId().

Referenced by readCCReg().

◆ readFloatReg()

Implements gem5::ThreadContext.

Definition at line 202 of file thread_context.hh.

References flattenRegId(), gem5::FloatRegClass, gem5::MipsISA::index, and readFloatRegFlat().

◆ readFloatRegFlat()

Implements gem5::ThreadContext.

Definition at line 168 of file thread_context.cc.

References cpu, gem5::o3::CPU::readArchFloatReg(), thread, and gem5::ThreadState::threadId().

Referenced by readFloatReg().

◆ readIntReg()

Implements gem5::ThreadContext.

Definition at line 195 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, gem5::IntRegClass, and readIntRegFlat().

◆ readIntRegFlat()

Flat register interfaces.

Some architectures have different registers visible in different modes. Such architectures "flatten" a register (see flattenRegId()) to map it into the gem5 register file. This interface provides a flat interface to the underlying register file, which allows for example serialization code to access all registers.

Implements gem5::ThreadContext.

Definition at line 162 of file thread_context.cc.

References cpu, gem5::o3::CPU::readArchIntReg(), thread, and gem5::ThreadState::threadId().

Referenced by readIntReg(), and readReg().

◆ readLastActivate()

|

overridevirtual |

Reads the last tick that this thread was activated on.

Implements gem5::ThreadContext.

Definition at line 132 of file thread_context.cc.

References gem5::ThreadState::lastActivate, and thread.

◆ readLastSuspend()

|

overridevirtual |

Reads the last tick that this thread was suspended on.

Implements gem5::ThreadContext.

Definition at line 138 of file thread_context.cc.

References gem5::ThreadState::lastSuspend, and thread.

◆ readMiscReg()

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements gem5::ThreadContext.

Definition at line 330 of file thread_context.hh.

References cpu, gem5::o3::CPU::readMiscReg(), thread, and gem5::ThreadState::threadId().

◆ readMiscRegNoEffect()

|

inlineoverridevirtual |

Reads a miscellaneous register.

Implements gem5::ThreadContext.

Definition at line 322 of file thread_context.hh.

References cpu, gem5::o3::CPU::readMiscRegNoEffect(), thread, and gem5::ThreadState::threadId().

◆ readReg()

Reads an integer register.

Definition at line 189 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, gem5::IntRegClass, and readIntRegFlat().

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements gem5::ThreadContext.

Definition at line 347 of file thread_context.hh.

References gem5::ThreadState::storeCondFailures, and thread.

◆ readVecElem()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 224 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, readVecElemFlat(), and gem5::X86ISA::reg.

◆ readVecElemFlat()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 186 of file thread_context.cc.

References cpu, gem5::o3::CPU::readArchVecElem(), thread, and gem5::ThreadState::threadId().

Referenced by readVecElem().

◆ readVecPredReg()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 230 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, and readVecPredRegFlat().

◆ readVecPredRegFlat()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 192 of file thread_context.cc.

References cpu, gem5::o3::CPU::readArchVecPredReg(), thread, and gem5::ThreadState::threadId().

Referenced by readVecPredReg().

◆ readVecReg()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 209 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, and readVecRegFlat().

◆ readVecRegFlat()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 174 of file thread_context.cc.

References cpu, gem5::o3::CPU::readArchVecReg(), thread, and gem5::ThreadState::threadId().

Referenced by readVecReg().

◆ remove()

|

inlineoverridevirtual |

Implements gem5::PCEventScope.

Definition at line 80 of file thread_context.hh.

References gem5::ArmISA::e, gem5::o3::ThreadState::pcEventQueue, gem5::PCEventQueue::remove(), and thread.

◆ schedule()

|

inlineoverridevirtual |

Implements gem5::PCEventScope.

Definition at line 75 of file thread_context.hh.

References gem5::ArmISA::e, gem5::o3::ThreadState::pcEventQueue, gem5::PCEventQueue::schedule(), and thread.

◆ scheduleInstCountEvent()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 86 of file thread_context.hh.

References gem5::o3::ThreadState::comInstEventQueue, gem5::X86ISA::count, gem5::MipsISA::event, gem5::EventQueue::schedule(), and thread.

◆ setCCReg()

Implements gem5::ThreadContext.

Definition at line 282 of file thread_context.hh.

References gem5::CCRegClass, flattenRegId(), gem5::MipsISA::index, setCCRegFlat(), and gem5::X86ISA::val.

◆ setCCRegFlat()

Implements gem5::ThreadContext.

Definition at line 252 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setArchCCReg(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

Referenced by setCCReg().

◆ setContextId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 132 of file thread_context.hh.

References gem5::ThreadState::setContextId(), and thread.

◆ setFloatReg()

Implements gem5::ThreadContext.

Definition at line 256 of file thread_context.hh.

References flattenRegId(), gem5::FloatRegClass, gem5::MipsISA::index, setFloatRegFlat(), and gem5::X86ISA::val.

◆ setFloatRegFlat()

Implements gem5::ThreadContext.

Definition at line 218 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setArchFloatReg(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

Referenced by setFloatReg().

◆ setHtmCheckpointPtr()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 314 of file thread_context.cc.

References gem5::o3::ThreadState::htmCheckpoint, and thread.

◆ setIntReg()

Sets an integer register to a value.

Implements gem5::ThreadContext.

Definition at line 250 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, gem5::IntRegClass, setIntRegFlat(), and gem5::X86ISA::val.

◆ setIntRegFlat()

Implements gem5::ThreadContext.

Definition at line 210 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setArchIntReg(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

Referenced by setIntReg().

◆ setMiscReg()

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Implements gem5::ThreadContext.

Definition at line 290 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setMiscReg(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

◆ setMiscRegNoEffect()

Sets a misc.

register.

Implements gem5::ThreadContext.

Definition at line 282 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setMiscRegNoEffect(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

◆ setProcessPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 144 of file thread_context.hh.

References gem5::MipsISA::p, gem5::ThreadState::setProcessPtr(), and thread.

◆ setStatus()

|

inlineoverridevirtual |

Sets this thread's status.

Implements gem5::ThreadContext.

Definition at line 159 of file thread_context.hh.

References gem5::ThreadState::setStatus(), and thread.

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements gem5::ThreadContext.

Definition at line 354 of file thread_context.hh.

References gem5::ThreadState::storeCondFailures, and thread.

◆ setThreadId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 136 of file thread_context.hh.

References gem5::ThreadState::setThreadId(), and thread.

◆ setVecElem()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 269 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, gem5::X86ISA::reg, setVecElemFlat(), and gem5::X86ISA::val.

◆ setVecElemFlat()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 235 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setArchVecElem(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

Referenced by setVecElem().

◆ setVecPredReg()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 275 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, gem5::X86ISA::reg, setVecPredRegFlat(), and gem5::X86ISA::val.

◆ setVecPredRegFlat()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 243 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setArchVecPredReg(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

Referenced by setVecPredReg().

◆ setVecReg()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 263 of file thread_context.hh.

References flattenRegId(), gem5::MipsISA::index, gem5::X86ISA::reg, setVecRegFlat(), and gem5::X86ISA::val.

◆ setVecRegFlat()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 226 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::o3::CPU::setArchVecReg(), thread, gem5::ThreadState::threadId(), and gem5::X86ISA::val.

Referenced by setVecReg().

◆ socketId()

|

inlineoverridevirtual |

Reads this CPU's Socket ID.

Implements gem5::ThreadContext.

Definition at line 128 of file thread_context.hh.

References cpu, and gem5::BaseCPU::socketId().

◆ status()

|

inlineoverridevirtual |

Returns this thread's status.

Implements gem5::ThreadContext.

Definition at line 155 of file thread_context.hh.

References gem5::ThreadState::status(), and thread.

◆ suspend()

|

overridevirtual |

Set the status to Suspended.

Implements gem5::ThreadContext.

Definition at line 92 of file thread_context.cc.

References cpu, gem5::curTick(), DPRINTF, gem5::o3::CPU::isDraining(), gem5::ThreadState::lastActivate, gem5::ThreadState::lastSuspend, gem5::ThreadState::setStatus(), gem5::ThreadState::status(), gem5::o3::CPU::suspendContext(), gem5::ThreadContext::Suspended, thread, gem5::ThreadState::threadId(), and threadId().

◆ takeOverFrom()

|

overridevirtual |

Takes over execution of a thread from another CPU.

Implements gem5::ThreadContext.

Definition at line 61 of file thread_context.cc.

References getDecoderPtr(), gem5::ThreadContext::getDecoderPtr(), getIsaPtr(), gem5::o3::ThreadState::noSquashFromTC, gem5::BaseISA::takeOverFrom(), gem5::takeOverFrom(), thread, and gem5::o3::ThreadState::trapPending.

◆ threadId()

|

inlineoverridevirtual |

Returns this thread's ID number.

Implements gem5::ThreadContext.

Definition at line 135 of file thread_context.hh.

References thread, and gem5::ThreadState::threadId().

Referenced by activate(), halt(), and suspend().

Member Data Documentation

◆ cpu

| CPU* gem5::o3::ThreadContext::cpu |

Pointer to the CPU.

Definition at line 72 of file thread_context.hh.

Referenced by activate(), clearArchRegs(), conditionalSquash(), copyArchRegs(), cpuId(), flattenRegId(), getCpuPtr(), getDecoderPtr(), getIsaPtr(), getMMUPtr(), getSystemPtr(), getWritableVecPredRegFlat(), getWritableVecRegFlat(), halt(), htmAbortTransaction(), instAddr(), microPC(), nextInstAddr(), pcState(), pcStateNoRecord(), readCCRegFlat(), readFloatRegFlat(), readIntRegFlat(), readMiscReg(), readMiscRegNoEffect(), readVecElemFlat(), readVecPredRegFlat(), readVecRegFlat(), setCCRegFlat(), setFloatRegFlat(), setIntRegFlat(), setMiscReg(), setMiscRegNoEffect(), setVecElemFlat(), setVecPredRegFlat(), setVecRegFlat(), socketId(), and suspend().

◆ thread

| ThreadState* gem5::o3::ThreadContext::thread |

Pointer to the thread state that this TC corrseponds to.

Definition at line 102 of file thread_context.hh.

Referenced by activate(), clearArchRegs(), conditionalSquash(), contextId(), copyArchRegs(), descheduleInstCountEvent(), flattenRegId(), getCurrentInstCount(), getDecoderPtr(), getHtmCheckpointPtr(), getIsaPtr(), getProcessPtr(), getVirtProxy(), getWritableVecPredRegFlat(), getWritableVecRegFlat(), halt(), htmAbortTransaction(), initMemProxies(), instAddr(), microPC(), nextInstAddr(), pcState(), pcStateNoRecord(), readCCRegFlat(), readFloatRegFlat(), readIntRegFlat(), readLastActivate(), readLastSuspend(), readMiscReg(), readMiscRegNoEffect(), readStCondFailures(), readVecElemFlat(), readVecPredRegFlat(), readVecRegFlat(), remove(), schedule(), scheduleInstCountEvent(), setCCRegFlat(), setContextId(), setFloatRegFlat(), setHtmCheckpointPtr(), setIntRegFlat(), setMiscReg(), setMiscRegNoEffect(), setProcessPtr(), setStatus(), setStCondFailures(), setThreadId(), setVecElemFlat(), setVecPredRegFlat(), setVecRegFlat(), status(), suspend(), takeOverFrom(), and threadId().

The documentation for this class was generated from the following files:

- cpu/o3/thread_context.hh

- cpu/o3/thread_context.cc