#include <remote_gdb.hh>

Classes | |

| struct | GEM5_PACKED |

| RISC-V Register Cache Order and sizes of registers found in ext/gdb-xml/riscv.xml To add support for more CSRs: More... | |

Public Member Functions | |

| char * | data () const |

| Return the pointer to the raw bytes buffer containing the register values. | |

| size_t | size () const |

| Return the size of the raw buffer, in bytes (i.e., half of the number of digits in the g/G packet). | |

| void | getRegs (ThreadContext *) |

| Fill the raw buffer from the registers in the ThreadContext. | |

| void | setRegs (ThreadContext *) const |

| Set the ThreadContext's registers from the values in the raw buffer. | |

| const std::string | name () const |

| Return the name to use in places like DPRINTF. | |

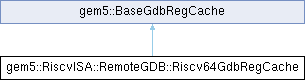

Public Member Functions inherited from gem5::BaseGdbRegCache Public Member Functions inherited from gem5::BaseGdbRegCache | |

| virtual char * | data () const =0 |

| Return the pointer to the raw bytes buffer containing the register values. | |

| virtual size_t | size () const =0 |

| Return the size of the raw buffer, in bytes (i.e., half of the number of digits in the g/G packet). | |

| virtual void | getRegs (ThreadContext *)=0 |

| Fill the raw buffer from the registers in the ThreadContext. | |

| virtual void | setRegs (ThreadContext *) const =0 |

| Set the ThreadContext's registers from the values in the raw buffer. | |

| virtual const std::string | name () const =0 |

| Return the name to use in places like DPRINTF. | |

| BaseGdbRegCache (BaseRemoteGDB *g) | |

| virtual | ~BaseGdbRegCache () |

Private Member Functions | |

| BaseGdbRegCache (BaseRemoteGDB *g) | |

Private Attributes | |

| struct gem5::RiscvISA::RemoteGDB::Riscv64GdbRegCache::GEM5_PACKED | r |

Additional Inherited Members | |

Protected Attributes inherited from gem5::BaseGdbRegCache Protected Attributes inherited from gem5::BaseGdbRegCache | |

| BaseRemoteGDB * | gdb |

Detailed Description

Definition at line 147 of file remote_gdb.hh.

Member Function Documentation

◆ BaseGdbRegCache()

|

inlineprivate |

Definition at line 134 of file remote_gdb.hh.

◆ data()

|

inlinevirtual |

Return the pointer to the raw bytes buffer containing the register values.

Each byte of this buffer is literally encoded as two hex digits in the g or G RSP packet.

Implements gem5::BaseGdbRegCache.

Definition at line 219 of file remote_gdb.hh.

References r.

◆ getRegs()

|

virtual |

Fill the raw buffer from the registers in the ThreadContext.

Implements gem5::BaseGdbRegCache.

Definition at line 420 of file remote_gdb.cc.

References gem5::ThreadContext::contextId(), gem5::RiscvISA::CSR_CYCLE, gem5::RiscvISA::CSR_FCSR, gem5::RiscvISA::CSR_FFLAGS, gem5::RiscvISA::CSR_FRM, gem5::RiscvISA::CSR_MARCHID, gem5::RiscvISA::CSR_MCAUSE, gem5::RiscvISA::CSR_MCOUNTEREN, gem5::RiscvISA::CSR_MEDELEG, gem5::RiscvISA::CSR_MEPC, gem5::RiscvISA::CSR_MIDELEG, gem5::RiscvISA::CSR_MIE, gem5::RiscvISA::CSR_MIMPID, gem5::RiscvISA::CSR_MIP, gem5::RiscvISA::CSR_MISA, gem5::RiscvISA::CSR_MSCRATCH, gem5::RiscvISA::CSR_MSTATUS, gem5::RiscvISA::CSR_MTVAL, gem5::RiscvISA::CSR_MTVEC, gem5::RiscvISA::CSR_MVENDORID, gem5::RiscvISA::CSR_SATP, gem5::RiscvISA::CSR_SCAUSE, gem5::RiscvISA::CSR_SCOUNTEREN, gem5::RiscvISA::CSR_SEDELEG, gem5::RiscvISA::CSR_SEPC, gem5::RiscvISA::CSR_SIDELEG, gem5::RiscvISA::CSR_SIE, gem5::RiscvISA::CSR_SIP, gem5::RiscvISA::CSR_SSCRATCH, gem5::RiscvISA::CSR_SSTATUS, gem5::RiscvISA::CSR_STVAL, gem5::RiscvISA::CSR_STVEC, gem5::RiscvISA::CSR_TIME, gem5::RiscvISA::CSR_UCAUSE, gem5::RiscvISA::CSR_UEPC, gem5::RiscvISA::CSR_UIE, gem5::RiscvISA::CSR_UIP, gem5::RiscvISA::CSR_USCRATCH, gem5::RiscvISA::CSR_USTATUS, gem5::RiscvISA::CSR_UTVAL, gem5::RiscvISA::CSR_UTVEC, gem5::RiscvISA::CSRData, gem5::RiscvISA::CSRMasks, DPRINTF, gem5::X86ISA::floatRegClass, gem5::ThreadContext::getReg(), gem5::ArmISA::i, gem5::PCStateBase::instAddr(), gem5::ArmISA::intRegClass, gem5::ThreadContext::pcState(), gem5::ThreadContext::readMiscReg(), gem5::ThreadContext::readMiscRegNoEffect(), and gem5::RiscvISA::RV64.

◆ name()

|

inlinevirtual |

Return the name to use in places like DPRINTF.

Having each concrete superclass redefine this member is useful in situations where the class of the regCache can change on the fly.

Implements gem5::BaseGdbRegCache.

Definition at line 225 of file remote_gdb.hh.

References gem5::BaseGdbRegCache::gdb, and gem5::BaseRemoteGDB::name().

◆ setRegs()

|

virtual |

Set the ThreadContext's registers from the values in the raw buffer.

Implements gem5::BaseGdbRegCache.

Definition at line 528 of file remote_gdb.cc.

References gem5::RiscvISA::CSR_FCSR, gem5::RiscvISA::CSR_FFLAGS, gem5::RiscvISA::CSR_FRM, gem5::RiscvISA::CSR_MCAUSE, gem5::RiscvISA::CSR_MCOUNTEREN, gem5::RiscvISA::CSR_MEDELEG, gem5::RiscvISA::CSR_MEPC, gem5::RiscvISA::CSR_MIDELEG, gem5::RiscvISA::CSR_MIE, gem5::RiscvISA::CSR_MIP, gem5::RiscvISA::CSR_MISA, gem5::RiscvISA::CSR_MSCRATCH, gem5::RiscvISA::CSR_MSTATUS, gem5::RiscvISA::CSR_MTVAL, gem5::RiscvISA::CSR_MTVEC, gem5::RiscvISA::CSR_SATP, gem5::RiscvISA::CSR_SCAUSE, gem5::RiscvISA::CSR_SCOUNTEREN, gem5::RiscvISA::CSR_SEDELEG, gem5::RiscvISA::CSR_SEPC, gem5::RiscvISA::CSR_SIDELEG, gem5::RiscvISA::CSR_SIE, gem5::RiscvISA::CSR_SIP, gem5::RiscvISA::CSR_SSCRATCH, gem5::RiscvISA::CSR_SSTATUS, gem5::RiscvISA::CSR_STVAL, gem5::RiscvISA::CSR_STVEC, gem5::RiscvISA::CSR_UCAUSE, gem5::RiscvISA::CSR_UEPC, gem5::RiscvISA::CSR_UIE, gem5::RiscvISA::CSR_UIP, gem5::RiscvISA::CSR_USCRATCH, gem5::RiscvISA::CSR_USTATUS, gem5::RiscvISA::CSR_UTVAL, gem5::RiscvISA::CSR_UTVEC, gem5::RiscvISA::CSRData, DPRINTF, gem5::X86ISA::floatRegClass, gem5::ArmISA::i, gem5::ArmISA::intRegClass, gem5::ThreadContext::pcState(), gem5::RiscvISA::RV64, gem5::ThreadContext::setMiscRegNoEffect(), gem5::ThreadContext::setReg(), gem5::setRegNoEffectWithMask(), and gem5::setRegWithMask().

◆ size()

|

inlinevirtual |

Return the size of the raw buffer, in bytes (i.e., half of the number of digits in the g/G packet).

Implements gem5::BaseGdbRegCache.

Definition at line 220 of file remote_gdb.hh.

References r.

Member Data Documentation

◆ r

|

private |

The documentation for this class was generated from the following files:

- arch/riscv/remote_gdb.hh

- arch/riscv/remote_gdb.cc