gem5::PrimaryQueue Struct Reference

#include <pm4_queues.hh>

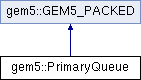

Inheritance diagram for gem5::PrimaryQueue:

Public Attributes | |

| union { | |

| struct { | |

| uint32_t queueRptrAddrLo | |

| uint32_t queueRptrAddrHi | |

| } | |

| Addr queueRptrAddr | |

| }; | |

| union { | |

| struct { | |

| uint32_t queueWptrLo | |

| uint32_t queueWptrHi | |

| } | |

| Addr queueWptr | |

| }; | |

| uint32_t | doorbellOffset |

| uint32_t | doorbellRangeLo |

| uint32_t | doorbellRangeHi |

| Public Attributes inherited from gem5::GEM5_PACKED | |

| union { | |

| struct { | |

| uint16_t predicated: 1 | |

| uint16_t shader: 1 | |

| uint16_t reserved: 6 | |

| uint16_t opcode: 8 | |

| uint16_t count: 14 | |

| uint16_t type: 2 | |

| } | |

| uint32_t ordinal | |

| }; | |

| uint32_t | reserved1: 8 |

| uint32_t | destSel: 4 |

| uint32_t | reserved2: 4 |

| uint32_t | addrIncr: 1 |

| uint32_t | reserved3: 2 |

| uint32_t | resume: 1 |

| uint32_t | writeConfirm: 1 |

| uint32_t | reserved4: 4 |

| uint32_t | cachePolicy: 2 |

| uint32_t | reserved5: 5 |

| union { | |

| struct { | |

| uint32_t destAddrLo | |

| uint32_t destAddrHi | |

| } | |

| uint64_t destAddr | |

| }; | |

| uint32_t | data |

| uint32_t | queueSel: 2 |

| uint32_t | vmid: 4 |

| uint32_t | queueSlot: 3 |

| uint32_t | pipe: 2 |

| uint32_t | me: 1 |

| uint32_t | reserved6: 2 |

| uint32_t | queueType: 3 |

| uint32_t | allocFormat: 2 |

| uint32_t | engineSel: 3 |

| uint32_t | numQueues: 3 |

| uint32_t | checkDisable: 1 |

| uint32_t | doorbellOffset: 26 |

| union { | |

| struct { | |

| uint32_t mqdAddrLo: 32 | |

| uint32_t mqdAddrHi: 32 | |

| } | |

| uint64_t mqdAddr | |

| }; | |

| union { | |

| struct { | |

| uint32_t wptrAddrLo: 32 | |

| uint32_t wptrAddrHi: 32 | |

| } | |

| uint64_t wptrAddr | |

| }; | |

| uint32_t | action: 2 |

| uint32_t | reserved: 2 |

| union { | |

| struct { | |

| uint32_t pasid: 16 | |

| uint32_t reserved2: 16 | |

| } | |

| struct { | |

| uint32_t reserved3: 2 | |

| uint32_t doorbellOffset0: 26 | |

| uint32_t reserved4: 4 | |

| } | |

| }; | |

| uint32_t | doorbellOffset1: 26 |

| uint32_t | reserved7: 2 |

| uint32_t | doorbellOffset2: 26 |

| uint32_t | reserved8: 4 |

| uint32_t | reserved9: 2 |

| uint32_t | doorbellOffset3: 26 |

| uint32_t | reserved10: 4 |

| uint32_t | vmidMask: 16 |

| uint32_t | unmapLatency: 8 |

| union { | |

| struct { | |

| uint32_t queueMaskLo | |

| uint32_t queueMaskHi | |

| } | |

| uint64_t queueMask | |

| }; | |

| union { | |

| struct { | |

| uint32_t gwsMaskLo | |

| uint32_t gwsMaskHi | |

| } | |

| uint64_t gwsMask | |

| }; | |

| uint16_t | oacMask |

| uint16_t | reserved1 |

| uint32_t | gdsHeapBase: 6 |

| uint32_t | gdsHeapSize: 6 |

| uint32_t | reserved0: 8 |

| uint32_t | diq: 1 |

| uint32_t | processQuantum: 7 |

| union { | |

| struct { | |

| uint32_t ptBaseLo | |

| uint32_t ptBaseHi | |

| } | |

| uint64_t ptBase | |

| }; | |

| uint32_t | shMemBases |

| uint32_t | shMemConfig |

| union { | |

| struct { | |

| uint32_t gdsAddrLo | |

| uint32_t gdsAddrHi | |

| } | |

| uint64_t gdsAddr | |

| }; | |

| uint32_t | numGws: 6 |

| uint32_t | numOac: 4 |

| uint32_t | gdsSize: 6 |

| union { | |

| struct { | |

| uint32_t completionSignalLo | |

| uint32_t completionSignalHi | |

| } | |

| uint64_t completionSignal | |

| }; | |

| union { | |

| struct { | |

| uint32_t ptBaseLo | |

| uint32_t ptBaseHi | |

| } | |

| uint64_t ptBase | |

| }; | |

| uint32_t | sqShaderTbaLo |

| uint32_t | sqShaderTbaHi |

| uint32_t | sqShaderTmaLo |

| uint32_t | sqShaderTmaHi |

| union { | |

| struct { | |

| uint32_t gdsAddrLo | |

| uint32_t gdsAddrHi | |

| } | |

| uint64_t gdsAddr | |

| }; | |

| union { | |

| struct { | |

| uint32_t numGws: 7 | |

| uint32_t sdma_enable: 1 | |

| uint32_t numOac: 4 | |

| uint32_t reserved3: 4 | |

| uint32_t gdsSize: 6 | |

| uint32_t numQueues: 10 | |

| } | |

| uint32_t ordinal14 | |

| }; | |

| uint32_t | spiGdbgPerVmidCntl |

| uint32_t | tcpWatchCntl [4] |

| union { | |

| struct { | |

| uint32_t completionSignalLo | |

| uint32_t completionSignalHi | |

| } | |

| uint64_t completionSignal | |

| }; | |

| uint32_t | function: 4 |

| uint32_t | memSpace: 2 |

| uint32_t | operation: 2 |

| union { | |

| struct { | |

| uint32_t regAddr1: 18 | |

| uint32_t reserved2: 14 | |

| } | |

| uint32_t memAddrLo | |

| }; | |

| union { | |

| struct { | |

| uint32_t regAddr2: 18 | |

| uint32_t reserved3: 14 | |

| } | |

| uint32_t memAddrHi | |

| }; | |

| uint32_t | reference |

| uint32_t | mask |

| uint32_t | pollInterval |

| uint32_t | regOffset: 16 |

| uint32_t | regData |

| union { | |

| struct { | |

| uint32_t ibBaseLo | |

| uint32_t ibBaseHi | |

| } | |

| uint64_t ibBase | |

| }; | |

| uint32_t | ibSize: 20 |

| uint32_t | chain: 1 |

| uint32_t | poll: 1 |

| uint32_t | valid: 1 |

| uint32_t | priv: 1 |

| union { | |

| struct { | |

| uint32_t tmz: 1 | |

| uint32_t reserved: 31 | |

| } | |

| uint32_t dummy | |

| }; | |

| union { | |

| struct { | |

| uint32_t ibBaseLo | |

| uint32_t ibBaseHi | |

| } | |

| uint64_t ibBase | |

| }; | |

| uint32_t | ena: 1 |

| uint32_t | preResume: 1 |

| uint32_t | command: 4 |

| uint32_t | event: 6 |

| uint32_t | eventIdx: 4 |

| uint32_t | l1Volatile: 1 |

| uint32_t | l2Volatile: 1 |

| uint32_t | l2WB: 1 |

| uint32_t | l1Inv: 1 |

| uint32_t | l2Inv: 1 |

| uint32_t | l2NC: 1 |

| uint32_t | l2WC: 1 |

| uint32_t | l2Meta: 1 |

| uint32_t | execute: 1 |

| uint32_t | destSelect: 2 |

| uint32_t | intSelect: 3 |

| uint32_t | dataSelect: 3 |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| uint64_t addr | |

| }; | |

| union { | |

| struct { | |

| union { | |

| struct { | |

| uint32_t dwOffset: 16 | |

| uint32_t numDws: 16 | |

| } | |

| uint32_t dataLo: 32 | |

| } | |

| uint32_t dataHi | |

| } | |

| uint64_t data | |

| }; | |

| uint32_t | intCtxId |

| uint32_t | offset: 16 |

| union { | |

| struct { | |

| uint32_t ibBaseLo | |

| uint32_t ibBaseHi | |

| } | |

| uint64_t ibBase | |

| }; | |

| uint32_t | offleadPolling: 1 |

| uint32_t | processCnt: 4 |

| uint32_t | contextId: 28 |

| uint32_t | interruptSel: 2 |

| union { | |

| struct { | |

| uint32_t pasid: 16 | |

| uint32_t reserved0: 16 | |

| } | |

| struct { | |

| uint32_t reserved1: 2 | |

| uint32_t doorbellOffset: 26 | |

| uint32_t engineSel: 3 | |

| uint32_t reserved2: 1 | |

| } | |

| }; | |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| uint64_t addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t dataLo | |

| uint32_t dataHi | |

| } | |

| uint64_t data | |

| }; | |

| union { | |

| struct { | |

| uint32_t cp_mqd_readindex_lo | |

| uint32_t cp_mqd_readindex_hi | |

| } | |

| uint64_t mqdReadIndex | |

| }; | |

| uint32_t | cp_mqd_save_start_time_lo |

| uint32_t | cp_mqd_save_start_time_hi |

| uint32_t | cp_mqd_save_end_time_lo |

| uint32_t | cp_mqd_save_end_time_hi |

| uint32_t | cp_mqd_restore_start_time_lo |

| uint32_t | cp_mqd_restore_start_time_hi |

| uint32_t | cp_mqd_restore_end_time_lo |

| uint32_t | cp_mqd_restore_end_time_hi |

| uint32_t | disable_queue |

| uint32_t | reserved_107 |

| uint32_t | gds_cs_ctxsw_cnt0 |

| uint32_t | gds_cs_ctxsw_cnt1 |

| uint32_t | gds_cs_ctxsw_cnt2 |

| uint32_t | gds_cs_ctxsw_cnt3 |

| uint32_t | reserved_112 |

| uint32_t | reserved_113 |

| uint32_t | cp_pq_exe_status_lo |

| uint32_t | cp_pq_exe_status_hi |

| uint32_t | cp_packet_id_lo |

| uint32_t | cp_packet_id_hi |

| uint32_t | cp_packet_exe_status_lo |

| uint32_t | cp_packet_exe_status_hi |

| uint32_t | gds_save_base_addr_lo |

| uint32_t | gds_save_base_addr_hi |

| uint32_t | gds_save_mask_lo |

| uint32_t | gds_save_mask_hi |

| uint32_t | ctx_save_base_addr_lo |

| uint32_t | ctx_save_base_addr_hi |

| uint32_t | dynamic_cu_mask_addr_lo |

| uint32_t | dynamic_cu_mask_addr_hi |

| union { | |

| struct { | |

| uint32_t mqd_base_addr_lo | |

| uint32_t mqd_base_addr_hi | |

| } | |

| uint64_t mqdBase | |

| }; | |

| uint32_t | hqd_active |

| uint32_t | hqd_vmid |

| uint32_t | hqd_persistent_state |

| uint32_t | hqd_pipe_priority |

| uint32_t | hqd_queue_priority |

| uint32_t | hqd_quantum |

| union { | |

| struct { | |

| uint32_t hqd_pq_base_lo | |

| uint32_t hqd_pq_base_hi | |

| } | |

| uint64_t base | |

| }; | |

| union { | |

| uint32_t hqd_pq_rptr | |

| uint32_t rptr | |

| }; | |

| union { | |

| struct { | |

| uint32_t hqd_pq_rptr_report_addr_lo | |

| uint32_t hqd_pq_rptr_report_addr_hi | |

| } | |

| uint64_t aqlRptr | |

| }; | |

| uint32_t | hqd_pq_wptr_poll_addr_lo |

| uint32_t | hqd_pq_wptr_poll_addr_hi |

| union { | |

| uint32_t hqd_pq_doorbell_control | |

| uint32_t doorbell | |

| }; | |

| uint32_t | reserved_144 |

| uint32_t | hqd_pq_control |

| union { | |

| struct { | |

| uint32_t hqd_ib_base_addr_lo | |

| uint32_t hqd_ib_base_addr_hi | |

| } | |

| Addr ibBase | |

| }; | |

| union { | |

| uint32_t hqd_ib_rptr | |

| uint32_t ibRptr | |

| }; | |

| uint32_t | hqd_ib_control |

| uint32_t | hqd_iq_timer |

| uint32_t | hqd_iq_rptr |

| uint32_t | cp_hqd_dequeue_request |

| uint32_t | cp_hqd_dma_offload |

| uint32_t | cp_hqd_sema_cmd |

| uint32_t | cp_hqd_msg_type |

| uint32_t | cp_hqd_atomic0_preop_lo |

| uint32_t | cp_hqd_atomic0_preop_hi |

| uint32_t | cp_hqd_atomic1_preop_lo |

| uint32_t | cp_hqd_atomic1_preop_hi |

| uint32_t | cp_hqd_hq_status0 |

| uint32_t | cp_hqd_hq_control0 |

| uint32_t | cp_mqd_control |

| uint32_t | cp_hqd_hq_status1 |

| uint32_t | cp_hqd_hq_control1 |

| uint32_t | cp_hqd_eop_base_addr_lo |

| uint32_t | cp_hqd_eop_base_addr_hi |

| uint32_t | cp_hqd_eop_control |

| uint32_t | cp_hqd_eop_rptr |

| uint32_t | cp_hqd_eop_wptr |

| uint32_t | cp_hqd_eop_done_events |

| uint32_t | cp_hqd_ctx_save_base_addr_lo |

| uint32_t | cp_hqd_ctx_save_base_addr_hi |

| uint32_t | cp_hqd_ctx_save_control |

| uint32_t | cp_hqd_cntl_stack_offset |

| uint32_t | cp_hqd_cntl_stack_size |

| uint32_t | cp_hqd_wg_state_offset |

| uint32_t | cp_hqd_ctx_save_size |

| uint32_t | cp_hqd_gds_resource_state |

| uint32_t | cp_hqd_error |

| uint32_t | cp_hqd_eop_wptr_mem |

| union { | |

| uint32_t cp_hqd_aql_control | |

| uint32_t aql | |

| }; | |

| uint32_t | cp_hqd_pq_wptr_lo |

| uint32_t | cp_hqd_pq_wptr_hi |

| uint32_t | sdmax_rlcx_rb_cntl |

| union { | |

| struct { | |

| uint32_t sdmax_rlcx_rb_base | |

| uint32_t sdmax_rlcx_rb_base_hi | |

| } | |

| uint64_t rb_base | |

| }; | |

| union { | |

| struct { | |

| uint32_t sdmax_rlcx_rb_rptr | |

| uint32_t sdmax_rlcx_rb_rptr_hi | |

| } | |

| uint64_t rptr | |

| }; | |

| union { | |

| struct { | |

| uint32_t sdmax_rlcx_rb_wptr | |

| uint32_t sdmax_rlcx_rb_wptr_hi | |

| } | |

| uint64_t wptr | |

| }; | |

| uint32_t | sdmax_rlcx_rb_wptr_poll_cntl |

| uint32_t | sdmax_rlcx_rb_rptr_addr_hi |

| uint32_t | sdmax_rlcx_rb_rptr_addr_lo |

| uint32_t | sdmax_rlcx_ib_cntl |

| uint32_t | sdmax_rlcx_ib_rptr |

| uint32_t | sdmax_rlcx_ib_offset |

| uint32_t | sdmax_rlcx_ib_base_lo |

| uint32_t | sdmax_rlcx_ib_base_hi |

| uint32_t | sdmax_rlcx_ib_size |

| uint32_t | sdmax_rlcx_skip_cntl |

| uint32_t | sdmax_rlcx_context_status |

| uint32_t | sdmax_rlcx_doorbell |

| uint32_t | sdmax_rlcx_status |

| uint32_t | sdmax_rlcx_doorbell_log |

| uint32_t | sdmax_rlcx_watermark |

| uint32_t | sdmax_rlcx_doorbell_offset |

| uint32_t | sdmax_rlcx_csa_addr_lo |

| uint32_t | sdmax_rlcx_csa_addr_hi |

| uint32_t | sdmax_rlcx_ib_sub_remain |

| uint32_t | sdmax_rlcx_preempt |

| uint32_t | sdmax_rlcx_dummy_reg |

| uint32_t | sdmax_rlcx_rb_wptr_poll_addr_hi |

| uint32_t | sdmax_rlcx_rb_wptr_poll_addr_lo |

| uint32_t | sdmax_rlcx_rb_aql_cntl |

| uint32_t | sdmax_rlcx_minor_ptr_update |

| uint32_t | sdmax_rlcx_midcmd_data0 |

| uint32_t | sdmax_rlcx_midcmd_data1 |

| uint32_t | sdmax_rlcx_midcmd_data2 |

| uint32_t | sdmax_rlcx_midcmd_data3 |

| uint32_t | sdmax_rlcx_midcmd_data4 |

| uint32_t | sdmax_rlcx_midcmd_data5 |

| uint32_t | sdmax_rlcx_midcmd_data6 |

| uint32_t | sdmax_rlcx_midcmd_data7 |

| uint32_t | sdmax_rlcx_midcmd_data8 |

| uint32_t | sdmax_rlcx_midcmd_cntl |

| uint32_t | reserved_42 |

| uint32_t | reserved_43 |

| uint32_t | reserved_44 |

| uint32_t | reserved_45 |

| uint32_t | reserved_46 |

| uint32_t | reserved_47 |

| uint32_t | reserved_48 |

| uint32_t | reserved_49 |

| uint32_t | reserved_50 |

| uint32_t | reserved_51 |

| uint32_t | reserved_52 |

| uint32_t | reserved_53 |

| uint32_t | reserved_54 |

| uint32_t | reserved_55 |

| uint32_t | reserved_56 |

| uint32_t | reserved_57 |

| uint32_t | reserved_58 |

| uint32_t | reserved_59 |

| uint32_t | reserved_60 |

| uint32_t | reserved_61 |

| uint32_t | reserved_62 |

| uint32_t | reserved_63 |

| uint32_t | reserved_64 |

| uint32_t | reserved_65 |

| uint32_t | reserved_66 |

| uint32_t | reserved_67 |

| uint32_t | reserved_68 |

| uint32_t | reserved_69 |

| uint32_t | reserved_70 |

| uint32_t | reserved_71 |

| uint32_t | reserved_72 |

| uint32_t | reserved_73 |

| uint32_t | reserved_74 |

| uint32_t | reserved_75 |

| uint32_t | reserved_76 |

| uint32_t | reserved_77 |

| uint32_t | reserved_78 |

| uint32_t | reserved_79 |

| uint32_t | reserved_80 |

| uint32_t | reserved_81 |

| uint32_t | reserved_82 |

| uint32_t | reserved_83 |

| uint32_t | reserved_84 |

| uint32_t | reserved_85 |

| uint32_t | reserved_86 |

| uint32_t | reserved_87 |

| uint32_t | reserved_88 |

| uint32_t | reserved_89 |

| uint32_t | reserved_90 |

| uint32_t | reserved_91 |

| uint32_t | reserved_92 |

| uint32_t | reserved_93 |

| uint32_t | reserved_94 |

| uint32_t | reserved_95 |

| uint32_t | reserved_96 |

| uint32_t | reserved_97 |

| uint32_t | reserved_98 |

| uint32_t | reserved_99 |

| uint32_t | reserved_100 |

| uint32_t | reserved_101 |

| uint32_t | reserved_102 |

| uint32_t | reserved_103 |

| uint32_t | reserved_104 |

| uint32_t | reserved_105 |

| uint32_t | reserved_106 |

| uint32_t | reserved_108 |

| uint32_t | reserved_109 |

| uint32_t | reserved_110 |

| uint32_t | reserved_111 |

| uint32_t | reserved_114 |

| uint32_t | reserved_115 |

| uint32_t | reserved_116 |

| uint32_t | reserved_117 |

| uint32_t | reserved_118 |

| uint32_t | reserved_119 |

| uint32_t | reserved_120 |

| uint32_t | reserved_121 |

| uint32_t | reserved_122 |

| uint32_t | reserved_123 |

| uint32_t | reserved_124 |

| uint32_t | reserved_125 |

| uint32_t | sdma_engine_id |

| uint32_t | sdma_queue_id |

| uint32_t | count: 30 |

| uint32_t | res0: 2 |

| uint32_t | res1: 16 |

| uint32_t | sdw: 2 |

| uint32_t | res2: 6 |

| uint32_t | ddw: 2 |

| uint32_t | res3: 6 |

| uint64_t | source |

| uint64_t | dest |

| uint32_t | sw: 2 |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| uint32_t | srcData |

| uint32_t | unused: 10 |

| union { | |

| struct { | |

| uint32_t op: 8 | |

| uint32_t sub_op: 8 | |

| uint32_t sw: 2 | |

| uint32_t res0: 12 | |

| uint32_t fillsize: 2 | |

| } | |

| uint32_t ordinal | |

| }; | |

| uint32_t | key0 |

| uint32_t | key1 |

| uint32_t | key2 |

| uint32_t | key3 |

| uint32_t | count0 |

| uint32_t | count1 |

| uint32_t | count2 |

| uint32_t | count3 |

| uint32_t | countData0 |

| uint32_t | countData1 |

| uint32_t | countData2 |

| uint32_t | countData3 |

| uint32_t | countKey0 |

| uint32_t | countKey1 |

| uint32_t | countKey2 |

| uint32_t | countKey3 |

| uint32_t | size: 20 |

| uint64_t | csaAddr |

| union { | |

| struct { | |

| uint32_t contextId: 3 | |

| uint32_t rbRptr: 13 | |

| uint32_t ibOffset: 12 | |

| uint32_t reserved: 4 | |

| } | |

| uint32_t intrContext | |

| }; | |

| union { | |

| struct { | |

| uint32_t reserved: 3 | |

| uint32_t addrLo: 29 | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t reserved: 3 | |

| uint32_t addrLo: 29 | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| uint32_t | regAddr: 18 |

| uint32_t | apertureId: 12 |

| union { | |

| struct { | |

| uint32_t reserved: 28 | |

| uint32_t byteEnable: 4 | |

| } | |

| uint32_t ordinal | |

| }; | |

| uint64_t | address |

| uint32_t | ref |

| uint32_t | pollInt: 16 |

| uint32_t | retryCount: 12 |

| union { | |

| struct { | |

| uint32_t reserved: 26 | |

| uint32_t op: 2 | |

| uint32_t func: 3 | |

| uint32_t mode: 1 | |

| } | |

| uint32_t ordinal | |

| }; | |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t execCount: 14 | |

| uint32_t unused: 18 | |

| } | |

| uint32_t ordinal | |

| }; | |

| union { | |

| struct { | |

| uint32_t addrLo | |

| uint32_t addrHi | |

| } | |

| Addr addr | |

| }; | |

| union { | |

| struct { | |

| uint32_t srcDataLo | |

| uint32_t srdDataHi | |

| } | |

| uint64_t srcData | |

| }; | |

| union { | |

| struct { | |

| uint32_t cmpDataLo | |

| uint32_t cmpDataHi | |

| } | |

| uint64_t cmpData | |

| }; | |

| uint32_t | loopInt: 13 |

| union { | |

| struct { | |

| int unused2: 16 | |

| int loop: 1 | |

| int unused1: 8 | |

| int opcode: 7 | |

| } | |

| uint32_t ordinal | |

| }; | |

| uint64_t | mask |

| uint64_t | initValue |

| uint64_t | increment |

| union { | |

| struct { | |

| uint32_t initDataLo | |

| uint32_t initDataHi | |

| } | |

| uint64_t initData | |

| }; | |

| uint32_t | opcode: 8 |

| uint32_t | subOpcode: 8 |

| uint32_t | device: 8 |

| uint32_t | byteStride |

| uint32_t | dmaCount |

| union { | |

| struct { | |

| uint32_t destLo | |

| uint32_t destHi | |

| } | |

| uint64_t dest | |

| }; | |

| uint32_t | byteCount: 26 |

| uint16_t | format: 8 |

| uint16_t | barrier: 1 |

| uint16_t | acqFenceScope: 2 |

| uint16_t | relFenceScope: 2 |

| sdmaHeaderAgentDisp | header |

| uint16_t | res0 |

| union { | |

| struct { | |

| uint32_t retLo | |

| uint32_t retHi | |

| } | |

| Addr ret | |

| }; | |

| uint32_t | swDest: 2 |

| uint32_t | res4: 6 |

| uint32_t | swSrc: 2 |

| union { | |

| struct { | |

| uint32_t srcLo | |

| uint32_t srcHi | |

| } | |

| Addr src | |

| }; | |

| union { | |

| struct { | |

| uint32_t destLo | |

| uint32_t destHi | |

| } | |

| Addr dest | |

| }; | |

| uint64_t | res5 |

| uint64_t | res6 |

| union { | |

| struct { | |

| uint32_t compSignalLo | |

| uint32_t compSignalHi | |

| } | |

| Addr compSignal | |

| }; | |

| Addr | depSignal0 |

| Addr | depSignal1 |

| Addr | depSignal2 |

| Addr | depSignal3 |

| Addr | depSignal4 |

| uint64_t | res2 |

| union { | |

| struct { | |

| uint32_t compSignalLo | |

| uint32_t compSignalHi | |

| } | |

| Addr compSignal | |

| }; | |

| uint32_t | group_segment_fixed_size |

| uint32_t | private_segment_fixed_size |

| uint32_t | kernarg_size |

| uint8_t | reserved0 [4] |

| int64_t | kernel_code_entry_byte_offset |

| uint8_t | reserved1 [20] |

| uint32_t | accum_offset: 6 |

| uint32_t | compute_pgm_rsrc3_reserved1: 10 |

| uint32_t | tg_split: 1 |

| uint32_t | compute_pgm_rsrc3_reserved2: 15 |

| uint32_t | granulated_workitem_vgpr_count: 6 |

| uint32_t | granulated_wavefront_sgpr_count: 4 |

| uint32_t | priority: 2 |

| uint32_t | float_mode_round_32: 2 |

| uint32_t | float_mode_round_16_64: 2 |

| uint32_t | float_mode_denorm_32: 2 |

| uint32_t | float_mode_denorm_16_64: 2 |

| uint32_t | enable_dx10_clamp: 1 |

| uint32_t | debug_mode: 1 |

| uint32_t | enable_ieee_mode: 1 |

| uint32_t | bulky: 1 |

| uint32_t | cdbg_user: 1 |

| uint32_t | fp16_ovfl: 1 |

| uint32_t | compute_pgm_rsrc1_reserved: 2 |

| uint32_t | wgp_mode: 1 |

| uint32_t | mem_ordered: 1 |

| uint32_t | fwd_progress: 1 |

| uint32_t | enable_private_segment: 1 |

| uint32_t | user_sgpr_count: 5 |

| uint32_t | enable_trap_handler: 1 |

| uint32_t | enable_sgpr_workgroup_id_x: 1 |

| uint32_t | enable_sgpr_workgroup_id_y: 1 |

| uint32_t | enable_sgpr_workgroup_id_z: 1 |

| uint32_t | enable_sgpr_workgroup_info: 1 |

| uint32_t | enable_vgpr_workitem_id: 2 |

| uint32_t | enable_exception_address_watch: 1 |

| uint32_t | enable_exception_memory: 1 |

| uint32_t | granulated_lds_size: 9 |

| uint32_t | enable_exception_ieee_754_fp_invalid_operation: 1 |

| uint32_t | enable_exception_fp_denormal_source: 1 |

| uint32_t | enable_exception_ieee_754_fp_division_by_zero: 1 |

| uint32_t | enable_exception_ieee_754_fp_overflow: 1 |

| uint32_t | enable_exception_ieee_754_fp_underflow: 1 |

| uint32_t | enable_exception_ieee_754_fp_inexact: 1 |

| uint32_t | enable_exception_int_divide_by_zero: 1 |

| uint32_t | compute_pgm_rsrc2_reserved: 1 |

| uint32_t | enable_sgpr_private_segment_buffer: 1 |

| uint32_t | enable_sgpr_dispatch_ptr: 1 |

| uint32_t | enable_sgpr_queue_ptr: 1 |

| uint32_t | enable_sgpr_kernarg_segment_ptr: 1 |

| uint32_t | enable_sgpr_dispatch_id: 1 |

| uint32_t | enable_sgpr_flat_scratch_init: 1 |

| uint32_t | enable_sgpr_private_segment_size: 1 |

| uint32_t | kernel_code_properties_reserved1: 3 |

| uint32_t | enable_wavefront_size32: 1 |

| uint32_t | use_dynamic_stack: 1 |

| uint32_t | kernel_code_properties_reserved2: 4 |

| uint32_t | kernarg_preload_spec_length: 7 |

| uint32_t | kernarg_preload_spec_offset: 9 |

| uint8_t | reserved2 [4] |

Detailed Description

Definition at line 349 of file pm4_queues.hh.

Member Data Documentation

◆ [union]

| union { ... } gem5::PrimaryQueue |

◆ [union]

| union { ... } gem5::PrimaryQueue |

◆ doorbellOffset

| uint32_t gem5::PrimaryQueue::doorbellOffset |

Definition at line 369 of file pm4_queues.hh.

◆ doorbellRangeHi

| uint32_t gem5::PrimaryQueue::doorbellRangeHi |

Definition at line 371 of file pm4_queues.hh.

◆ doorbellRangeLo

| uint32_t gem5::PrimaryQueue::doorbellRangeLo |

Definition at line 370 of file pm4_queues.hh.

◆ queueRptrAddr

| Addr gem5::PrimaryQueue::queueRptrAddr |

Definition at line 358 of file pm4_queues.hh.

◆ queueRptrAddrHi

| uint32_t gem5::PrimaryQueue::queueRptrAddrHi |

Definition at line 356 of file pm4_queues.hh.

◆ queueRptrAddrLo

| uint32_t gem5::PrimaryQueue::queueRptrAddrLo |

Definition at line 355 of file pm4_queues.hh.

◆ queueWptr

| Addr gem5::PrimaryQueue::queueWptr |

Definition at line 367 of file pm4_queues.hh.

◆ queueWptrHi

| uint32_t gem5::PrimaryQueue::queueWptrHi |

Definition at line 365 of file pm4_queues.hh.

◆ queueWptrLo

| uint32_t gem5::PrimaryQueue::queueWptrLo |

Definition at line 364 of file pm4_queues.hh.

The documentation for this struct was generated from the following file:

- dev/amdgpu/pm4_queues.hh

Generated on Sat Oct 18 2025 08:06:53 for gem5 by doxygen 1.14.0