#include <op_encodings.hh>

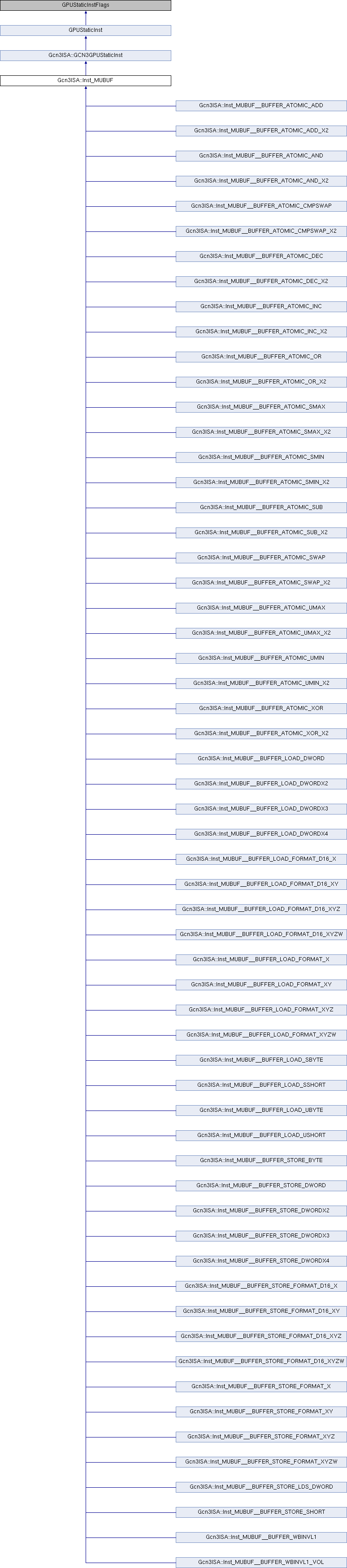

Public Member Functions | |

| Inst_MUBUF (InFmt_MUBUF *, const std::string &opcode) | |

| ~Inst_MUBUF () | |

| int | instSize () const override |

| void | generateDisassembly () override |

| bool | isScalarRegister (int opIdx) override |

| bool | isVectorRegister (int opIdx) override |

| int | getRegisterIndex (int opIdx, GPUDynInstPtr gpuDynInst) override |

Public Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst Public Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst | |

| GCN3GPUStaticInst (const std::string &opcode) | |

| ~GCN3GPUStaticInst () | |

| bool | isFlatScratchRegister (int opIdx) override |

| bool | isExecMaskRegister (int opIdx) override |

| bool | isSrcOperand (int opIdx) override |

| bool | isDstOperand (int opIdx) override |

| int | getOperandSize (int opIdx) override |

| int | coalescerTokenCount () const override |

| Return the number of tokens needed by the coalescer. More... | |

| ScalarRegU32 | srcLiteral () const override |

Public Member Functions inherited from GPUStaticInst Public Member Functions inherited from GPUStaticInst | |

| GPUStaticInst (const std::string &opcode) | |

| virtual | ~GPUStaticInst () |

| void | instAddr (int inst_addr) |

| int | instAddr () const |

| int | nextInstAddr () const |

| void | instNum (int num) |

| int | instNum () |

| void | ipdInstNum (int num) |

| int | ipdInstNum () const |

| virtual void | execute (GPUDynInstPtr gpuDynInst)=0 |

| const std::string & | disassemble () |

| virtual int | getNumOperands ()=0 |

| virtual int | numDstRegOperands ()=0 |

| virtual int | numSrcRegOperands ()=0 |

| int | numDstVecOperands () |

| int | numSrcVecOperands () |

| int | numDstVecDWORDs () |

| int | numSrcVecDWORDs () |

| int | numOpdDWORDs (int operandIdx) |

| bool | isALU () const |

| bool | isBranch () const |

| bool | isCondBranch () const |

| bool | isNop () const |

| bool | isReturn () const |

| bool | isEndOfKernel () const |

| bool | isKernelLaunch () const |

| bool | isSDWAInst () const |

| bool | isDPPInst () const |

| bool | isUnconditionalJump () const |

| bool | isSpecialOp () const |

| bool | isWaitcnt () const |

| bool | isBarrier () const |

| bool | isMemSync () const |

| bool | isMemRef () const |

| bool | isFlat () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isAtomicNoRet () const |

| bool | isAtomicRet () const |

| bool | isScalar () const |

| bool | readsSCC () const |

| bool | writesSCC () const |

| bool | readsVCC () const |

| bool | writesVCC () const |

| bool | readsEXEC () const |

| bool | writesEXEC () const |

| bool | readsMode () const |

| bool | writesMode () const |

| bool | ignoreExec () const |

| bool | isAtomicAnd () const |

| bool | isAtomicOr () const |

| bool | isAtomicXor () const |

| bool | isAtomicCAS () const |

| bool | isAtomicExch () const |

| bool | isAtomicAdd () const |

| bool | isAtomicSub () const |

| bool | isAtomicInc () const |

| bool | isAtomicDec () const |

| bool | isAtomicMax () const |

| bool | isAtomicMin () const |

| bool | isArgLoad () const |

| bool | isGlobalMem () const |

| bool | isLocalMem () const |

| bool | isArgSeg () const |

| bool | isGlobalSeg () const |

| bool | isGroupSeg () const |

| bool | isKernArgSeg () const |

| bool | isPrivateSeg () const |

| bool | isReadOnlySeg () const |

| bool | isSpillSeg () const |

| bool | isGloballyCoherent () const |

| Coherence domain of a memory instruction. More... | |

| bool | isSystemCoherent () const |

| bool | isF16 () const |

| bool | isF32 () const |

| bool | isF64 () const |

| bool | isFMA () const |

| bool | isMAC () const |

| bool | isMAD () const |

| virtual void | initiateAcc (GPUDynInstPtr gpuDynInst) |

| virtual void | completeAcc (GPUDynInstPtr gpuDynInst) |

| virtual uint32_t | getTargetPc () |

| void | setFlag (Flags flag) |

| const std::string & | opcode () const |

Protected Member Functions | |

| template<typename T > | |

| void | initMemRead (GPUDynInstPtr gpuDynInst) |

| template<int N> | |

| void | initMemRead (GPUDynInstPtr gpuDynInst) |

| template<typename T > | |

| void | initMemWrite (GPUDynInstPtr gpuDynInst) |

| template<int N> | |

| void | initMemWrite (GPUDynInstPtr gpuDynInst) |

| void | injectGlobalMemFence (GPUDynInstPtr gpuDynInst) |

| template<typename VOFF , typename VIDX , typename SRSRC , typename SOFF > | |

| void | calcAddr (GPUDynInstPtr gpuDynInst, VOFF v_off, VIDX v_idx, SRSRC s_rsrc_desc, SOFF s_offset, int inst_offset) |

| MUBUF insructions calculate their addresses as follows: More... | |

Protected Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst Protected Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst | |

| void | panicUnimplemented () const |

Protected Attributes | |

| InFmt_MUBUF | instData |

| InFmt_MUBUF_1 | extData |

| VectorMask | oobMask |

Protected Attributes inherited from Gcn3ISA::GCN3GPUStaticInst Protected Attributes inherited from Gcn3ISA::GCN3GPUStaticInst | |

| ScalarRegU32 | _srcLiteral |

| if the instruction has a src literal - an immediate value that is part of the instruction stream - we store that here More... | |

Protected Attributes inherited from GPUStaticInst Protected Attributes inherited from GPUStaticInst | |

| const std::string | _opcode |

| std::string | disassembly |

| int | _instNum |

| int | _instAddr |

| int | srcVecOperands |

| int | dstVecOperands |

| int | srcVecDWORDs |

| int | dstVecDWORDs |

| int | _ipdInstNum |

| Identifier of the immediate post-dominator instruction. More... | |

| std::bitset< Num_Flags > | _flags |

Additional Inherited Members | |

Public Attributes inherited from GPUStaticInst Public Attributes inherited from GPUStaticInst | |

| Enums::StorageClassType | executed_as |

Static Public Attributes inherited from GPUStaticInst Static Public Attributes inherited from GPUStaticInst | |

| static uint64_t | dynamic_id_count |

Detailed Description

Definition at line 512 of file op_encodings.hh.

Constructor & Destructor Documentation

◆ Inst_MUBUF()

| Gcn3ISA::Inst_MUBUF::Inst_MUBUF | ( | InFmt_MUBUF * | iFmt, |

| const std::string & | opcode | ||

| ) |

Definition at line 1911 of file op_encodings.cc.

References Gcn3ISA::GCN3GPUStaticInst::_srcLiteral, extData, Gcn3ISA::InFmt_MUBUF::GLC, instData, GPUStaticInst::setFlag(), and Gcn3ISA::InFmt_MUBUF::SLC.

◆ ~Inst_MUBUF()

| Gcn3ISA::Inst_MUBUF::~Inst_MUBUF | ( | ) |

Definition at line 1927 of file op_encodings.cc.

Member Function Documentation

◆ calcAddr()

|

inlineprotected |

MUBUF insructions calculate their addresses as follows:

index = (IDXEN ? vgpr_idx : 0) + (const_add_tid_en ? TID : 0) offset = (OFFEN ? vgpr_off : 0) + inst_off

/ ====================== LINEAR ADDRESSING ====================== / VADDR = base + sgpr_off + offset + stride * index

/ ===================== SWIZZLED ADDRESSING ===================== / index_msb = index / const_index_stride index_lsb = index % const_index_stride offset_msb = offset / const_element_size offset_lsb = offset % const_element_size buffer_offset = ((index_msb * stride + offset_msb * const_element_size) * const_index_stride + index_lsb * const_element_size + offset_lsb)

VADDR = base + sgpr_off + buffer_offset

first we calculate the buffer's index and offset. these will be used for either linear or swizzled buffers.

Range check behavior causes out of range accesses to to be treated differently. Out of range accesses return 0 for loads and are ignored for stores. For non-formatted accesses, this is done on a per-lane basis.

Definition at line 616 of file op_encodings.hh.

References DPRINTF, Gcn3ISA::NumVecElemPerVecReg(), oobMask, ArmISA::stride, and MipsISA::vaddr.

Referenced by Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_UBYTE::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_USHORT::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORD::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX2::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX3::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX4::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_BYTE::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_SHORT::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORD::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX2::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX3::execute(), and Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX4::execute().

◆ generateDisassembly()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 1938 of file op_encodings.cc.

References GPUStaticInst::_opcode, GPUStaticInst::disassembly, extData, instData, Gcn3ISA::InFmt_MUBUF::OFFSET, Gcn3ISA::InFmt_MUBUF_1::SOFFSET, Gcn3ISA::InFmt_MUBUF_1::SRSRC, Gcn3ISA::InFmt_MUBUF_1::VADDR, and Gcn3ISA::InFmt_MUBUF_1::VDATA.

◆ getRegisterIndex()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 1998 of file op_encodings.cc.

References extData, fatal, GPUStaticInst::getNumOperands(), Gcn3ISA::InFmt_MUBUF_1::SOFFSET, Gcn3ISA::InFmt_MUBUF_1::SRSRC, Gcn3ISA::InFmt_MUBUF_1::VADDR, and Gcn3ISA::InFmt_MUBUF_1::VDATA.

◆ initMemRead() [1/2]

|

inlineprotected |

Definition at line 528 of file op_encodings.hh.

References oobMask, and MemCmd::ReadReq.

◆ initMemRead() [2/2]

|

inlineprotected |

Definition at line 542 of file op_encodings.hh.

References oobMask, and MemCmd::ReadReq.

◆ initMemWrite() [1/2]

|

inlineprotected |

Definition at line 555 of file op_encodings.hh.

References oobMask, and MemCmd::WriteReq.

◆ initMemWrite() [2/2]

|

inlineprotected |

Definition at line 568 of file op_encodings.hh.

References oobMask, and MemCmd::WriteReq.

◆ injectGlobalMemFence()

|

inlineprotected |

Definition at line 580 of file op_encodings.hh.

Referenced by Gcn3ISA::Inst_MUBUF__BUFFER_WBINVL1::initiateAcc(), and Gcn3ISA::Inst_MUBUF__BUFFER_WBINVL1_VOL::initiateAcc().

◆ instSize()

|

overridevirtual |

Implements GPUStaticInst.

Definition at line 1932 of file op_encodings.cc.

◆ isScalarRegister()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 1956 of file op_encodings.cc.

References fatal, and GPUStaticInst::getNumOperands().

◆ isVectorRegister()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 1977 of file op_encodings.cc.

References fatal, and GPUStaticInst::getNumOperands().

Member Data Documentation

◆ extData

|

protected |

Definition at line 715 of file op_encodings.hh.

Referenced by Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_UBYTE::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_USHORT::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORD::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX2::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX3::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX4::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_UBYTE::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_USHORT::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORD::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX2::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX3::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX4::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_BYTE::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_SHORT::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORD::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX2::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX3::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX4::execute(), generateDisassembly(), getRegisterIndex(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_BYTE::initiateAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_SHORT::initiateAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORD::initiateAcc(), and Inst_MUBUF().

◆ instData

|

protected |

Definition at line 713 of file op_encodings.hh.

Referenced by Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_UBYTE::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_USHORT::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORD::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX2::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX3::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX4::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_BYTE::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_SHORT::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORD::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX2::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX3::execute(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORDX4::execute(), generateDisassembly(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_UBYTE::getOperandSize(), Gcn3ISA::Inst_MUBUF__BUFFER_STORE_BYTE::getOperandSize(), Inst_MUBUF(), and Gcn3ISA::Inst_MUBUF__BUFFER_STORE_DWORD::Inst_MUBUF__BUFFER_STORE_DWORD().

◆ oobMask

|

protected |

Definition at line 719 of file op_encodings.hh.

Referenced by calcAddr(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_UBYTE::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_USHORT::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORD::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX2::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX3::completeAcc(), Gcn3ISA::Inst_MUBUF__BUFFER_LOAD_DWORDX4::completeAcc(), initMemRead(), and initMemWrite().

The documentation for this class was generated from the following files:

- arch/gcn3/insts/op_encodings.hh

- arch/gcn3/insts/op_encodings.cc