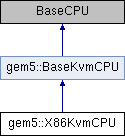

x86 implementation of a KVM-based hardware virtualized CPU. More...

#include <x86_cpu.hh>

Public Member Functions | |

| X86KvmCPU (const X86KvmCPUParams ¶ms) | |

| virtual | ~X86KvmCPU () |

| void | startup () override |

| void | dump () const override |

| Dump the internal state to the terminal. More... | |

| void | dumpFpuRegs () const |

| void | dumpIntRegs () const |

| void | dumpSpecRegs () const |

| void | dumpDebugRegs () const |

| void | dumpXCRs () const |

| void | dumpXSave () const |

| void | dumpVCpuEvents () const |

| void | dumpMSRs () const |

Public Member Functions inherited from gem5::BaseKvmCPU Public Member Functions inherited from gem5::BaseKvmCPU | |

| BaseKvmCPU (const BaseKvmCPUParams ¶ms) | |

| virtual | ~BaseKvmCPU () |

| void | init () override |

| void | startup () override |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| void | unserializeThread (CheckpointIn &cp, ThreadID tid) override |

| DrainState | drain () override |

| void | drainResume () override |

| void | notifyFork () override |

| void | switchOut () override |

| void | takeOverFrom (BaseCPU *cpu) override |

| void | verifyMemoryMode () const override |

| Port & | getDataPort () override |

| Port & | getInstPort () override |

| void | wakeup (ThreadID tid=0) override |

| void | activateContext (ThreadID thread_num) override |

| void | suspendContext (ThreadID thread_num) override |

| void | deallocateContext (ThreadID thread_num) |

| void | haltContext (ThreadID thread_num) override |

| long | getVCpuID () const |

| ThreadContext * | getContext (int tn) override |

| Counter | totalInsts () const override |

| Counter | totalOps () const override |

| void | finishMMIOPending () |

| Callback from KvmCPUPort to transition the CPU out of RunningMMIOPending when all timing requests have completed. More... | |

| void | kick () const |

| Force an exit from KVM. More... | |

Protected Types | |

| typedef std::vector< struct kvm_msr_entry > | KvmMSRVector |

Protected Types inherited from gem5::BaseKvmCPU Protected Types inherited from gem5::BaseKvmCPU | |

| enum | Status { Idle, Running, RunningService, RunningMMIOPending, RunningServiceCompletion } |

Protected Member Functions | |

| Tick | kvmRun (Tick ticks) override |

| Request KVM to run the guest for a given number of ticks. More... | |

| Tick | kvmRunDrain () override |

| Run the virtual CPU until draining completes. More... | |

| uint64_t | getHostCycles () const override |

| Get the value of the hardware cycle counter in the guest. More... | |

| void | stutterPC (PCStateBase &pc) const override |

| Modify a PCStatePtr's value so that its next PC is the current PC. More... | |

| const Kvm::MSRIndexVector & | getMsrIntersection () const |

| Get a list of MSRs supported by both gem5 and KVM. More... | |

| void | updateKvmState () override |

| Update the KVM state from the current thread context. More... | |

| void | updateThreadContext () override |

| Update the current thread context with the KVM state. More... | |

| void | deliverInterrupts () |

| Inject pending interrupts from gem5 into the virtual CPU. More... | |

| Tick | handleKvmExitIO () override |

| Handle x86 legacy IO (in/out) More... | |

| Tick | handleKvmExitIRQWindowOpen () override |

| The guest exited because an interrupt window was requested. More... | |

| bool | archIsDrained () const override |

| Check if there are pending events in the vCPU that prevents it from being drained. More... | |

| void | ioctlRun () override |

| Override for synchronizing state in kvm_run. More... | |

| void | setCPUID (const struct kvm_cpuid2 &cpuid) |

| Methods to access CPUID information using the extended API. More... | |

| void | setCPUID (const Kvm::CPUIDVector &cpuid) |

| void | setMSRs (const struct kvm_msrs &msrs) |

| Methods to access MSRs in the guest. More... | |

| void | setMSRs (const KvmMSRVector &msrs) |

| void | getMSRs (struct kvm_msrs &msrs) const |

| void | setMSR (uint32_t index, uint64_t value) |

| uint64_t | getMSR (uint32_t index) const |

| void | getDebugRegisters (struct kvm_debugregs ®s) const |

| Wrappers around KVM's state transfer methods. More... | |

| void | setDebugRegisters (const struct kvm_debugregs ®s) |

| void | getXCRs (struct kvm_xcrs ®s) const |

| void | setXCRs (const struct kvm_xcrs ®s) |

| void | getXSave (struct kvm_xsave &xsave) const |

| void | setXSave (const struct kvm_xsave &xsave) |

| void | getVCpuEvents (struct kvm_vcpu_events &events) const |

| void | setVCpuEvents (const struct kvm_vcpu_events &events) |

Protected Member Functions inherited from gem5::BaseKvmCPU Protected Member Functions inherited from gem5::BaseKvmCPU | |

| void | tick () |

| Execute the CPU until the next event in the main event queue or until the guest needs service from gem5. More... | |

| struct kvm_run * | getKvmRunState () |

| Get a pointer to the kvm_run structure containing all the input and output parameters from kvmRun(). More... | |

| uint8_t * | getGuestData (uint64_t offset) const |

| Retrieve a pointer to guest data stored at the end of the kvm_run structure. More... | |

| void | kvmNonMaskableInterrupt () |

| Send a non-maskable interrupt to the guest. More... | |

| void | kvmInterrupt (const struct kvm_interrupt &interrupt) |

| Send a normal interrupt to the guest. More... | |

| std::string | getAndFormatOneReg (uint64_t id) const |

| Get and format one register for printout. More... | |

| Tick | doMMIOAccess (Addr paddr, void *data, int size, bool write) |

| Inject a memory mapped IO request into gem5. More... | |

| int | ioctl (int request, long p1) const |

| vCPU ioctl interface. More... | |

| int | ioctl (int request, void *p1) const |

| int | ioctl (int request) const |

| void | getRegisters (struct kvm_regs ®s) const |

| Get/Set the register state of the guest vCPU. More... | |

| void | setRegisters (const struct kvm_regs ®s) |

| void | getSpecialRegisters (struct kvm_sregs ®s) const |

| void | setSpecialRegisters (const struct kvm_sregs ®s) |

| void | getFPUState (struct kvm_fpu &state) const |

| Get/Set the guest FPU/vector state. More... | |

| void | setFPUState (const struct kvm_fpu &state) |

| void | setOneReg (uint64_t id, const void *addr) |

| Get/Set single register using the KVM_(SET|GET)_ONE_REG API. More... | |

| void | setOneReg (uint64_t id, uint64_t value) |

| void | setOneReg (uint64_t id, uint32_t value) |

| void | getOneReg (uint64_t id, void *addr) const |

| uint64_t | getOneRegU64 (uint64_t id) const |

| uint32_t | getOneRegU32 (uint64_t id) const |

| void | syncThreadContext () |

| Update a thread context if the KVM state is dirty with respect to the cached thread context. More... | |

| EventQueue * | deviceEventQueue () |

| Get a pointer to the event queue owning devices. More... | |

| void | syncKvmState () |

| Update the KVM if the thread context is dirty. More... | |

| virtual Tick | handleKvmExit () |

| Main kvmRun exit handler, calls the relevant handleKvmExit* depending on exit type. More... | |

| virtual Tick | handleKvmExitHypercall () |

| The guest requested a monitor service using a hypercall. More... | |

| virtual Tick | handleKvmExitUnknown () |

| An unknown architecture dependent error occurred when starting the vCPU. More... | |

| virtual Tick | handleKvmExitException () |

| An unhandled virtualization exception occured. More... | |

| virtual Tick | handleKvmExitFailEntry () |

| KVM failed to start the virtualized CPU. More... | |

| void | setSignalMask (const sigset_t *mask) |

| Set the signal mask used in kvmRun() More... | |

Private Member Functions | |

| void | updateCPUID () |

| Transfer gem5's CPUID values into the virtual CPU. More... | |

| void | handleIOMiscReg32 (int miscreg) |

| Handle a 32-bit IO access that should be mapped to a MiscReg. More... | |

| void | updateKvmStateRegs () |

| Support routines to update the state of the KVM CPU from gem5's state representation. More... | |

| void | updateKvmStateSRegs () |

| Update control registers (CRx, segments, etc.) More... | |

| void | updateKvmStateFPU () |

| Update FPU and SIMD registers. More... | |

| void | updateKvmStateFPULegacy () |

| Update FPU and SIMD registers using the legacy API. More... | |

| void | updateKvmStateFPUXSave () |

| Update FPU and SIMD registers using the XSave API. More... | |

| void | updateKvmStateMSRs () |

| Update MSR registers. More... | |

| void | updateThreadContextRegs (const struct kvm_regs ®s, const struct kvm_sregs &sregs) |

| Support routines to update the state of gem5's thread context from KVM's state representation. More... | |

| void | updateThreadContextSRegs (const struct kvm_sregs &sregs) |

| Update control registers (CRx, segments, etc.) More... | |

| void | updateThreadContextFPU (const struct kvm_fpu &fpu) |

| Update FPU and SIMD registers using the legacy API. More... | |

| void | updateThreadContextXSave (const struct kvm_xsave &kxsave) |

| Update FPU and SIMD registers using the XSave API. More... | |

| void | updateThreadContextMSRs () |

| Update MSR registers. More... | |

Private Attributes | |

| Kvm::MSRIndexVector | cachedMsrIntersection |

| Cached intersection of supported MSRs. More... | |

| bool | haveDebugRegs |

| Kvm::capDebugRegs() available? More... | |

| bool | haveXSave |

| Kvm::capXSave() available? More... | |

| bool | useXSave |

| Should the XSave interface be used to sync the FPU and SIMD registers? More... | |

| bool | haveXCRs |

| Kvm::capXCRs() available? More... | |

Additional Inherited Members | |

Public Attributes inherited from gem5::BaseKvmCPU Public Attributes inherited from gem5::BaseKvmCPU | |

| SimpleThread * | thread |

| A cached copy of a thread's state in the form of a SimpleThread object. More... | |

| ThreadContext * | tc |

| ThreadContext object, provides an interface for external objects to modify this thread's state. More... | |

| KvmVM & | vm |

| gem5::BaseKvmCPU::StatGroup | stats |

| Counter | ctrInsts |

| Number of instructions executed by the CPU. More... | |

Protected Attributes inherited from gem5::BaseKvmCPU Protected Attributes inherited from gem5::BaseKvmCPU | |

| Status | _status |

| CPU run state. More... | |

| KVMCpuPort | dataPort |

| Port for data requests. More... | |

| KVMCpuPort | instPort |

| Unused dummy port for the instruction interface. More... | |

| const bool | alwaysSyncTC |

| Be conservative and always synchronize the thread context on KVM entry/exit. More... | |

| bool | threadContextDirty |

| Is the gem5 context dirty? Set to true to force an update of the KVM vCPU state upon the next call to kvmRun(). More... | |

| bool | kvmStateDirty |

| Is the KVM state dirty? Set to true to force an update of the KVM vCPU state upon the next call to kvmRun(). More... | |

| const long | vcpuID |

| KVM internal ID of the vCPU. More... | |

| pthread_t | vcpuThread |

| ID of the vCPU thread. More... | |

Detailed Description

x86 implementation of a KVM-based hardware virtualized CPU.

Definition at line 52 of file x86_cpu.hh.

Member Typedef Documentation

◆ KvmMSRVector

|

protected |

Definition at line 73 of file x86_cpu.hh.

Constructor & Destructor Documentation

◆ X86KvmCPU()

| gem5::X86KvmCPU::X86KvmCPU | ( | const X86KvmCPUParams & | params | ) |

Definition at line 536 of file x86_cpu.cc.

References gem5::Kvm::capDebugRegs(), gem5::Kvm::capExtendedCPUID(), gem5::Kvm::capSetTSSAddress(), gem5::Kvm::capUserNMI(), gem5::Kvm::capVCPUEvents(), gem5::Kvm::capXCRs(), gem5::Kvm::capXSave(), haveDebugRegs, haveXCRs, haveXSave, gem5::KvmVM::kvm, panic, useXSave, gem5::BaseKvmCPU::vm, and warn.

◆ ~X86KvmCPU()

|

virtual |

Definition at line 564 of file x86_cpu.cc.

Member Function Documentation

◆ archIsDrained()

|

overrideprotectedvirtual |

Check if there are pending events in the vCPU that prevents it from being drained.

There are cases after interrupt injection where the interrupt is still pending in the guest. This method detects such cases and requests additional draining.

- Returns

- False if there are pending events in the guest, True otherwise.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1373 of file x86_cpu.cc.

References DPRINTF, and getVCpuEvents().

Referenced by kvmRunDrain().

◆ deliverInterrupts()

|

protected |

Inject pending interrupts from gem5 into the virtual CPU.

Definition at line 1143 of file x86_cpu.cc.

References DPRINTF, gem5::X86ISA::X86FaultBase::getVector(), gem5::BaseKvmCPU::kvmInterrupt(), gem5::BaseKvmCPU::kvmNonMaskableInterrupt(), panic, gem5::SimpleThread::suspend(), gem5::BaseKvmCPU::syncThreadContext(), gem5::BaseKvmCPU::tc, gem5::BaseKvmCPU::thread, gem5::BaseKvmCPU::threadContextDirty, and updateKvmState().

Referenced by kvmRun().

◆ dump()

|

overridevirtual |

Dump the internal state to the terminal.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 583 of file x86_cpu.cc.

References dumpDebugRegs(), dumpFpuRegs(), dumpIntRegs(), dumpMSRs(), dumpSpecRegs(), dumpVCpuEvents(), dumpXCRs(), dumpXSave(), and useXSave.

Referenced by updateKvmState(), and updateThreadContext().

◆ dumpDebugRegs()

| void gem5::X86KvmCPU::dumpDebugRegs | ( | ) | const |

Definition at line 622 of file x86_cpu.cc.

References gem5::dumpKvm(), getDebugRegisters(), haveDebugRegs, and inform.

Referenced by dump().

◆ dumpFpuRegs()

| void gem5::X86KvmCPU::dumpFpuRegs | ( | ) | const |

Definition at line 598 of file x86_cpu.cc.

References gem5::dumpKvm(), and gem5::BaseKvmCPU::getFPUState().

Referenced by dump().

◆ dumpIntRegs()

| void gem5::X86KvmCPU::dumpIntRegs | ( | ) | const |

Definition at line 606 of file x86_cpu.cc.

References gem5::dumpKvm(), and gem5::BaseKvmCPU::getRegisters().

Referenced by dump().

◆ dumpMSRs()

| void gem5::X86KvmCPU::dumpMSRs | ( | ) | const |

Definition at line 668 of file x86_cpu.cc.

References gem5::dumpKvm(), gem5::ArmISA::e, getMSRs(), gem5::ArmISA::i, gem5::KvmVM::kvm, and gem5::BaseKvmCPU::vm.

Referenced by dump().

◆ dumpSpecRegs()

| void gem5::X86KvmCPU::dumpSpecRegs | ( | ) | const |

Definition at line 614 of file x86_cpu.cc.

References gem5::dumpKvm(), and gem5::BaseKvmCPU::getSpecialRegisters().

Referenced by dump().

◆ dumpVCpuEvents()

| void gem5::X86KvmCPU::dumpVCpuEvents | ( | ) | const |

Definition at line 660 of file x86_cpu.cc.

References gem5::dumpKvm(), and getVCpuEvents().

Referenced by dump().

◆ dumpXCRs()

| void gem5::X86KvmCPU::dumpXCRs | ( | ) | const |

Definition at line 636 of file x86_cpu.cc.

References gem5::dumpKvm(), getXCRs(), haveXCRs, and inform.

Referenced by dump().

◆ dumpXSave()

| void gem5::X86KvmCPU::dumpXSave | ( | ) | const |

Definition at line 648 of file x86_cpu.cc.

References gem5::dumpKvm(), getXSave(), haveXSave, and inform.

Referenced by dump().

◆ getDebugRegisters()

|

protected |

Wrappers around KVM's state transfer methods.

Definition at line 1570 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpDebugRegs().

◆ getHostCycles()

|

overrideprotectedvirtual |

Get the value of the hardware cycle counter in the guest.

This method is supposed to return the total number of cycles executed in hardware mode relative to some arbitrary point in the past. It's mainly used when estimating the number of cycles actually executed by the CPU in kvmRun(). The default behavior of this method is to use the cycles performance counter, but some architectures may want to use internal registers instead.

- Returns

- Number of host cycles executed relative to an undefined point in the past.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1269 of file x86_cpu.cc.

◆ getMSR()

|

protected |

Definition at line 1534 of file x86_cpu.cc.

References getMSRs(), and gem5::MipsISA::index.

Referenced by getHostCycles().

◆ getMsrIntersection()

|

protected |

Get a list of MSRs supported by both gem5 and KVM.

- Note

- This method uses an internal cache and only generates the MSR list once.

- Returns

- reference to a list of msr indices

Definition at line 1549 of file x86_cpu.cc.

References cachedMsrIntersection, DPRINTF, gem5::KvmVM::kvm, gem5::X86ISA::msrMap, gem5::BaseKvmCPU::vm, and warn.

Referenced by updateKvmStateMSRs(), and updateThreadContextMSRs().

◆ getMSRs()

|

protected |

Definition at line 1511 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpMSRs(), getMSR(), and updateThreadContextMSRs().

◆ getVCpuEvents()

|

protected |

Definition at line 1621 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by archIsDrained(), and dumpVCpuEvents().

◆ getXCRs()

|

protected |

Definition at line 1592 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpXCRs().

◆ getXSave()

|

protected |

Definition at line 1606 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpXSave(), and updateThreadContext().

◆ handleIOMiscReg32()

|

private |

Handle a 32-bit IO access that should be mapped to a MiscReg.

- Note

- This method can only be called on when handling IO after a KVM_EXIT_IO.

- Parameters

-

miscreg Register to map the current IO access to.

Definition at line 1275 of file x86_cpu.cc.

References data, gem5::BaseKvmCPU::getGuestData(), gem5::BaseKvmCPU::getKvmRunState(), panic, gem5::ThreadContext::readMiscRegNoEffect(), gem5::ThreadContext::setMiscReg(), and gem5::BaseKvmCPU::tc.

Referenced by handleKvmExitIO().

◆ handleKvmExitIO()

|

overrideprotectedvirtual |

Handle x86 legacy IO (in/out)

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1300 of file x86_cpu.cc.

References gem5::ThreadContext::contextId(), gem5::X86ISA::count, gem5::BaseKvmCPU::dataPort, gem5::Packet::dataStatic(), gem5::BaseKvmCPU::deviceEventQueue(), DPRINTF, gem5::BaseKvmCPU::getGuestData(), gem5::BaseKvmCPU::getKvmRunState(), handleIOMiscReg32(), gem5::ArmISA::i, IO_PCI_CONF_ADDR, IO_PCI_CONF_DATA_BASE, gem5::X86ISA::MISCREG_PCI_CONFIG_ADDRESS, gem5::ThreadContext::readMiscRegNoEffect(), gem5::MemCmd::ReadReq, gem5::BaseKvmCPU::KVMCpuPort::submitIO(), gem5::BaseKvmCPU::tc, gem5::Request::UNCACHEABLE, gem5::MemCmd::WriteReq, gem5::X86ISA::x86IOAddress(), and gem5::X86ISA::x86PciConfigAddress().

◆ handleKvmExitIRQWindowOpen()

|

overrideprotectedvirtual |

The guest exited because an interrupt window was requested.

The guest exited because an interrupt window was requested (request_interrupt_window in the kvm_run structure was set to 1 before calling kvmRun) and it is now ready to receive

- Returns

- Number of ticks spent servicing the IRQ

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1364 of file x86_cpu.cc.

◆ ioctlRun()

|

overrideprotectedvirtual |

Override for synchronizing state in kvm_run.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1402 of file x86_cpu.cc.

References gem5::BaseKvmCPU::getKvmRunState(), gem5::BaseKvmCPU::ioctlRun(), gem5::X86ISA::MISCREG_APIC_BASE, gem5::X86ISA::MISCREG_CR8, gem5::ThreadContext::readMiscReg(), gem5::ThreadContext::setMiscReg(), and gem5::BaseKvmCPU::tc.

◆ kvmRun()

Request KVM to run the guest for a given number of ticks.

The method returns the approximate number of ticks executed.

- Note

- The returned number of ticks can be both larger or smaller than the requested number of ticks. A smaller number can, for example, occur when the guest executes MMIO. A larger number is typically due to performance counter inaccuracies.

- This method is virtual in order to allow implementations to check for architecture specific events (e.g., interrupts) before entering the VM.

- It is the response of the caller (normally tick()) to make sure that the KVM state is synchronized and that the TC is invalidated after entering KVM.

- This method does not normally cause any state transitions. However, if it may suspend the CPU by suspending the thread, which leads to a transition to the Idle state. In such a case, kvm must not be entered.

- Parameters

-

ticks Number of ticks to execute, set to 0 to exit immediately after finishing pending operations.

- Returns

- Number of ticks executed (see note)

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1196 of file x86_cpu.cc.

References gem5::BaseKvmCPU::_status, deliverInterrupts(), DPRINTF, gem5::BaseKvmCPU::getKvmRunState(), gem5::BaseKvmCPU::Idle, gem5::BaseKvmCPU::kvmRun(), and gem5::BaseKvmCPU::syncThreadContext().

◆ kvmRunDrain()

|

overrideprotectedvirtual |

Run the virtual CPU until draining completes.

In addition to the base functionality provided by BaseKvmCPU::kvmRunDrain(), this method handles x86-specific cases where there are pending interrupt events in the virtual CPU. These are handled by requesting an interrupt window if interrupts are pending (causing the vCPU to execute until interrupts can be delivered again).

- Returns

- Number of ticks executed

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1244 of file x86_cpu.cc.

References archIsDrained(), DPRINTF, gem5::BaseKvmCPU::getKvmRunState(), gem5::BaseKvmCPU::kvmRun(), and gem5::sim_clock::as_float::ms.

◆ setCPUID() [1/2]

|

protected |

Definition at line 1479 of file x86_cpu.cc.

References gem5::MipsISA::cpuid, and setCPUID().

◆ setCPUID() [2/2]

|

protected |

Methods to access CPUID information using the extended API.

Only available if Kvm::capExtendedCPUID() is true.

Definition at line 1471 of file x86_cpu.cc.

References gem5::MipsISA::cpuid, gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by setCPUID(), and updateCPUID().

◆ setDebugRegisters()

|

protected |

Definition at line 1581 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

◆ setMSR()

|

protected |

Definition at line 1520 of file x86_cpu.cc.

References gem5::MipsISA::index, and setMSRs().

◆ setMSRs() [1/2]

|

protected |

Definition at line 1499 of file x86_cpu.cc.

References setMSRs().

◆ setMSRs() [2/2]

|

protected |

Methods to access MSRs in the guest.

Definition at line 1491 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by setMSR(), setMSRs(), and updateKvmStateMSRs().

◆ setVCpuEvents()

|

protected |

Definition at line 1628 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

◆ setXCRs()

|

protected |

Definition at line 1599 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

◆ setXSave()

|

protected |

Definition at line 1613 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by updateKvmStateFPUXSave().

◆ startup()

|

override |

Definition at line 569 of file x86_cpu.cc.

References gem5::BaseKvmCPU::startup(), and updateCPUID().

◆ stutterPC()

|

inlineoverrideprotectedvirtual |

Modify a PCStatePtr's value so that its next PC is the current PC.

This needs to be implemented in KVM base classes since modifying the next PC value is an ISA specific operation. This is only used in doMMIOAccess, for reasons explained in a comment there.

Implements gem5::BaseKvmCPU.

Definition at line 96 of file x86_cpu.hh.

References gem5::MipsISA::pc.

◆ updateCPUID()

|

private |

Transfer gem5's CPUID values into the virtual CPU.

Definition at line 1435 of file x86_cpu.cc.

References gem5::MipsISA::cpuid, gem5::X86ISA::doCpuid(), gem5::makeKvmCpuid(), gem5::X86ISA::CpuidResult::rax, setCPUID(), and gem5::BaseKvmCPU::tc.

Referenced by startup().

◆ updateKvmState()

|

overrideprotectedvirtual |

Update the KVM state from the current thread context.

The base CPU calls this method before starting the guest CPU when the contextDirty flag is set. The architecture dependent CPU implementation is expected to update all guest state (registers, special registers, and FPU state).

Implements gem5::BaseKvmCPU.

Definition at line 687 of file x86_cpu.cc.

References DPRINTF, dump(), updateKvmStateFPU(), updateKvmStateMSRs(), updateKvmStateRegs(), and updateKvmStateSRegs().

Referenced by deliverInterrupts().

◆ updateKvmStateFPU()

|

private |

Update FPU and SIMD registers.

This method uses the appropriate (depending on availability and user configuration) kernel API by calling updateKvmStateFPULegacy() or updateKvmStateFPUXSave().

Definition at line 919 of file x86_cpu.cc.

References updateKvmStateFPULegacy(), updateKvmStateFPUXSave(), and useXSave.

Referenced by updateKvmState().

◆ updateKvmStateFPULegacy()

|

private |

Update FPU and SIMD registers using the legacy API.

- Note

- This method should normally only be called by updateKvmStateFPU() which automatically chooses between available APIs.

Definition at line 870 of file x86_cpu.cc.

References gem5::X86ISA::MISCREG_FIOFF, gem5::X86ISA::MISCREG_FISEG, gem5::X86ISA::MISCREG_FOOFF, gem5::X86ISA::MISCREG_FOSEG, gem5::ThreadContext::readMiscRegNoEffect(), gem5::BaseKvmCPU::setFPUState(), gem5::BaseKvmCPU::tc, gem5::updateKvmStateFPUCommon(), and warn_once.

Referenced by updateKvmStateFPU().

◆ updateKvmStateFPUXSave()

|

private |

Update FPU and SIMD registers using the XSave API.

- Note

- This method should normally only be called by updateKvmStateFPU() which automatically chooses between available APIs.

Definition at line 894 of file x86_cpu.cc.

References gem5::X86ISA::MISCREG_FIOFF, gem5::X86ISA::MISCREG_FISEG, gem5::X86ISA::MISCREG_FOOFF, gem5::X86ISA::MISCREG_FOSEG, gem5::ThreadContext::readMiscRegNoEffect(), setXSave(), gem5::BaseKvmCPU::tc, gem5::updateKvmStateFPUCommon(), and warn_once.

Referenced by updateKvmStateFPU().

◆ updateKvmStateMSRs()

|

private |

Update MSR registers.

Definition at line 928 of file x86_cpu.cc.

References DPRINTF, gem5::ArmISA::e, getMsrIntersection(), gem5::X86ISA::msrMap, gem5::ThreadContext::readMiscReg(), setMSRs(), and gem5::BaseKvmCPU::tc.

Referenced by updateKvmState().

◆ updateKvmStateRegs()

|

private |

Support routines to update the state of the KVM CPU from gem5's state representation.

Update integer registers

Definition at line 700 of file x86_cpu.cc.

References FOREACH_IREG, gem5::X86ISA::getRFlags(), gem5::PCStateBase::instAddr(), gem5::X86ISA::MISCREG_CS_BASE, gem5::ThreadContext::pcState(), gem5::ThreadContext::readMiscReg(), gem5::BaseKvmCPU::setRegisters(), and gem5::BaseKvmCPU::tc.

Referenced by updateKvmState().

◆ updateKvmStateSRegs()

|

private |

Update control registers (CRx, segments, etc.)

Definition at line 767 of file x86_cpu.cc.

References gem5::forceSegAccessed(), FOREACH_DTABLE, FOREACH_SEGMENT, FOREACH_SREG, hack, gem5::X86ISA::MISCREG_RFLAGS, gem5::ThreadContext::readMiscReg(), SEG_CS_TYPE_ACCESSED, SEG_CS_TYPE_READ_ACCESSED, SEG_SYS_TYPE_TSS_AVAILABLE, SEG_SYS_TYPE_TSS_BUSY, gem5::BaseKvmCPU::setSpecialRegisters(), and gem5::BaseKvmCPU::tc.

Referenced by updateKvmState().

◆ updateThreadContext()

|

overrideprotectedvirtual |

Update the current thread context with the KVM state.

The base CPU after the guest updates any of the KVM state. In practice, this happens after kvmRun is called. The architecture dependent code is expected to read the state of the guest CPU and update gem5's thread state.

Implements gem5::BaseKvmCPU.

Definition at line 950 of file x86_cpu.cc.

References DPRINTF, dump(), gem5::BaseKvmCPU::getFPUState(), gem5::BaseKvmCPU::getRegisters(), gem5::BaseKvmCPU::getSpecialRegisters(), getXSave(), gem5::X86ISA::MISCREG_M5_REG, gem5::ThreadContext::setMiscReg(), gem5::BaseKvmCPU::tc, updateThreadContextFPU(), updateThreadContextMSRs(), updateThreadContextRegs(), updateThreadContextSRegs(), updateThreadContextXSave(), and useXSave.

◆ updateThreadContextFPU()

|

private |

Update FPU and SIMD registers using the legacy API.

Definition at line 1089 of file x86_cpu.cc.

References gem5::X86ISA::MISCREG_FIOFF, gem5::X86ISA::MISCREG_FISEG, gem5::X86ISA::MISCREG_FOOFF, gem5::X86ISA::MISCREG_FOSEG, gem5::ThreadContext::setMiscRegNoEffect(), gem5::BaseKvmCPU::tc, and gem5::updateThreadContextFPUCommon().

Referenced by updateThreadContext().

◆ updateThreadContextMSRs()

|

private |

Update MSR registers.

Definition at line 1113 of file x86_cpu.cc.

References gem5::ArmISA::at, DPRINTF, getMsrIntersection(), getMSRs(), gem5::ArmISA::i, gem5::X86ISA::msrMap, gem5::ThreadContext::setMiscReg(), and gem5::BaseKvmCPU::tc.

Referenced by updateThreadContext().

◆ updateThreadContextRegs()

|

private |

Support routines to update the state of gem5's thread context from KVM's state representation.

Update integer registers

Definition at line 984 of file x86_cpu.cc.

References FOREACH_IREG, gem5::ThreadContext::pcState(), gem5::X86ISA::setRFlags(), and gem5::BaseKvmCPU::tc.

Referenced by updateThreadContext().

◆ updateThreadContextSRegs()

|

private |

Update control registers (CRx, segments, etc.)

Definition at line 1038 of file x86_cpu.cc.

References FOREACH_DTABLE, FOREACH_SEGMENT, FOREACH_SREG, and gem5::BaseKvmCPU::getKvmRunState().

Referenced by updateThreadContext().

◆ updateThreadContextXSave()

|

private |

Update FPU and SIMD registers using the XSave API.

Definition at line 1100 of file x86_cpu.cc.

References gem5::FXSave::ctrl64, gem5::X86ISA::MISCREG_FIOFF, gem5::X86ISA::MISCREG_FISEG, gem5::X86ISA::MISCREG_FOOFF, gem5::X86ISA::MISCREG_FOSEG, gem5::ThreadContext::setMiscRegNoEffect(), gem5::BaseKvmCPU::tc, and gem5::updateThreadContextFPUCommon().

Referenced by updateThreadContext().

Member Data Documentation

◆ cachedMsrIntersection

|

mutableprivate |

Cached intersection of supported MSRs.

Definition at line 254 of file x86_cpu.hh.

Referenced by getMsrIntersection().

◆ haveDebugRegs

|

private |

Kvm::capDebugRegs() available?

Definition at line 258 of file x86_cpu.hh.

Referenced by dumpDebugRegs(), and X86KvmCPU().

◆ haveXCRs

|

private |

Kvm::capXCRs() available?

Definition at line 267 of file x86_cpu.hh.

Referenced by dumpXCRs(), and X86KvmCPU().

◆ haveXSave

|

private |

Kvm::capXSave() available?

Definition at line 260 of file x86_cpu.hh.

Referenced by dumpXSave(), and X86KvmCPU().

◆ useXSave

|

private |

Should the XSave interface be used to sync the FPU and SIMD registers?

Definition at line 265 of file x86_cpu.hh.

Referenced by dump(), updateKvmStateFPU(), updateThreadContext(), and X86KvmCPU().

The documentation for this class was generated from the following files:

- arch/x86/kvm/x86_cpu.hh

- arch/x86/kvm/x86_cpu.cc