#include <isa.hh>

Public Member Functions | |

| const RegId & | mapIntRegId (RegIndex idx) const |

| void | clear () override |

| SelfDebug * | getSelfDebug () const |

| const ArmRelease * | getRelease () const |

| RegVal | readMiscRegNoEffect (RegIndex idx) const override |

| RegVal | readMiscReg (RegIndex idx) override |

| void | setMiscRegNoEffect (RegIndex idx, RegVal val) override |

| void | setMiscReg (RegIndex, RegVal val) override |

| RegVal | readMiscRegReset (RegIndex) const |

| void | setMiscRegReset (RegIndex, RegVal val) |

| int | flattenMiscIndex (int reg) const |

| int | redirectRegVHE (int misc_reg) |

| Returns the enconcing equivalent when VHE is implemented and HCR_EL2.E2H is enabled and executing at EL2. | |

| int | snsBankedIndex64 (MiscRegIndex reg, bool ns) const |

| std::pair< int, int > | getMiscIndices (int misc_reg) const |

| bool | inSecureState () const |

| Return true if the PE is in Secure state. | |

| ExceptionLevel | currEL () const |

| Returns the current Exception Level (EL) of the ISA object. | |

| unsigned | getCurSveVecLenInBits () const |

| unsigned | getCurSveVecLenInBitsAtReset () const |

| unsigned | getCurSmeVecLenInBits () const |

| unsigned | getCurSmeVecLenInBitsAtReset () const |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| void | startup () override |

| startup() is the final initialization call before simulation. | |

| void | setupThreadContext () |

| PCStateBase * | newPCState (Addr new_inst_addr=0) const override |

| void | takeOverFrom (ThreadContext *new_tc, ThreadContext *old_tc) override |

| enums::DecoderFlavor | decoderFlavor () const |

| PARAMS (ArmISA) | |

| ISA (const Params &p) | |

| uint64_t | getExecutingAsid () const override |

| bool | inUserMode () const override |

| void | copyRegsFrom (ThreadContext *src) override |

| void | handleLockedRead (const RequestPtr &req) override |

| void | handleLockedRead (ExecContext *xc, const RequestPtr &req) override |

| bool | handleLockedWrite (const RequestPtr &req, Addr cacheBlockMask) override |

| bool | handleLockedWrite (ExecContext *xc, const RequestPtr &req, Addr cacheBlockMask) override |

| void | handleLockedSnoop (PacketPtr pkt, Addr cacheBlockMask) override |

| void | handleLockedSnoop (ExecContext *xc, PacketPtr pkt, Addr cacheBlockMask) override |

| void | handleLockedSnoopHit () override |

| void | handleLockedSnoopHit (ExecContext *xc) override |

| void | globalClearExclusive () override |

| void | globalClearExclusive (ExecContext *xc) override |

| int64_t | getVectorLengthInBytes () const override |

| This function returns the vector length of the Vector Length Agnostic extension of the ISA. | |

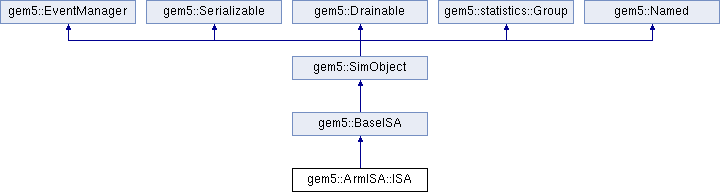

| Public Member Functions inherited from gem5::BaseISA | |

| virtual void | setThreadContext (ThreadContext *_tc) |

| virtual void | resetThread () |

| const RegClasses & | regClasses () const |

| const std::string & | getIsaName () const |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Static Public Member Functions | |

| static SelfDebug * | getSelfDebug (ThreadContext *tc) |

| template<typename Elem> | |

| static void | zeroSveVecRegUpperPart (Elem *v, unsigned eCount) |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

Protected Member Functions | |

| const MiscRegLUTEntryInitializer | InitReg (uint32_t reg) |

| void | initializeMiscRegMetadata () |

| BaseISADevice & | getGenericTimer () |

| BaseISADevice & | getGICv3CPUInterface () |

| BaseISADevice * | getGICv3CPUInterface (ThreadContext *tc) |

| void | updateRegMap (CPSR cpsr) |

| void | addressTranslation (MMU::ArmTranslationType tran_type, BaseMMU::Mode mode, Request::Flags flags, RegVal val) |

| Protected Member Functions inherited from gem5::BaseISA | |

| BaseISA (const SimObjectParams &p, const std::string &name) | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

Protected Attributes | |

| ArmSystem * | system |

| const enums::DecoderFlavor | _decoderFlavor |

| DummyISADevice | dummyDevice |

| Dummy device for to handle non-existing ISA devices. | |

| BaseISADevice * | pmu |

| std::unique_ptr< BaseISADevice > | timer |

| std::unique_ptr< BaseISADevice > | gicv3CpuInterface |

| bool | highestELIs64 |

| ExceptionLevel | highestEL |

| bool | haveLargeAsid64 |

| uint8_t | physAddrRange |

| unsigned | sveVL |

| SVE vector length in quadwords. | |

| unsigned | smeVL |

| SME vector length in quadwords. | |

| const ArmRelease * | release |

| This could be either a FS or a SE release. | |

| bool | impdefAsNop |

| If true, accesses to IMPLEMENTATION DEFINED registers are treated as NOP hence not causing UNDEFINED INSTRUCTION. | |

| SelfDebug * | selfDebug |

| Random::RandomPtr | rng = Random::genRandom() |

| RegVal | miscRegs [NUM_MISCREGS] |

| const RegId * | intRegMap |

| Protected Attributes inherited from gem5::BaseISA | |

| ThreadContext * | tc = nullptr |

| RegClasses | _regClasses |

| std::string | isaName |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Public Types inherited from gem5::BaseISA | |

| typedef std::vector< const RegClass * > | RegClasses |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Detailed Description

Constructor & Destructor Documentation

◆ ISA()

| gem5::ArmISA::ISA::ISA | ( | const Params & | p | ) |

Definition at line 86 of file isa.cc.

References _decoderFlavor, gem5::BaseISA::_regClasses, gem5::BaseISA::BaseISA(), gem5::ArmISA::ccRegClass, clear(), decoderFlavor(), dummyDevice, gem5::ArmISA::EL1, gem5::ArmISA::flatIntRegClass, gem5::X86ISA::floatRegClass, gem5::FullSystem, haveLargeAsid64, highestEL, highestELIs64, impdefAsNop, initializeMiscRegMetadata(), gem5::ArmISA::matRegClass, gem5::ArmISA::miscRegClass, gem5::MipsISA::p, physAddrRange, pmu, gem5::ArmISA::preUnflattenMiscReg(), release, selfDebug, smeVL, sveVL, system, gem5::ArmISA::vecElemClass, gem5::ArmISA::vecPredRegClass, and gem5::ArmISA::vecRegClass.

Member Function Documentation

◆ addressTranslation()

|

protected |

Definition at line 1573 of file isa.cc.

References DPRINTF, gem5::Request::funcRequestorId, gem5::ArmISA::ArmFault::getFsr(), gem5::ArmISA::getMMUPtr(), gem5::ArmISA::MMU::HypMode, gem5::ArmISA::ArmFault::iss(), gem5::ArmISA::ArmFault::isStage2(), gem5::ArmISA::mask, gem5::ArmISA::MISCREG_HCR_EL2, gem5::ArmISA::MISCREG_PAR, gem5::ArmISA::MISCREG_TTBCR, gem5::ArmISA::mode, gem5::NoFault, readMiscRegNoEffect(), release, gem5::ArmISA::MMU::S1S2NsTran, setMiscRegNoEffect(), gem5::BaseISA::tc, gem5::ArmISA::MMU::translateFunctional(), gem5::ArmISA::ArmFault::update(), gem5::X86ISA::val, and warn_once.

Referenced by setMiscReg().

◆ clear()

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 138 of file isa.cc.

References gem5::ArmISA::getMMUPtr(), gem5::ArmISA::MMU::invalidateMiscReg(), gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::MISCREG_CPSR, miscRegs, gem5::ArmISA::NUM_MISCREGS, gem5::BaseISA::tc, and updateRegMap().

Referenced by ISA().

◆ copyRegsFrom()

|

overridevirtual |

Implements gem5::BaseISA.

Definition at line 191 of file isa.cc.

References gem5::ArmISA::ccRegClass, gem5::ArmISA::flatIntRegClass, gem5::ThreadContext::getReg(), gem5::ArmISA::i, gem5::ArmISA::MMU::invalidateMiscReg(), gem5::ArmISA::matRegClass, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::NUM_MISCREGS, gem5::ThreadContext::pcState(), gem5::ThreadContext::readMiscRegNoEffect(), gem5::BaseISA::tc, gem5::ArmISA::vecElemClass, and gem5::ArmISA::vecRegClass.

◆ currEL()

| ExceptionLevel gem5::ArmISA::ISA::currEL | ( | ) | const |

Returns the current Exception Level (EL) of the ISA object.

Definition at line 1434 of file isa.cc.

References gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::opModeToEL(), and readMiscRegNoEffect().

Referenced by readMiscReg(), and redirectRegVHE().

◆ decoderFlavor()

|

inline |

◆ flattenMiscIndex()

|

inline |

Definition at line 205 of file isa.hh.

References flattenMiscIndex(), highestELIs64, inSecureState(), gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::MISCREG_BANKED, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_MAIR0, gem5::ArmISA::MISCREG_MAIR1, gem5::ArmISA::MISCREG_MUTEX, gem5::ArmISA::MISCREG_NMRR, gem5::ArmISA::MISCREG_NMRR_MAIR1, gem5::ArmISA::MISCREG_NMRR_MAIR1_NS, gem5::ArmISA::MISCREG_NMRR_MAIR1_S, gem5::ArmISA::MISCREG_PMCCFILTR, gem5::ArmISA::MISCREG_PMSELR, gem5::ArmISA::MISCREG_PMXEVTYPER, gem5::ArmISA::MISCREG_PMXEVTYPER_PMCCFILTR, gem5::ArmISA::MISCREG_PRRR, gem5::ArmISA::MISCREG_PRRR_MAIR0, gem5::ArmISA::MISCREG_PRRR_MAIR0_NS, gem5::ArmISA::MISCREG_PRRR_MAIR0_S, gem5::ArmISA::MISCREG_SPSR, gem5::ArmISA::MISCREG_SPSR_ABT, gem5::ArmISA::MISCREG_SPSR_EL1, gem5::ArmISA::MISCREG_SPSR_EL2, gem5::ArmISA::MISCREG_SPSR_EL3, gem5::ArmISA::MISCREG_SPSR_FIQ, gem5::ArmISA::MISCREG_SPSR_HYP, gem5::ArmISA::MISCREG_SPSR_IRQ, gem5::ArmISA::MISCREG_SPSR_MON, gem5::ArmISA::MISCREG_SPSR_SVC, gem5::ArmISA::MISCREG_SPSR_UND, gem5::ArmISA::MISCREG_TTBCR, miscRegs, gem5::ArmISA::MODE_ABORT, gem5::ArmISA::MODE_EL0T, gem5::ArmISA::MODE_EL1H, gem5::ArmISA::MODE_EL1T, gem5::ArmISA::MODE_EL2H, gem5::ArmISA::MODE_EL2T, gem5::ArmISA::MODE_EL3H, gem5::ArmISA::MODE_EL3T, gem5::ArmISA::MODE_FIQ, gem5::ArmISA::MODE_HYP, gem5::ArmISA::MODE_IRQ, gem5::ArmISA::MODE_MON, gem5::ArmISA::MODE_SVC, gem5::ArmISA::MODE_UNDEFINED, gem5::ArmISA::MODE_USER, panic, readMiscRegNoEffect(), gem5::X86ISA::reg, snsBankedIndex64(), and warn.

Referenced by flattenMiscIndex(), getMiscIndices(), readMiscRegReset(), and setMiscRegReset().

◆ getCurSmeVecLenInBits()

| unsigned gem5::ArmISA::ISA::getCurSmeVecLenInBits | ( | ) | const |

Definition at line 1493 of file isa.cc.

References gem5::ArmISA::el, gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL3, gem5::ArmISA::ELIsInHost(), gem5::FullSystem, gem5::ArmISA::isSecure(), gem5::ArmISA::len, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_SMCR_EL1, gem5::ArmISA::MISCREG_SMCR_EL2, gem5::ArmISA::MISCREG_SMCR_EL3, miscRegs, panic_if, release, smeVL, and gem5::BaseISA::tc.

Referenced by gem5::ArmISA::ArmStaticInst::getCurSmeVecLenInBits(), getCurSveVecLenInBits(), and setMiscReg().

◆ getCurSmeVecLenInBitsAtReset()

|

inline |

◆ getCurSveVecLenInBits()

| unsigned gem5::ArmISA::ISA::getCurSveVecLenInBits | ( | ) | const |

Definition at line 1442 of file isa.cc.

References gem5::ArmISA::el, gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL3, gem5::ArmISA::ELIsInHost(), gem5::FullSystem, getCurSmeVecLenInBits(), gem5::ArmISA::isSecure(), gem5::ArmISA::len, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_SVCR, gem5::ArmISA::MISCREG_ZCR_EL1, gem5::ArmISA::MISCREG_ZCR_EL2, gem5::ArmISA::MISCREG_ZCR_EL3, miscRegs, panic_if, release, sveVL, and gem5::BaseISA::tc.

Referenced by gem5::ArmISA::ArmStaticInst::getCurSveVecLenInBits(), and setMiscReg().

◆ getCurSveVecLenInBitsAtReset()

|

inline |

◆ getExecutingAsid()

|

inlineoverridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 409 of file isa.hh.

References gem5::ArmISA::MISCREG_CONTEXTIDR, and readMiscRegNoEffect().

◆ getGenericTimer()

|

protected |

Definition at line 1364 of file isa.cc.

References panic, system, gem5::BaseISA::tc, and timer.

Referenced by readMiscReg(), and setMiscReg().

◆ getGICv3CPUInterface() [1/2]

|

protected |

Definition at line 1385 of file isa.cc.

References getGICv3CPUInterface(), gicv3CpuInterface, panic_if, and gem5::BaseISA::tc.

Referenced by getGICv3CPUInterface(), readMiscReg(), setMiscReg(), and setupThreadContext().

◆ getGICv3CPUInterface() [2/2]

|

protected |

Definition at line 1398 of file isa.cc.

References gem5::Gicv3::getCPUInterface(), system, and gem5::BaseISA::tc.

◆ getMiscIndices()

|

inline |

Definition at line 338 of file isa.hh.

References flattenMiscIndex(), highestELIs64, inSecureState(), gem5::ArmISA::lookUpMiscReg, and gem5::ArmISA::MISCREG_BANKED_CHILD.

Referenced by readMiscRegNoEffect(), and setMiscRegNoEffect().

◆ getRelease()

|

inline |

Definition at line 194 of file isa.hh.

References release.

Referenced by gem5::ArmISA::HaveExt(), and gem5::TlbiOp::performTlbi().

◆ getSelfDebug() [1/2]

|

inline |

Definition at line 182 of file isa.hh.

References selfDebug.

Referenced by gem5::ArmISA::ArmStaticInst::activateBreakpoint(), gem5::DebugStep::execute(), gem5::ArmISA::ArmStaticInst::getPSTATEFromPSR(), getSelfDebug(), and gem5::ArmISA::MMU::translateFs().

◆ getSelfDebug() [2/2]

|

inlinestatic |

Definition at line 188 of file isa.hh.

References getSelfDebug(), and gem5::BaseISA::tc.

◆ getVectorLengthInBytes()

|

inlineoverridevirtual |

This function returns the vector length of the Vector Length Agnostic extension of the ISA.

For ARM ISA, this function returns the SVE/SVE2 vector length. For RISC-V ISA, this function returns the RVV vector length. For other ISAs, this function returns -1.

Reimplemented from gem5::BaseISA.

Definition at line 440 of file isa.hh.

References sveVL.

◆ globalClearExclusive() [1/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1773 of file isa.cc.

References DPRINTF, gem5::ArmISA::MISCREG_LOCKFLAG, gem5::ArmISA::MISCREG_SEV_MAILBOX, gem5::ArmISA::sendEvent(), and gem5::BaseISA::tc.

◆ globalClearExclusive() [2/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1787 of file isa.cc.

References DPRINTF, gem5::ArmISA::MISCREG_LOCKFLAG, gem5::ArmISA::MISCREG_SEV_MAILBOX, gem5::ArmISA::sendEvent(), gem5::ExecContext::setMiscReg(), and gem5::ExecContext::tcBase().

◆ handleLockedRead() [1/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1683 of file isa.cc.

References DPRINTF, gem5::ArmISA::MISCREG_LOCKADDR, gem5::ArmISA::MISCREG_LOCKFLAG, and gem5::BaseISA::tc.

◆ handleLockedRead() [2/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1692 of file isa.cc.

References DPRINTF, gem5::ThreadContext::getCpuPtr(), gem5::ArmISA::MISCREG_LOCKADDR, gem5::ArmISA::MISCREG_LOCKFLAG, gem5::Named::name(), gem5::ExecContext::setMiscReg(), and gem5::ExecContext::tcBase().

◆ handleLockedSnoop() [1/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1677 of file isa.cc.

References gem5::ArmISA::lockedSnoopHandler(), and gem5::ExecContext::tcBase().

◆ handleLockedSnoop() [2/2]

Reimplemented from gem5::BaseISA.

Definition at line 1671 of file isa.cc.

References gem5::ArmISA::lockedSnoopHandler(), and gem5::BaseISA::tc.

◆ handleLockedSnoopHit() [1/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1701 of file isa.cc.

References DPRINTF, gem5::ArmISA::MISCREG_LOCKADDR, gem5::ArmISA::MISCREG_LOCKFLAG, gem5::ArmISA::MISCREG_SEV_MAILBOX, and gem5::BaseISA::tc.

◆ handleLockedSnoopHit() [2/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1710 of file isa.cc.

References DPRINTF, gem5::ThreadContext::getCpuPtr(), gem5::ArmISA::MISCREG_LOCKADDR, gem5::ArmISA::MISCREG_LOCKFLAG, gem5::ArmISA::MISCREG_SEV_MAILBOX, gem5::Named::name(), gem5::ExecContext::readMiscReg(), gem5::ExecContext::setMiscReg(), and gem5::ExecContext::tcBase().

◆ handleLockedWrite() [1/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1760 of file isa.cc.

References gem5::ArmISA::lockedWriteHandler(), and gem5::BaseISA::tc.

◆ handleLockedWrite() [2/2]

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 1766 of file isa.cc.

References gem5::ArmISA::lockedWriteHandler(), and gem5::ExecContext::tcBase().

◆ initializeMiscRegMetadata()

|

protected |

Some registers alias with others, and therefore need to be translated. When two mapping registers are given, they are the 32b lower and upper halves, respectively, of the 64b register being mapped. aligned with reference documentation ARM DDI 0487A.i pp 1540-1543

NAM = "not architecturally mandated", from ARM DDI 0487A.i, template text "AArch64 System register ___ can be mapped to AArch32 System register ___, but this is not architecturally mandated."

Definition at line 3082 of file misc.cc.

References gem5::ArmISA::MiscRegLUTEntryInitializer::allPrivileges(), gem5::ArmISA::MiscRegLUTEntryInitializer::banked(), gem5::ArmISA::MiscRegLUTEntryInitializer::bankedChild(), gem5::ArmISA::MiscRegLUTEntryInitializer::exceptUserMode(), highestELIs64, InitReg(), gem5::ArmISA::mask, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_CPSR_MODE, gem5::ArmISA::MISCREG_CPSR_Q, gem5::ArmISA::MISCREG_CTR, gem5::ArmISA::MISCREG_DBGAUTHSTATUS, gem5::ArmISA::MISCREG_DBGBCR0, gem5::ArmISA::MISCREG_DBGBCR1, gem5::ArmISA::MISCREG_DBGBCR10, gem5::ArmISA::MISCREG_DBGBCR11, gem5::ArmISA::MISCREG_DBGBCR12, gem5::ArmISA::MISCREG_DBGBCR13, gem5::ArmISA::MISCREG_DBGBCR14, gem5::ArmISA::MISCREG_DBGBCR15, gem5::ArmISA::MISCREG_DBGBCR2, gem5::ArmISA::MISCREG_DBGBCR3, gem5::ArmISA::MISCREG_DBGBCR4, gem5::ArmISA::MISCREG_DBGBCR5, gem5::ArmISA::MISCREG_DBGBCR6, gem5::ArmISA::MISCREG_DBGBCR7, gem5::ArmISA::MISCREG_DBGBCR8, gem5::ArmISA::MISCREG_DBGBCR9, gem5::ArmISA::MISCREG_DBGBVR0, gem5::ArmISA::MISCREG_DBGBVR1, gem5::ArmISA::MISCREG_DBGBVR10, gem5::ArmISA::MISCREG_DBGBVR11, gem5::ArmISA::MISCREG_DBGBVR12, gem5::ArmISA::MISCREG_DBGBVR13, gem5::ArmISA::MISCREG_DBGBVR14, gem5::ArmISA::MISCREG_DBGBVR15, gem5::ArmISA::MISCREG_DBGBVR2, gem5::ArmISA::MISCREG_DBGBVR3, gem5::ArmISA::MISCREG_DBGBVR4, gem5::ArmISA::MISCREG_DBGBVR5, gem5::ArmISA::MISCREG_DBGBVR6, gem5::ArmISA::MISCREG_DBGBVR7, gem5::ArmISA::MISCREG_DBGBVR8, gem5::ArmISA::MISCREG_DBGBVR9, gem5::ArmISA::MISCREG_DBGBXVR0, gem5::ArmISA::MISCREG_DBGBXVR1, gem5::ArmISA::MISCREG_DBGBXVR10, gem5::ArmISA::MISCREG_DBGBXVR11, gem5::ArmISA::MISCREG_DBGBXVR12, gem5::ArmISA::MISCREG_DBGBXVR13, gem5::ArmISA::MISCREG_DBGBXVR14, gem5::ArmISA::MISCREG_DBGBXVR15, gem5::ArmISA::MISCREG_DBGBXVR2, gem5::ArmISA::MISCREG_DBGBXVR3, gem5::ArmISA::MISCREG_DBGBXVR4, gem5::ArmISA::MISCREG_DBGBXVR5, gem5::ArmISA::MISCREG_DBGBXVR6, gem5::ArmISA::MISCREG_DBGBXVR7, gem5::ArmISA::MISCREG_DBGBXVR8, gem5::ArmISA::MISCREG_DBGBXVR9, gem5::ArmISA::MISCREG_DBGCLAIMCLR, gem5::ArmISA::MISCREG_DBGCLAIMSET, gem5::ArmISA::MISCREG_DBGDCCINT, gem5::ArmISA::MISCREG_DBGDEVID0, gem5::ArmISA::MISCREG_DBGDEVID1, gem5::ArmISA::MISCREG_DBGDEVID2, gem5::ArmISA::MISCREG_DBGDIDR, gem5::ArmISA::MISCREG_DBGDRAR, gem5::ArmISA::MISCREG_DBGDSAR, gem5::ArmISA::MISCREG_DBGDSCRext, gem5::ArmISA::MISCREG_DBGDSCRint, gem5::ArmISA::MISCREG_DBGDTRRXext, gem5::ArmISA::MISCREG_DBGDTRRXint, gem5::ArmISA::MISCREG_DBGDTRTXext, gem5::ArmISA::MISCREG_DBGDTRTXint, gem5::ArmISA::MISCREG_DBGOSDLR, gem5::ArmISA::MISCREG_DBGOSECCR, gem5::ArmISA::MISCREG_DBGOSLAR, gem5::ArmISA::MISCREG_DBGOSLSR, gem5::ArmISA::MISCREG_DBGPRCR, gem5::ArmISA::MISCREG_DBGVCR, gem5::ArmISA::MISCREG_DBGWCR0, gem5::ArmISA::MISCREG_DBGWCR1, gem5::ArmISA::MISCREG_DBGWCR10, gem5::ArmISA::MISCREG_DBGWCR11, gem5::ArmISA::MISCREG_DBGWCR12, gem5::ArmISA::MISCREG_DBGWCR13, gem5::ArmISA::MISCREG_DBGWCR14, gem5::ArmISA::MISCREG_DBGWCR15, gem5::ArmISA::MISCREG_DBGWCR2, gem5::ArmISA::MISCREG_DBGWCR3, gem5::ArmISA::MISCREG_DBGWCR4, gem5::ArmISA::MISCREG_DBGWCR5, gem5::ArmISA::MISCREG_DBGWCR6, gem5::ArmISA::MISCREG_DBGWCR7, gem5::ArmISA::MISCREG_DBGWCR8, gem5::ArmISA::MISCREG_DBGWCR9, gem5::ArmISA::MISCREG_DBGWFAR, gem5::ArmISA::MISCREG_DBGWVR0, gem5::ArmISA::MISCREG_DBGWVR1, gem5::ArmISA::MISCREG_DBGWVR10, gem5::ArmISA::MISCREG_DBGWVR11, gem5::ArmISA::MISCREG_DBGWVR12, gem5::ArmISA::MISCREG_DBGWVR13, gem5::ArmISA::MISCREG_DBGWVR14, gem5::ArmISA::MISCREG_DBGWVR15, gem5::ArmISA::MISCREG_DBGWVR2, gem5::ArmISA::MISCREG_DBGWVR3, gem5::ArmISA::MISCREG_DBGWVR4, gem5::ArmISA::MISCREG_DBGWVR5, gem5::ArmISA::MISCREG_DBGWVR6, gem5::ArmISA::MISCREG_DBGWVR7, gem5::ArmISA::MISCREG_DBGWVR8, gem5::ArmISA::MISCREG_DBGWVR9, gem5::ArmISA::MISCREG_ELR_HYP, gem5::ArmISA::MISCREG_FPEXC, gem5::ArmISA::MISCREG_FPSCR, gem5::ArmISA::MISCREG_FPSCR_EXC, gem5::ArmISA::MISCREG_FPSCR_QC, gem5::ArmISA::MISCREG_FPSID, gem5::ArmISA::MISCREG_JIDR, gem5::ArmISA::MISCREG_JMCR, gem5::ArmISA::MISCREG_JOSCR, gem5::ArmISA::MISCREG_LOCKADDR, gem5::ArmISA::MISCREG_LOCKFLAG, gem5::ArmISA::MISCREG_MIDR, gem5::ArmISA::MISCREG_MVFR0, gem5::ArmISA::MISCREG_MVFR1, gem5::ArmISA::MISCREG_NMRR_MAIR1, gem5::ArmISA::MISCREG_NMRR_MAIR1_NS, gem5::ArmISA::MISCREG_NMRR_MAIR1_S, gem5::ArmISA::MISCREG_PMXEVTYPER_PMCCFILTR, gem5::ArmISA::MISCREG_PRRR_MAIR0, gem5::ArmISA::MISCREG_PRRR_MAIR0_NS, gem5::ArmISA::MISCREG_PRRR_MAIR0_S, gem5::ArmISA::MISCREG_SEV_MAILBOX, gem5::ArmISA::MISCREG_SPSR, gem5::ArmISA::MISCREG_SPSR_ABT, gem5::ArmISA::MISCREG_SPSR_FIQ, gem5::ArmISA::MISCREG_SPSR_HYP, gem5::ArmISA::MISCREG_SPSR_IRQ, gem5::ArmISA::MISCREG_SPSR_MON, gem5::ArmISA::MISCREG_SPSR_SVC, gem5::ArmISA::MISCREG_SPSR_UND, gem5::ArmISA::MISCREG_TEECR, gem5::ArmISA::MISCREG_TEEHBR, gem5::ArmISA::MISCREG_TLBINEEDSYNC, gem5::ArmISA::MiscRegLUTEntryInitializer::monNonSecureRead(), gem5::ArmISA::MiscRegLUTEntryInitializer::monNonSecureWrite(), gem5::ArmISA::MiscRegLUTEntryInitializer::monSecureRead(), gem5::ArmISA::MiscRegLUTEntryInitializer::monSecureWrite(), gem5::ArmISA::MiscRegLUTEntryInitializer::mutex(), gem5::MipsISA::p, gem5::SimObject::params(), gem5::ArmISA::MiscRegLUTEntryInitializer::privSecure(), gem5::ArmISA::MiscRegLUTEntryInitializer::raz(), release, gem5::ArmISA::MiscRegLUTEntryInitializer::res0(), gem5::ArmISA::MiscRegLUTEntryInitializer::reset(), gem5::ArmISA::resetCPSR(), system, gem5::ArmISA::MiscRegLUTEntryInitializer::unimplemented(), gem5::ArmISA::MiscRegLUTEntryInitializer::warnNotFail(), and gem5::ArmISA::MiscRegLUTEntryInitializer::writes().

Referenced by ISA().

◆ InitReg()

|

inlineprotected |

Definition at line 118 of file isa.hh.

References gem5::ArmISA::lookUpMiscReg, and gem5::X86ISA::reg.

Referenced by initializeMiscRegMetadata(), and setMiscRegReset().

◆ inSecureState()

| bool gem5::ArmISA::ISA::inSecureState | ( | ) | const |

Return true if the PE is in Secure state.

Definition at line 1410 of file isa.cc.

References gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_SCR, miscRegs, gem5::ArmISA::MODE_EL2H, gem5::ArmISA::MODE_EL2T, gem5::ArmISA::MODE_EL3H, gem5::ArmISA::MODE_EL3T, gem5::ArmISA::MODE_HYP, gem5::ArmISA::MODE_MON, and release.

Referenced by flattenMiscIndex(), and getMiscIndices().

◆ inUserMode()

|

inlineoverridevirtual |

Implements gem5::BaseISA.

Definition at line 415 of file isa.hh.

References gem5::ArmISA::inUserMode(), gem5::ArmISA::MISCREG_CPSR, and miscRegs.

◆ mapIntRegId()

◆ newPCState()

|

inlineoverridevirtual |

Implements gem5::BaseISA.

◆ PARAMS()

| gem5::ArmISA::ISA::PARAMS | ( | ArmISA | ) |

References gem5::MipsISA::p.

◆ readMiscReg()

Implements gem5::BaseISA.

Definition at line 423 of file isa.cc.

References gem5::ArmISA::cc_reg::C, currEL(), DPRINTF, gem5::ArmISA::EL1, gem5::ArmISA::EL2Enabled(), gem5::ArmISA::EL3, gem5::ArmISA::ELIs32(), gem5::ArmISA::FpscrExcMask, gem5::ArmISA::FpscrFpcrMask, gem5::ArmISA::FpscrFpsrMask, gem5::ArmISA::FpscrQcMask, gem5::FullSystem, getGenericTimer(), getGICv3CPUInterface(), highestEL, gem5::ArmISA::isSecure(), gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::MISCREG_ACTLR, gem5::ArmISA::MISCREG_CCSIDR, gem5::ArmISA::MISCREG_CLIDR, gem5::ArmISA::MISCREG_CNTFRQ, gem5::ArmISA::MISCREG_CNTFRQ_EL0, gem5::ArmISA::MISCREG_CNTVOFF, gem5::ArmISA::MISCREG_CNTVOFF_EL2, gem5::ArmISA::MISCREG_CPACR, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_CPSR_Q, gem5::ArmISA::MISCREG_CURRENTEL, gem5::ArmISA::MISCREG_DAIF, gem5::ArmISA::MISCREG_DFAR_S, gem5::ArmISA::MISCREG_FPCR, gem5::ArmISA::MISCREG_FPSCR, gem5::ArmISA::MISCREG_FPSCR_EXC, gem5::ArmISA::MISCREG_FPSCR_QC, gem5::ArmISA::MISCREG_FPSR, gem5::ArmISA::MISCREG_HCPTR, gem5::ArmISA::MISCREG_HCR_EL2, gem5::ArmISA::MISCREG_HDFAR, gem5::ArmISA::MISCREG_HIFAR, gem5::ArmISA::MISCREG_ICC_AP0R0, gem5::ArmISA::MISCREG_ICC_IGRPEN1_EL3, gem5::ArmISA::MISCREG_ICC_PMR_EL1, gem5::ArmISA::MISCREG_ICH_AP0R0_EL2, gem5::ArmISA::MISCREG_ICH_LR15_EL2, gem5::ArmISA::MISCREG_ICH_LRC15, gem5::ArmISA::MISCREG_ID_AFR0, gem5::ArmISA::MISCREG_IFAR_S, gem5::ArmISA::MISCREG_IMPLEMENTED, gem5::ArmISA::MISCREG_ISR, gem5::ArmISA::MISCREG_ISR_EL1, gem5::ArmISA::MISCREG_L2CTLR, gem5::ArmISA::MISCREG_MIDR, gem5::ArmISA::MISCREG_MIDR_EL1, gem5::ArmISA::MISCREG_MPAM1_EL1, gem5::ArmISA::MISCREG_MPAM2_EL2, gem5::ArmISA::MISCREG_MPIDR, gem5::ArmISA::MISCREG_MPIDR_EL1, gem5::ArmISA::MISCREG_NSACR, gem5::ArmISA::MISCREG_NZCV, gem5::ArmISA::MISCREG_PAN, gem5::ArmISA::MISCREG_PMCR, gem5::ArmISA::MISCREG_PMEVCNTR0_EL0, gem5::ArmISA::MISCREG_PMEVTYPER5_EL0, gem5::ArmISA::MISCREG_PMINTENSET_EL1, gem5::ArmISA::MISCREG_PMOVSSET, gem5::ArmISA::MISCREG_PMOVSSET_EL0, gem5::ArmISA::MISCREG_PMXEVTYPER_PMCCFILTR, gem5::ArmISA::MISCREG_REVIDR, gem5::ArmISA::MISCREG_RNDR, gem5::ArmISA::MISCREG_RNDRRS, gem5::ArmISA::MISCREG_SCR_EL3, gem5::ArmISA::MISCREG_SP_EL0, gem5::ArmISA::MISCREG_SP_EL1, gem5::ArmISA::MISCREG_SP_EL2, gem5::ArmISA::MISCREG_SPSEL, gem5::ArmISA::MISCREG_UAO, gem5::ArmISA::MISCREG_VPIDR, gem5::ArmISA::MISCREG_WARN_NOT_FAIL, gem5::ArmISA::miscRegName, miscRegs, gem5::ArmISA::MODE_MON, gem5::ArmISA::cc_reg::Nz, panic, gem5::MipsISA::pc, pmu, gem5::ArmISA::BaseISADevice::readMiscReg(), readMiscRegNoEffect(), gem5::ArmISA::readMPIDR(), gem5::ArmISA::misc_regs::readRegisterNoEffect(), redirectRegVHE(), release, rng, gem5::ArmISA::int_reg::Sp0, gem5::ArmISA::int_reg::Sp1, gem5::ArmISA::int_reg::Sp2, system, gem5::BaseISA::tc, gem5::ArmISA::unflattenMiscReg(), gem5::ArmISA::cc_reg::V, gem5::X86ISA::val, warn, and warn_once.

◆ readMiscRegNoEffect()

Implements gem5::BaseISA.

Definition at line 399 of file isa.cc.

References DPRINTF, getMiscIndices(), gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::mask, gem5::ArmISA::miscRegName, miscRegs, gem5::ArmISA::NUM_MISCREGS, gem5::X86ISA::reg, and gem5::X86ISA::val.

Referenced by addressTranslation(), currEL(), gem5::ArmISA::IntRegClassOps::flatten(), flattenMiscIndex(), getExecutingAsid(), gem5::SparcISA::ISA::readFSReg(), readMiscReg(), redirectRegVHE(), and setMiscReg().

◆ readMiscRegReset()

Definition at line 1350 of file isa.cc.

References flattenMiscIndex(), and gem5::ArmISA::lookUpMiscReg.

◆ redirectRegVHE()

| int gem5::ArmISA::ISA::redirectRegVHE | ( | int | misc_reg | ) |

Returns the enconcing equivalent when VHE is implemented and HCR_EL2.E2H is enabled and executing at EL2.

Definition at line 233 of file isa.cc.

References currEL(), gem5::ArmISA::EL2, gem5::ArmISA::ELIsInHost(), gem5::ArmISA::MISCREG_AFSR0_EL1, gem5::ArmISA::MISCREG_AFSR0_EL12, gem5::ArmISA::MISCREG_AFSR0_EL2, gem5::ArmISA::MISCREG_AFSR1_EL1, gem5::ArmISA::MISCREG_AFSR1_EL12, gem5::ArmISA::MISCREG_AFSR1_EL2, gem5::ArmISA::MISCREG_AMAIR_EL1, gem5::ArmISA::MISCREG_AMAIR_EL12, gem5::ArmISA::MISCREG_AMAIR_EL2, gem5::ArmISA::MISCREG_CNTHCTL_EL2, gem5::ArmISA::MISCREG_CNTHP_CTL_EL2, gem5::ArmISA::MISCREG_CNTHP_CVAL_EL2, gem5::ArmISA::MISCREG_CNTHP_TVAL_EL2, gem5::ArmISA::MISCREG_CNTHPS_CTL_EL2, gem5::ArmISA::MISCREG_CNTHPS_CVAL_EL2, gem5::ArmISA::MISCREG_CNTHPS_TVAL_EL2, gem5::ArmISA::MISCREG_CNTHV_CTL_EL2, gem5::ArmISA::MISCREG_CNTHV_CVAL_EL2, gem5::ArmISA::MISCREG_CNTHV_TVAL_EL2, gem5::ArmISA::MISCREG_CNTHVS_CTL_EL2, gem5::ArmISA::MISCREG_CNTHVS_CVAL_EL2, gem5::ArmISA::MISCREG_CNTHVS_TVAL_EL2, gem5::ArmISA::MISCREG_CNTKCTL_EL1, gem5::ArmISA::MISCREG_CNTKCTL_EL12, gem5::ArmISA::MISCREG_CNTP_CTL, gem5::ArmISA::MISCREG_CNTP_CTL_EL0, gem5::ArmISA::MISCREG_CNTP_CTL_EL02, gem5::ArmISA::MISCREG_CNTP_CVAL, gem5::ArmISA::MISCREG_CNTP_CVAL_EL0, gem5::ArmISA::MISCREG_CNTP_CVAL_EL02, gem5::ArmISA::MISCREG_CNTP_TVAL, gem5::ArmISA::MISCREG_CNTP_TVAL_EL0, gem5::ArmISA::MISCREG_CNTP_TVAL_EL02, gem5::ArmISA::MISCREG_CNTPCT_EL0, gem5::ArmISA::MISCREG_CNTV_CTL, gem5::ArmISA::MISCREG_CNTV_CTL_EL0, gem5::ArmISA::MISCREG_CNTV_CTL_EL02, gem5::ArmISA::MISCREG_CNTV_CVAL, gem5::ArmISA::MISCREG_CNTV_CVAL_EL0, gem5::ArmISA::MISCREG_CNTV_CVAL_EL02, gem5::ArmISA::MISCREG_CNTV_TVAL, gem5::ArmISA::MISCREG_CNTV_TVAL_EL0, gem5::ArmISA::MISCREG_CNTV_TVAL_EL02, gem5::ArmISA::MISCREG_CNTVCT, gem5::ArmISA::MISCREG_CNTVCT_EL0, gem5::ArmISA::MISCREG_CONTEXTIDR_EL1, gem5::ArmISA::MISCREG_CONTEXTIDR_EL12, gem5::ArmISA::MISCREG_CONTEXTIDR_EL2, gem5::ArmISA::MISCREG_CPACR_EL1, gem5::ArmISA::MISCREG_CPACR_EL12, gem5::ArmISA::MISCREG_CPTR_EL2, gem5::ArmISA::MISCREG_ELR_EL1, gem5::ArmISA::MISCREG_ELR_EL12, gem5::ArmISA::MISCREG_ELR_EL2, gem5::ArmISA::MISCREG_ESR_EL1, gem5::ArmISA::MISCREG_ESR_EL12, gem5::ArmISA::MISCREG_ESR_EL2, gem5::ArmISA::MISCREG_FAR_EL1, gem5::ArmISA::MISCREG_FAR_EL12, gem5::ArmISA::MISCREG_FAR_EL2, gem5::ArmISA::MISCREG_HCR_EL2, gem5::ArmISA::MISCREG_MAIR_EL1, gem5::ArmISA::MISCREG_MAIR_EL12, gem5::ArmISA::MISCREG_MAIR_EL2, gem5::ArmISA::MISCREG_MPAM1_EL1, gem5::ArmISA::MISCREG_MPAM1_EL12, gem5::ArmISA::MISCREG_MPAM2_EL2, gem5::ArmISA::MISCREG_PIR_EL1, gem5::ArmISA::MISCREG_PIR_EL12, gem5::ArmISA::MISCREG_PIR_EL2, gem5::ArmISA::MISCREG_PIRE0_EL1, gem5::ArmISA::MISCREG_PIRE0_EL12, gem5::ArmISA::MISCREG_PIRE0_EL2, gem5::ArmISA::MISCREG_SCR_EL3, gem5::ArmISA::MISCREG_SCTLR2_EL1, gem5::ArmISA::MISCREG_SCTLR2_EL12, gem5::ArmISA::MISCREG_SCTLR_EL1, gem5::ArmISA::MISCREG_SCTLR_EL12, gem5::ArmISA::MISCREG_SCTLR_EL2, gem5::ArmISA::MISCREG_SPSR_EL1, gem5::ArmISA::MISCREG_SPSR_EL12, gem5::ArmISA::MISCREG_SPSR_EL2, gem5::ArmISA::MISCREG_TCR2_EL1, gem5::ArmISA::MISCREG_TCR2_EL12, gem5::ArmISA::MISCREG_TCR2_EL2, gem5::ArmISA::MISCREG_TCR_EL1, gem5::ArmISA::MISCREG_TCR_EL12, gem5::ArmISA::MISCREG_TCR_EL2, gem5::ArmISA::MISCREG_TTBR0_EL1, gem5::ArmISA::MISCREG_TTBR0_EL12, gem5::ArmISA::MISCREG_TTBR0_EL2, gem5::ArmISA::MISCREG_TTBR1_EL1, gem5::ArmISA::MISCREG_TTBR1_EL12, gem5::ArmISA::MISCREG_TTBR1_EL2, gem5::ArmISA::MISCREG_VBAR_EL1, gem5::ArmISA::MISCREG_VBAR_EL12, gem5::ArmISA::MISCREG_VBAR_EL2, gem5::ArmISA::MISCREG_ZCR_EL1, gem5::ArmISA::MISCREG_ZCR_EL12, gem5::ArmISA::MISCREG_ZCR_EL2, readMiscRegNoEffect(), release, and gem5::BaseISA::tc.

Referenced by readMiscReg(), and setMiscReg().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::BaseISA.

Definition at line 1543 of file isa.cc.

References DPRINTF, gem5::ArmISA::miscRegName, miscRegs, gem5::ArmISA::NUM_PHYS_MISCREGS, gem5::BaseISA::serialize(), and SERIALIZE_MAPPING.

◆ setMiscReg()

Implements gem5::BaseISA.

Definition at line 703 of file isa.cc.

References addressTranslation(), gem5::bits(), gem5::ArmISA::cc_reg::C, gem5::ArmISA::CpsrMaskQ, DPRINTF, gem5::ArmISA::EL3, gem5::ArmISA::ELIs32(), gem5::ArmISA::FpscrExcMask, gem5::ArmISA::FpscrFpcrMask, gem5::ArmISA::FpscrFpsrMask, gem5::ArmISA::FpscrQcMask, getCurSmeVecLenInBits(), getCurSveVecLenInBits(), getGenericTimer(), getGICv3CPUInterface(), gem5::ArmISA::getMMUPtr(), gicv3CpuInterface, highestELIs64, gem5::ArmISA::MMU::HypMode, gem5::ArmISA::MMU::invalidateMiscReg(), gem5::ArmISA::isSecure(), gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::mask, gem5::ArmISA::MISCREG_ACTLR, gem5::ArmISA::MISCREG_ATS12NSOPR, gem5::ArmISA::MISCREG_ATS12NSOPW, gem5::ArmISA::MISCREG_ATS12NSOUR, gem5::ArmISA::MISCREG_ATS12NSOUW, gem5::ArmISA::MISCREG_ATS1CPR, gem5::ArmISA::MISCREG_ATS1CPW, gem5::ArmISA::MISCREG_ATS1CUR, gem5::ArmISA::MISCREG_ATS1CUW, gem5::ArmISA::MISCREG_ATS1HR, gem5::ArmISA::MISCREG_ATS1HW, gem5::ArmISA::MISCREG_CNTFRQ, gem5::ArmISA::MISCREG_CNTFRQ_EL0, gem5::ArmISA::MISCREG_CNTVOFF, gem5::ArmISA::MISCREG_CNTVOFF_EL2, gem5::ArmISA::MISCREG_CONTEXTIDR, gem5::ArmISA::MISCREG_CPACR, gem5::ArmISA::MISCREG_CPACR_EL1, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_CPSR_Q, gem5::ArmISA::MISCREG_CPTR_EL2, gem5::ArmISA::MISCREG_CPTR_EL3, gem5::ArmISA::MISCREG_CSSELR, gem5::ArmISA::MISCREG_CURRENTEL, gem5::ArmISA::MISCREG_DACR, gem5::ArmISA::MISCREG_DAIF, gem5::ArmISA::MISCREG_DBGBCR0, gem5::ArmISA::MISCREG_DBGBCR0_EL1, gem5::ArmISA::MISCREG_DBGBCR15, gem5::ArmISA::MISCREG_DBGBCR15_EL1, gem5::ArmISA::MISCREG_DBGDSCRext, gem5::ArmISA::MISCREG_DBGDSCRint, gem5::ArmISA::MISCREG_DBGOSLAR, gem5::ArmISA::MISCREG_DBGOSLSR, gem5::ArmISA::MISCREG_DBGWCR0, gem5::ArmISA::MISCREG_DBGWCR0_EL1, gem5::ArmISA::MISCREG_DBGWCR15, gem5::ArmISA::MISCREG_DBGWCR15_EL1, gem5::ArmISA::MISCREG_DC_ZVA_Xt, gem5::ArmISA::MISCREG_DFAR_S, gem5::ArmISA::MISCREG_FPCR, gem5::ArmISA::MISCREG_FPEXC, gem5::ArmISA::MISCREG_FPSCR, gem5::ArmISA::MISCREG_FPSCR_EXC, gem5::ArmISA::MISCREG_FPSCR_QC, gem5::ArmISA::MISCREG_FPSID, gem5::ArmISA::MISCREG_FPSR, gem5::ArmISA::MISCREG_HCPTR, gem5::ArmISA::MISCREG_HCR, gem5::ArmISA::MISCREG_HCR_EL2, gem5::ArmISA::MISCREG_HDCR, gem5::ArmISA::MISCREG_HDFAR, gem5::ArmISA::MISCREG_HIFAR, gem5::ArmISA::MISCREG_HSCTLR, gem5::ArmISA::MISCREG_HSTR, gem5::ArmISA::MISCREG_ICC_AP0R0, gem5::ArmISA::MISCREG_ICC_IGRPEN1_EL3, gem5::ArmISA::MISCREG_ICC_PMR_EL1, gem5::ArmISA::MISCREG_ICH_AP0R0_EL2, gem5::ArmISA::MISCREG_ICH_LR15_EL2, gem5::ArmISA::MISCREG_ICH_LRC15, gem5::ArmISA::MISCREG_ID_AA64AFR0_EL1, gem5::ArmISA::MISCREG_ID_AA64AFR1_EL1, gem5::ArmISA::MISCREG_ID_AA64DFR0_EL1, gem5::ArmISA::MISCREG_ID_AA64DFR1_EL1, gem5::ArmISA::MISCREG_ID_AA64ISAR0_EL1, gem5::ArmISA::MISCREG_ID_AA64ISAR1_EL1, gem5::ArmISA::MISCREG_ID_AA64MMFR0_EL1, gem5::ArmISA::MISCREG_ID_AA64MMFR1_EL1, gem5::ArmISA::MISCREG_ID_AA64MMFR2_EL1, gem5::ArmISA::MISCREG_ID_AA64PFR0_EL1, gem5::ArmISA::MISCREG_ID_AA64PFR1_EL1, gem5::ArmISA::MISCREG_ID_DFR0, gem5::ArmISA::MISCREG_ID_ISAR0, gem5::ArmISA::MISCREG_ID_ISAR1, gem5::ArmISA::MISCREG_ID_ISAR2, gem5::ArmISA::MISCREG_ID_ISAR3, gem5::ArmISA::MISCREG_ID_ISAR4, gem5::ArmISA::MISCREG_ID_ISAR5, gem5::ArmISA::MISCREG_ID_MMFR0, gem5::ArmISA::MISCREG_ID_MMFR1, gem5::ArmISA::MISCREG_ID_MMFR2, gem5::ArmISA::MISCREG_ID_MMFR3, gem5::ArmISA::MISCREG_ID_MMFR4, gem5::ArmISA::MISCREG_ID_PFR0, gem5::ArmISA::MISCREG_ID_PFR1, gem5::ArmISA::MISCREG_IFAR_S, gem5::ArmISA::MISCREG_IMPLEMENTED, gem5::ArmISA::MISCREG_L2CTLR, gem5::ArmISA::MISCREG_MAIR0, gem5::ArmISA::MISCREG_MAIR1, gem5::ArmISA::MISCREG_MDCR_EL2, gem5::ArmISA::MISCREG_MDCR_EL3, gem5::ArmISA::MISCREG_MDSCR_EL1, gem5::ArmISA::MISCREG_MIDR, gem5::ArmISA::MISCREG_MPIDR, gem5::ArmISA::MISCREG_MVFR0, gem5::ArmISA::MISCREG_MVFR1, gem5::ArmISA::MISCREG_NMRR, gem5::ArmISA::MISCREG_NSACR, gem5::ArmISA::MISCREG_NZCV, gem5::ArmISA::MISCREG_OSLAR_EL1, gem5::ArmISA::MISCREG_OSLSR_EL1, gem5::ArmISA::MISCREG_PAN, gem5::ArmISA::MISCREG_PIR_EL1, gem5::ArmISA::MISCREG_PIR_EL2, gem5::ArmISA::MISCREG_PIR_EL3, gem5::ArmISA::MISCREG_PIRE0_EL1, gem5::ArmISA::MISCREG_PIRE0_EL2, gem5::ArmISA::MISCREG_PMCR, gem5::ArmISA::MISCREG_PMEVCNTR0_EL0, gem5::ArmISA::MISCREG_PMEVTYPER5_EL0, gem5::ArmISA::MISCREG_PMINTENSET_EL1, gem5::ArmISA::MISCREG_PMOVSSET, gem5::ArmISA::MISCREG_PMOVSSET_EL0, gem5::ArmISA::MISCREG_PMXEVTYPER_PMCCFILTR, gem5::ArmISA::MISCREG_PRRR, gem5::ArmISA::MISCREG_SCR, gem5::ArmISA::MISCREG_SCR_EL3, gem5::ArmISA::MISCREG_SCTLR, gem5::ArmISA::MISCREG_SCTLR_EL1, gem5::ArmISA::MISCREG_SCTLR_EL2, gem5::ArmISA::MISCREG_SCTLR_EL3, gem5::ArmISA::MISCREG_SCTLR_NS, gem5::ArmISA::MISCREG_SCTLR_S, gem5::ArmISA::MISCREG_SDCR, gem5::ArmISA::MISCREG_SMCR_EL1, gem5::ArmISA::MISCREG_SMCR_EL2, gem5::ArmISA::MISCREG_SMCR_EL3, gem5::ArmISA::MISCREG_SP_EL0, gem5::ArmISA::MISCREG_SP_EL1, gem5::ArmISA::MISCREG_SP_EL2, gem5::ArmISA::MISCREG_SPSEL, gem5::ArmISA::MISCREG_TCR2_EL1, gem5::ArmISA::MISCREG_TCR2_EL2, gem5::ArmISA::MISCREG_TCR_EL1, gem5::ArmISA::MISCREG_TCR_EL2, gem5::ArmISA::MISCREG_TCR_EL3, gem5::ArmISA::MISCREG_TLBTR, gem5::ArmISA::MISCREG_TTBCR, gem5::ArmISA::MISCREG_TTBR0, gem5::ArmISA::MISCREG_TTBR0_EL1, gem5::ArmISA::MISCREG_TTBR0_EL2, gem5::ArmISA::MISCREG_TTBR0_EL3, gem5::ArmISA::MISCREG_TTBR1, gem5::ArmISA::MISCREG_TTBR1_EL1, gem5::ArmISA::MISCREG_TTBR1_EL2, gem5::ArmISA::MISCREG_UAO, gem5::ArmISA::MISCREG_VTCR_EL2, gem5::ArmISA::MISCREG_VTTBR, gem5::ArmISA::MISCREG_WARN_NOT_FAIL, gem5::ArmISA::MISCREG_ZCR_EL1, gem5::ArmISA::MISCREG_ZCR_EL2, gem5::ArmISA::MISCREG_ZCR_EL3, gem5::ArmISA::miscRegName, miscRegs, gem5::ArmISA::MODE_MON, gem5::ArmISA::cc_reg::Nz, panic, gem5::MipsISA::pc, pmu, gem5::MipsISA::r, gem5::BaseMMU::Read, readMiscRegNoEffect(), redirectRegVHE(), release, gem5::ArmISA::MMU::S1CTran, gem5::ArmISA::MMU::S1S2NsTran, selfDebug, gem5::ArmISA::BaseISADevice::setMiscReg(), setMiscRegNoEffect(), gem5::ArmISA::int_reg::Sp0, gem5::ArmISA::int_reg::Sp1, gem5::ArmISA::int_reg::Sp2, gem5::BaseISA::tc, gem5::ArmISA::unflattenMiscReg(), updateRegMap(), gem5::ArmISA::MMU::UserMode, gem5::ArmISA::cc_reg::V, gem5::ArmISA::v, gem5::X86ISA::val, warn, warn_once, and gem5::BaseMMU::Write.

Referenced by gem5::SparcISA::ISA::processHSTickCompare(), gem5::SparcISA::ISA::processSTickCompare(), and gem5::SparcISA::ISA::setFSReg().

◆ setMiscRegNoEffect()

Implements gem5::BaseISA.

Definition at line 681 of file isa.cc.

References gem5::bits(), DPRINTF, getMiscIndices(), gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::miscRegName, miscRegs, gem5::ArmISA::NUM_MISCREGS, gem5::X86ISA::reg, gem5::ArmISA::v, and gem5::X86ISA::val.

Referenced by addressTranslation(), gem5::SparcISA::ISA::setFSReg(), and setMiscReg().

◆ setMiscRegReset()

Definition at line 1357 of file isa.cc.

References flattenMiscIndex(), InitReg(), gem5::ArmISA::MiscRegLUTEntryInitializer::reset(), and gem5::X86ISA::val.

◆ setupThreadContext()

| void gem5::ArmISA::ISA::setupThreadContext | ( | ) |

Definition at line 168 of file isa.cc.

References getGICv3CPUInterface(), pmu, selfDebug, system, and gem5::BaseISA::tc.

Referenced by startup(), and takeOverFrom().

◆ snsBankedIndex64()

|

inline |

Definition at line 327 of file isa.hh.

References gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::MISCREG_BANKED64, gem5::ArmISA::ns, gem5::X86ISA::reg, and release.

Referenced by flattenMiscIndex().

◆ startup()

|

overridevirtual |

startup() is the final initialization call before simulation.

All state is initialized (including unserialized state, if any, such as the curTick() value), so this is the appropriate place to schedule initial event(s) for objects that need them.

Reimplemented from gem5::SimObject.

Definition at line 153 of file isa.cc.

References release, setupThreadContext(), gem5::SimObject::startup(), and gem5::BaseISA::tc.

◆ takeOverFrom()

|

overridevirtual |

Reimplemented from gem5::BaseISA.

Definition at line 184 of file isa.cc.

References setupThreadContext(), and gem5::BaseISA::tc.

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 1552 of file isa.cc.

References DPRINTF, gem5::ArmISA::lookUpMiscReg, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_UNSERIALIZE, gem5::ArmISA::miscRegName, miscRegs, gem5::ArmISA::NUM_MISCREGS, gem5::ArmISA::NUM_PHYS_MISCREGS, gem5::statistics::reset(), UNSERIALIZE_MAPPING, updateRegMap(), and warn.

◆ updateRegMap()

|

inlineprotected |

Definition at line 133 of file isa.hh.

References intRegMap, gem5::ArmISA::MODE_ABORT, gem5::ArmISA::MODE_FIQ, gem5::ArmISA::MODE_HYP, gem5::ArmISA::MODE_IRQ, gem5::ArmISA::MODE_MON, gem5::ArmISA::MODE_SVC, gem5::ArmISA::MODE_SYSTEM, gem5::ArmISA::MODE_UNDEFINED, gem5::ArmISA::MODE_USER, panic, gem5::ArmISA::int_reg::Reg64Map, gem5::ArmISA::int_reg::RegAbtMap, gem5::ArmISA::int_reg::RegFiqMap, gem5::ArmISA::int_reg::RegHypMap, gem5::ArmISA::int_reg::RegIrqMap, gem5::ArmISA::int_reg::RegMonMap, gem5::ArmISA::int_reg::RegSvcMap, gem5::ArmISA::int_reg::RegUndMap, and gem5::ArmISA::int_reg::RegUsrMap.

Referenced by clear(), setMiscReg(), and unserialize().

◆ zeroSveVecRegUpperPart()

|

inlinestatic |

Definition at line 376 of file isa.hh.

References gem5::ArmISA::i, and gem5::ArmISA::v.

Member Data Documentation

◆ _decoderFlavor

|

protected |

Definition at line 78 of file isa.hh.

Referenced by decoderFlavor(), and ISA().

◆ dummyDevice

|

protected |

◆ gicv3CpuInterface

|

protected |

Definition at line 90 of file isa.hh.

Referenced by getGICv3CPUInterface(), and setMiscReg().

◆ haveLargeAsid64

|

protected |

◆ highestEL

|

protected |

Definition at line 94 of file isa.hh.

Referenced by ISA(), and readMiscReg().

◆ highestELIs64

|

protected |

Definition at line 93 of file isa.hh.

Referenced by flattenMiscIndex(), getMiscIndices(), initializeMiscRegMetadata(), ISA(), and setMiscReg().

◆ impdefAsNop

|

protected |

◆ intRegMap

|

protected |

Definition at line 130 of file isa.hh.

Referenced by mapIntRegId(), and updateRegMap().

◆ miscRegs

|

protected |

Definition at line 129 of file isa.hh.

Referenced by clear(), flattenMiscIndex(), getCurSmeVecLenInBits(), getCurSveVecLenInBits(), inSecureState(), inUserMode(), readMiscReg(), readMiscRegNoEffect(), serialize(), setMiscReg(), setMiscRegNoEffect(), and unserialize().

◆ physAddrRange

|

protected |

◆ pmu

|

protected |

Definition at line 84 of file isa.hh.

Referenced by ISA(), readMiscReg(), setMiscReg(), and setupThreadContext().

◆ release

|

protected |

This could be either a FS or a SE release.

Definition at line 105 of file isa.hh.

Referenced by addressTranslation(), getCurSmeVecLenInBits(), getCurSveVecLenInBits(), getRelease(), initializeMiscRegMetadata(), inSecureState(), ISA(), readMiscReg(), redirectRegVHE(), setMiscReg(), snsBankedIndex64(), and startup().

◆ rng

|

protected |

Definition at line 115 of file isa.hh.

Referenced by readMiscReg().

◆ selfDebug

|

protected |

Definition at line 113 of file isa.hh.

Referenced by getSelfDebug(), ISA(), setMiscReg(), and setupThreadContext().

◆ smeVL

|

protected |

SME vector length in quadwords.

Definition at line 102 of file isa.hh.

Referenced by getCurSmeVecLenInBits(), getCurSmeVecLenInBitsAtReset(), and ISA().

◆ sveVL

|

protected |

SVE vector length in quadwords.

Definition at line 99 of file isa.hh.

Referenced by getCurSveVecLenInBits(), getCurSveVecLenInBitsAtReset(), getVectorLengthInBytes(), and ISA().

◆ system

|

protected |

Definition at line 75 of file isa.hh.

Referenced by getGenericTimer(), getGICv3CPUInterface(), initializeMiscRegMetadata(), ISA(), readMiscReg(), and setupThreadContext().

◆ timer

|

protected |

Definition at line 87 of file isa.hh.

Referenced by getGenericTimer().

The documentation for this class was generated from the following files:

Generated on Mon Oct 27 2025 04:13:16 for gem5 by doxygen 1.14.0