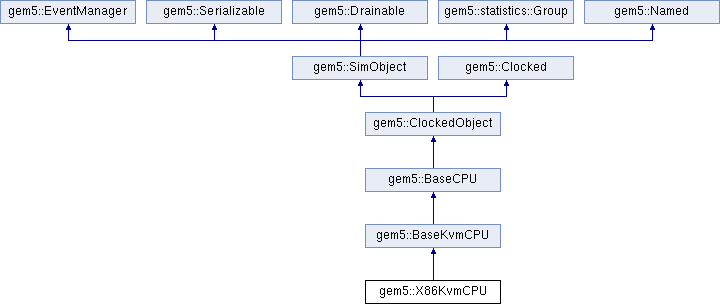

x86 implementation of a KVM-based hardware virtualized CPU. More...

#include <x86_cpu.hh>

Public Member Functions | |

| X86KvmCPU (const X86KvmCPUParams ¶ms) | |

| virtual | ~X86KvmCPU () |

| void | startup () override |

| startup() is the final initialization call before simulation. More... | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| void | dump () const override |

| Dump the internal state to the terminal. More... | |

| void | dumpFpuRegs () const |

| void | dumpIntRegs () const |

| void | dumpSpecRegs () const |

| void | dumpDebugRegs () const |

| void | dumpXCRs () const |

| void | dumpXSave () const |

| void | dumpVCpuEvents () const |

| void | dumpMSRs () const |

Public Member Functions inherited from gem5::BaseKvmCPU Public Member Functions inherited from gem5::BaseKvmCPU | |

| BaseKvmCPU (const BaseKvmCPUParams ¶ms) | |

| virtual | ~BaseKvmCPU () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| void | startup () override |

| startup() is the final initialization call before simulation. More... | |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| Serialize a single thread. More... | |

| void | unserializeThread (CheckpointIn &cp, ThreadID tid) override |

| Unserialize one thread. More... | |

| DrainState | drain () override |

| Draining is the process of clearing out the states of SimObjects.These are the SimObjects that are partially executed or are partially in flight. More... | |

| void | drainResume () override |

| Resume execution after a successful drain. More... | |

| void | notifyFork () override |

| Notify a child process of a fork. More... | |

| void | switchOut () override |

| Prepare for another CPU to take over execution. More... | |

| void | takeOverFrom (BaseCPU *cpu) override |

| Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in. More... | |

| void | verifyMemoryMode () const override |

| Verify that the system is in a memory mode supported by the CPU. More... | |

| Port & | getDataPort () override |

| Purely virtual method that returns a reference to the data port. More... | |

| Port & | getInstPort () override |

| Purely virtual method that returns a reference to the instruction port. More... | |

| void | wakeup (ThreadID tid=0) override |

| void | activateContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now active. More... | |

| void | suspendContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now suspended. More... | |

| void | deallocateContext (ThreadID thread_num) |

| void | haltContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now halted. More... | |

| long | getVCpuID () const |

| ThreadContext * | getContext (int tn) override |

| Given a thread num get tho thread context for it. More... | |

| Counter | totalInsts () const override |

| Counter | totalOps () const override |

| void | finishMMIOPending () |

| Callback from KvmCPUPort to transition the CPU out of RunningMMIOPending when all timing requests have completed. More... | |

| void | kick () const |

| Force an exit from KVM. More... | |

Public Member Functions inherited from gem5::BaseCPU Public Member Functions inherited from gem5::BaseCPU | |

| int | cpuId () const |

| Reads this CPU's ID. More... | |

| uint32_t | socketId () const |

| Reads this CPU's Socket ID. More... | |

| RequestorID | dataRequestorId () const |

| Reads this CPU's unique data requestor ID. More... | |

| RequestorID | instRequestorId () const |

| Reads this CPU's unique instruction requestor ID. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. More... | |

| uint32_t | taskId () const |

| Get cpu task id. More... | |

| void | taskId (uint32_t id) |

| Set cpu task id. More... | |

| uint32_t | getPid () const |

| void | setPid (uint32_t pid) |

| void | workItemBegin () |

| void | workItemEnd () |

| Tick | instCount () |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupts (ThreadID tid) |

| bool | checkInterrupts (ThreadID tid) const |

| trace::InstTracer * | getTracer () |

| Provide access to the tracer pointer. More... | |

| int | findContext (ThreadContext *tc) |

| Given a Thread Context pointer return the thread num. More... | |

| unsigned | numContexts () |

| Get the number of thread contexts available. More... | |

| ThreadID | contextToThread (ContextID cid) |

| Convert ContextID to threadID. More... | |

| PARAMS (BaseCPU) | |

| BaseCPU (const Params ¶ms, bool is_checker=false) | |

| virtual | ~BaseCPU () |

| void | regStats () override |

| Callback to set stat parameters. More... | |

| void | regProbePoints () override |

| Register probe points for this object. More... | |

| void | registerThreadContexts () |

| void | deschedulePowerGatingEvent () |

| void | schedulePowerGatingEvent () |

| virtual void | setReset (bool state) |

| Set the reset of the CPU to be either asserted or deasserted. More... | |

| void | flushTLBs () |

| Flush all TLBs in the CPU. More... | |

| bool | switchedOut () const |

| Determine if the CPU is switched out. More... | |

| unsigned int | cacheLineSize () const |

| Get the cache line size of the system. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. More... | |

| void | scheduleInstStop (ThreadID tid, Counter insts, std::string cause) |

| Schedule an event that exits the simulation loops after a predefined number of instructions. More... | |

| void | scheduleSimpointsInstStop (std::vector< Counter > inst_starts) |

| Schedule simpoint events using the scheduleInstStop function. More... | |

| void | scheduleInstStopAnyThread (Counter max_insts) |

| Schedule an exit event when any threads in the core reach the max_insts instructions using the scheduleInstStop function. More... | |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| Get the number of instructions executed by the specified thread on this CPU. More... | |

| void | traceFunctions (Addr pc) |

| void | armMonitor (ThreadID tid, Addr address) |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseMMU *mmu) |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| virtual void | htmSendAbortSignal (ThreadID tid, uint64_t htm_uid, HtmFailureFaultCause cause) |

| This function is used to instruct the memory subsystem that a transaction should be aborted and the speculative state should be thrown away. More... | |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| Helper method to trigger PMU probes for a committed instruction. More... | |

Public Member Functions inherited from gem5::ClockedObject Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from gem5::SimObject Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. More... | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from gem5::EventManager Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. More... | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. More... | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Public Member Functions inherited from gem5::Serializable Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from gem5::Drainable Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

Public Member Functions inherited from gem5::statistics::Group Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. More... | |

| virtual | ~Group () |

| virtual void | resetStats () |

| Callback to reset stats. More... | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. More... | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. More... | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. More... | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. More... | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. More... | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. More... | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. More... | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

Public Member Functions inherited from gem5::Named Public Member Functions inherited from gem5::Named | |

| Named (const std::string &name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Public Member Functions inherited from gem5::Clocked Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Types | |

| typedef std::vector< struct kvm_msr_entry > | KvmMSRVector |

Protected Types inherited from gem5::BaseKvmCPU Protected Types inherited from gem5::BaseKvmCPU | |

| enum | Status { Idle, Running, RunningService, RunningMMIOPending, RunningServiceCompletion } |

Protected Types inherited from gem5::BaseCPU Protected Types inherited from gem5::BaseCPU | |

| enum | CPUState { CPU_STATE_ON, CPU_STATE_SLEEP, CPU_STATE_WAKEUP } |

Protected Member Functions | |

| Tick | kvmRun (Tick ticks) override |

| Request KVM to run the guest for a given number of ticks. More... | |

| Tick | kvmRunDrain () override |

| Run the virtual CPU until draining completes. More... | |

| uint64_t | getHostCycles () const override |

| Get the value of the hardware cycle counter in the guest. More... | |

| void | stutterPC (PCStateBase &pc) const override |

| Modify a PCStatePtr's value so that its next PC is the current PC. More... | |

| const Kvm::MSRIndexVector & | getMsrIntersection () const |

| Get a list of MSRs supported by both gem5 and KVM. More... | |

| void | updateKvmState () override |

| Update the KVM state from the current thread context. More... | |

| void | updateThreadContext () override |

| Update the current thread context with the KVM state. More... | |

| void | deliverInterrupts () |

| Inject pending interrupts from gem5 into the virtual CPU. More... | |

| Tick | handleKvmExitIO () override |

| Handle x86 legacy IO (in/out) More... | |

| Tick | handleKvmExitIRQWindowOpen () override |

| The guest exited because an interrupt window was requested. More... | |

| bool | archIsDrained () const override |

| Check if there are pending events in the vCPU that prevents it from being drained. More... | |

| void | ioctlRun () override |

| Override for synchronizing state in kvm_run. More... | |

| void | setCPUID (const struct kvm_cpuid2 &cpuid) |

| Methods to access CPUID information using the extended API. More... | |

| void | setCPUID (const Kvm::CPUIDVector &cpuid) |

| void | setMSRs (const struct kvm_msrs &msrs) |

| Methods to access MSRs in the guest. More... | |

| void | setMSRs (const KvmMSRVector &msrs) |

| void | getMSRs (struct kvm_msrs &msrs) const |

| void | setMSR (uint32_t index, uint64_t value) |

| uint64_t | getMSR (uint32_t index) const |

| void | getDebugRegisters (struct kvm_debugregs ®s) const |

| Wrappers around KVM's state transfer methods. More... | |

| void | setDebugRegisters (const struct kvm_debugregs ®s) |

| void | getXCRs (struct kvm_xcrs ®s) const |

| void | setXCRs (const struct kvm_xcrs ®s) |

| void | getXSave (struct kvm_xsave &xsave) const |

| void | setXSave (const struct kvm_xsave &xsave) |

| void | getVCpuEvents (struct kvm_vcpu_events &events) const |

| void | setVCpuEvents (const struct kvm_vcpu_events &events) |

Protected Member Functions inherited from gem5::BaseKvmCPU Protected Member Functions inherited from gem5::BaseKvmCPU | |

| void | tick () |

| Execute the CPU until the next event in the main event queue or until the guest needs service from gem5. More... | |

| struct kvm_run * | getKvmRunState () |

| Get a pointer to the kvm_run structure containing all the input and output parameters from kvmRun(). More... | |

| uint8_t * | getGuestData (uint64_t offset) const |

| Retrieve a pointer to guest data stored at the end of the kvm_run structure. More... | |

| void | kvmNonMaskableInterrupt () |

| Send a non-maskable interrupt to the guest. More... | |

| void | kvmInterrupt (const struct kvm_interrupt &interrupt) |

| Send a normal interrupt to the guest. More... | |

| std::string | getAndFormatOneReg (uint64_t id) const |

| Get and format one register for printout. More... | |

| Tick | doMMIOAccess (Addr paddr, void *data, int size, bool write) |

| Inject a memory mapped IO request into gem5. More... | |

| int | ioctl (int request, long p1) const |

| vCPU ioctl interface. More... | |

| int | ioctl (int request, void *p1) const |

| int | ioctl (int request) const |

| void | getRegisters (struct kvm_regs ®s) const |

| Get/Set the register state of the guest vCPU. More... | |

| void | setRegisters (const struct kvm_regs ®s) |

| void | getSpecialRegisters (struct kvm_sregs ®s) const |

| void | setSpecialRegisters (const struct kvm_sregs ®s) |

| void | getFPUState (struct kvm_fpu &state) const |

| Get/Set the guest FPU/vector state. More... | |

| void | setFPUState (const struct kvm_fpu &state) |

| void | setOneReg (uint64_t id, const void *addr) |

| Get/Set single register using the KVM_(SET|GET)_ONE_REG API. More... | |

| void | setOneReg (uint64_t id, uint64_t value) |

| void | setOneReg (uint64_t id, uint32_t value) |

| void | getOneReg (uint64_t id, void *addr) const |

| uint64_t | getOneRegU64 (uint64_t id) const |

| uint32_t | getOneRegU32 (uint64_t id) const |

| void | syncThreadContext () |

| Update a thread context if the KVM state is dirty with respect to the cached thread context. More... | |

| EventQueue * | deviceEventQueue () |

| Get a pointer to the event queue owning devices. More... | |

| void | syncKvmState () |

| Update the KVM if the thread context is dirty. More... | |

| virtual Tick | handleKvmExit () |

| Main kvmRun exit handler, calls the relevant handleKvmExit* depending on exit type. More... | |

| virtual Tick | handleKvmExitHypercall () |

| The guest requested a monitor service using a hypercall. More... | |

| virtual Tick | handleKvmExitUnknown () |

| An unknown architecture dependent error occurred when starting the vCPU. More... | |

| virtual Tick | handleKvmExitException () |

| An unhandled virtualization exception occured. More... | |

| virtual Tick | handleKvmExitFailEntry () |

| KVM failed to start the virtualized CPU. More... | |

| void | setSignalMask (const sigset_t *mask) |

| Set the signal mask used in kvmRun() More... | |

Protected Member Functions inherited from gem5::BaseCPU Protected Member Functions inherited from gem5::BaseCPU | |

| void | updateCycleCounters (CPUState state) |

| base method keeping track of cycle progression More... | |

| void | enterPwrGating () |

| probing::PMUUPtr | pmuProbePoint (const char *name) |

| Helper method to instantiate probe points belonging to this object. More... | |

Protected Member Functions inherited from gem5::Drainable Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from gem5::Clocked Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. More... | |

Private Member Functions | |

| void | updateCPUID () |

| Transfer gem5's CPUID values into the virtual CPU. More... | |

| void | handleIOMiscReg32 (int miscreg) |

| Handle a 32-bit IO access that should be mapped to a MiscReg. More... | |

| void | updateKvmStateRegs () |

| Support routines to update the state of the KVM CPU from gem5's state representation. More... | |

| void | updateKvmStateSRegs () |

| Update control registers (CRx, segments, etc.) More... | |

| void | updateKvmStateFPU () |

| Update FPU and SIMD registers. More... | |

| void | updateKvmStateFPULegacy () |

| Update FPU and SIMD registers using the legacy API. More... | |

| void | updateKvmStateFPUXSave () |

| Update FPU and SIMD registers using the XSave API. More... | |

| void | updateKvmStateMSRs () |

| Update MSR registers. More... | |

| void | updateThreadContextRegs (const struct kvm_regs ®s, const struct kvm_sregs &sregs) |

| Support routines to update the state of gem5's thread context from KVM's state representation. More... | |

| void | updateThreadContextSRegs (const struct kvm_sregs &sregs) |

| Update control registers (CRx, segments, etc.) More... | |

| void | updateThreadContextFPU (const struct kvm_fpu &fpu) |

| Update FPU and SIMD registers using the legacy API. More... | |

| void | updateThreadContextXSave (const struct kvm_xsave &kxsave) |

| Update FPU and SIMD registers using the XSave API. More... | |

| void | updateThreadContextMSRs () |

| Update MSR registers. More... | |

Private Attributes | |

| Kvm::MSRIndexVector | cachedMsrIntersection |

| Cached intersection of supported MSRs. More... | |

| bool | haveDebugRegs |

| Kvm::capDebugRegs() available? More... | |

| bool | haveXSave |

| Kvm::capXSave() available? More... | |

| bool | useXSave |

| Should the XSave interface be used to sync the FPU and SIMD registers? More... | |

| bool | haveXCRs |

| Kvm::capXCRs() available? More... | |

Additional Inherited Members | |

Public Types inherited from gem5::ClockedObject Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. More... | |

Public Types inherited from gem5::SimObject Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Static Public Member Functions inherited from gem5::BaseCPU Static Public Member Functions inherited from gem5::BaseCPU | |

| static int | numSimulatedCPUs () |

| static Counter | numSimulatedInsts () |

| static Counter | numSimulatedOps () |

Static Public Member Functions inherited from gem5::SimObject Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. More... | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. More... | |

Static Public Member Functions inherited from gem5::Serializable Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. More... | |

Public Attributes inherited from gem5::BaseKvmCPU Public Attributes inherited from gem5::BaseKvmCPU | |

| SimpleThread * | thread |

| A cached copy of a thread's state in the form of a SimpleThread object. More... | |

| ThreadContext * | tc |

| ThreadContext object, provides an interface for external objects to modify this thread's state. More... | |

| KvmVM * | vm |

| gem5::BaseKvmCPU::StatGroup | stats |

| Counter | ctrInsts |

| Number of instructions executed by the CPU. More... | |

Public Attributes inherited from gem5::BaseCPU Public Attributes inherited from gem5::BaseCPU | |

| ThreadID | numThreads |

| Number of threads we're actually simulating (<= SMT_MAX_THREADS). More... | |

| System * | system |

| gem5::BaseCPU::BaseCPUStats | baseStats |

| Cycles | syscallRetryLatency |

| std::vector< std::unique_ptr< FetchCPUStats > > | fetchStats |

| std::vector< std::unique_ptr< ExecuteCPUStats > > | executeStats |

| std::vector< std::unique_ptr< CommitCPUStats > > | commitStats |

Public Attributes inherited from gem5::ClockedObject Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Static Public Attributes inherited from gem5::BaseCPU Static Public Attributes inherited from gem5::BaseCPU | |

| static const uint32_t | invldPid = std::numeric_limits<uint32_t>::max() |

| Invalid or unknown Pid. More... | |

Protected Attributes inherited from gem5::BaseKvmCPU Protected Attributes inherited from gem5::BaseKvmCPU | |

| Status | _status |

| CPU run state. More... | |

| KVMCpuPort | dataPort |

| Port for data requests. More... | |

| KVMCpuPort | instPort |

| Unused dummy port for the instruction interface. More... | |

| const bool | alwaysSyncTC |

| Be conservative and always synchronize the thread context on KVM entry/exit. More... | |

| bool | threadContextDirty |

| Is the gem5 context dirty? Set to true to force an update of the KVM vCPU state upon the next call to kvmRun(). More... | |

| bool | kvmStateDirty |

| Is the KVM state dirty? Set to true to force an update of the KVM vCPU state upon the next call to kvmRun(). More... | |

| long | vcpuID |

| KVM internal ID of the vCPU. More... | |

| pthread_t | vcpuThread |

| ID of the vCPU thread. More... | |

Protected Attributes inherited from gem5::BaseCPU Protected Attributes inherited from gem5::BaseCPU | |

| Tick | instCnt |

| Instruction count used for SPARC misc register. More... | |

| int | _cpuId |

| const uint32_t | _socketId |

| Each cpu will have a socket ID that corresponds to its physical location in the system. More... | |

| RequestorID | _instRequestorId |

| instruction side request id that must be placed in all requests More... | |

| RequestorID | _dataRequestorId |

| data side request id that must be placed in all requests More... | |

| uint32_t | _taskId |

| An intrenal representation of a task identifier within gem5. More... | |

| uint32_t | _pid |

| The current OS process ID that is executing on this processor. More... | |

| bool | _switchedOut |

| Is the CPU switched out or active? More... | |

| const unsigned int | _cacheLineSize |

| Cache the cache line size that we get from the system. More... | |

| SignalSinkPort< bool > | modelResetPort |

| std::vector< BaseInterrupts * > | interrupts |

| std::vector< ThreadContext * > | threadContexts |

| trace::InstTracer * | tracer |

| Cycles | previousCycle |

| CPUState | previousState |

| const Cycles | pwrGatingLatency |

| const bool | powerGatingOnIdle |

| EventFunctionWrapper | enterPwrGatingEvent |

| probing::PMUUPtr | ppRetiredInsts |

| Instruction commit probe point. More... | |

| probing::PMUUPtr | ppRetiredInstsPC |

| probing::PMUUPtr | ppRetiredLoads |

| Retired load instructions. More... | |

| probing::PMUUPtr | ppRetiredStores |

| Retired store instructions. More... | |

| probing::PMUUPtr | ppRetiredBranches |

| Retired branches (any type) More... | |

| probing::PMUUPtr | ppAllCycles |

| CPU cycle counter even if any thread Context is suspended. More... | |

| probing::PMUUPtr | ppActiveCycles |

| CPU cycle counter, only counts if any thread contexts is active. More... | |

| ProbePointArg< bool > * | ppSleeping |

| ProbePoint that signals transitions of threadContexts sets. More... | |

Protected Attributes inherited from gem5::SimObject Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from gem5::EventManager Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

Static Protected Attributes inherited from gem5::BaseCPU Static Protected Attributes inherited from gem5::BaseCPU | |

| static std::unique_ptr< GlobalStats > | globalStats |

| Pointer to the global stat structure. More... | |

Detailed Description

x86 implementation of a KVM-based hardware virtualized CPU.

Definition at line 52 of file x86_cpu.hh.

Member Typedef Documentation

◆ KvmMSRVector

|

protected |

Definition at line 74 of file x86_cpu.hh.

Constructor & Destructor Documentation

◆ X86KvmCPU()

| gem5::X86KvmCPU::X86KvmCPU | ( | const X86KvmCPUParams & | params | ) |

Definition at line 537 of file x86_cpu.cc.

◆ ~X86KvmCPU()

|

virtual |

Definition at line 571 of file x86_cpu.cc.

Member Function Documentation

◆ archIsDrained()

|

overrideprotectedvirtual |

Check if there are pending events in the vCPU that prevents it from being drained.

There are cases after interrupt injection where the interrupt is still pending in the guest. This method detects such cases and requests additional draining.

- Returns

- False if there are pending events in the guest, True otherwise.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1375 of file x86_cpu.cc.

References DPRINTF, and getVCpuEvents().

Referenced by kvmRunDrain().

◆ deliverInterrupts()

|

protected |

Inject pending interrupts from gem5 into the virtual CPU.

Definition at line 1145 of file x86_cpu.cc.

References DPRINTF, gem5::EventManager::eventQueue(), gem5::X86ISA::X86FaultBase::getVector(), gem5::BaseCPU::interrupts, gem5::BaseKvmCPU::kvmInterrupt(), gem5::BaseKvmCPU::kvmNonMaskableInterrupt(), panic, gem5::SimpleThread::suspend(), gem5::BaseKvmCPU::syncThreadContext(), gem5::BaseKvmCPU::tc, gem5::BaseKvmCPU::thread, gem5::BaseKvmCPU::threadContextDirty, and updateKvmState().

Referenced by kvmRun().

◆ dump()

|

overridevirtual |

Dump the internal state to the terminal.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 590 of file x86_cpu.cc.

References dumpDebugRegs(), dumpFpuRegs(), dumpIntRegs(), dumpMSRs(), dumpSpecRegs(), dumpVCpuEvents(), dumpXCRs(), dumpXSave(), and useXSave.

Referenced by updateKvmState(), and updateThreadContext().

◆ dumpDebugRegs()

| void gem5::X86KvmCPU::dumpDebugRegs | ( | ) | const |

Definition at line 629 of file x86_cpu.cc.

References gem5::dumpKvm(), getDebugRegisters(), haveDebugRegs, and inform.

Referenced by dump().

◆ dumpFpuRegs()

| void gem5::X86KvmCPU::dumpFpuRegs | ( | ) | const |

Definition at line 605 of file x86_cpu.cc.

References gem5::dumpKvm(), and gem5::BaseKvmCPU::getFPUState().

Referenced by dump().

◆ dumpIntRegs()

| void gem5::X86KvmCPU::dumpIntRegs | ( | ) | const |

Definition at line 613 of file x86_cpu.cc.

References gem5::dumpKvm(), and gem5::BaseKvmCPU::getRegisters().

Referenced by dump().

◆ dumpMSRs()

| void gem5::X86KvmCPU::dumpMSRs | ( | ) | const |

Definition at line 675 of file x86_cpu.cc.

References gem5::dumpKvm(), gem5::ArmISA::e, getMSRs(), gem5::ArmISA::i, gem5::KvmVM::kvm, and gem5::BaseKvmCPU::vm.

Referenced by dump().

◆ dumpSpecRegs()

| void gem5::X86KvmCPU::dumpSpecRegs | ( | ) | const |

Definition at line 621 of file x86_cpu.cc.

References gem5::dumpKvm(), and gem5::BaseKvmCPU::getSpecialRegisters().

Referenced by dump().

◆ dumpVCpuEvents()

| void gem5::X86KvmCPU::dumpVCpuEvents | ( | ) | const |

Definition at line 667 of file x86_cpu.cc.

References gem5::dumpKvm(), and getVCpuEvents().

Referenced by dump().

◆ dumpXCRs()

| void gem5::X86KvmCPU::dumpXCRs | ( | ) | const |

Definition at line 643 of file x86_cpu.cc.

References gem5::dumpKvm(), getXCRs(), haveXCRs, and inform.

Referenced by dump().

◆ dumpXSave()

| void gem5::X86KvmCPU::dumpXSave | ( | ) | const |

Definition at line 655 of file x86_cpu.cc.

References gem5::dumpKvm(), getXSave(), haveXSave, and inform.

Referenced by dump().

◆ getDebugRegisters()

|

protected |

Wrappers around KVM's state transfer methods.

Definition at line 1572 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpDebugRegs().

◆ getHostCycles()

|

overrideprotectedvirtual |

Get the value of the hardware cycle counter in the guest.

This method is supposed to return the total number of cycles executed in hardware mode relative to some arbitrary point in the past. It's mainly used when estimating the number of cycles actually executed by the CPU in kvmRun(). The default behavior of this method is to use the cycles performance counter, but some architectures may want to use internal registers instead.

- Returns

- Number of host cycles executed relative to an undefined point in the past.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1271 of file x86_cpu.cc.

◆ getMSR()

|

protected |

Definition at line 1536 of file x86_cpu.cc.

References getMSRs(), and gem5::MipsISA::index.

Referenced by getHostCycles().

◆ getMsrIntersection()

|

protected |

Get a list of MSRs supported by both gem5 and KVM.

- Note

- This method uses an internal cache and only generates the MSR list once.

- Returns

- reference to a list of msr indices

Definition at line 1551 of file x86_cpu.cc.

References cachedMsrIntersection, DPRINTF, gem5::SimObject::find(), gem5::KvmVM::kvm, gem5::X86ISA::msrMap, gem5::BaseKvmCPU::vm, and warn.

Referenced by updateKvmStateMSRs(), and updateThreadContextMSRs().

◆ getMSRs()

|

protected |

Definition at line 1513 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpMSRs(), getMSR(), and updateThreadContextMSRs().

◆ getVCpuEvents()

|

protected |

Definition at line 1623 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by archIsDrained(), and dumpVCpuEvents().

◆ getXCRs()

|

protected |

Definition at line 1594 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpXCRs().

◆ getXSave()

|

protected |

Definition at line 1608 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by dumpXSave(), and updateThreadContext().

◆ handleIOMiscReg32()

|

private |

Handle a 32-bit IO access that should be mapped to a MiscReg.

- Note

- This method can only be called on when handling IO after a KVM_EXIT_IO.

- Parameters

-

miscreg Register to map the current IO access to.

Definition at line 1277 of file x86_cpu.cc.

References data, gem5::BaseKvmCPU::getGuestData(), gem5::BaseKvmCPU::getKvmRunState(), panic, gem5::ThreadContext::readMiscRegNoEffect(), gem5::ThreadContext::setMiscReg(), and gem5::BaseKvmCPU::tc.

Referenced by handleKvmExitIO().

◆ handleKvmExitIO()

|

overrideprotectedvirtual |

Handle x86 legacy IO (in/out)

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1302 of file x86_cpu.cc.

References gem5::ThreadContext::contextId(), gem5::X86ISA::count, gem5::BaseKvmCPU::dataPort, gem5::BaseCPU::dataRequestorId(), gem5::Packet::dataStatic(), gem5::BaseKvmCPU::deviceEventQueue(), DPRINTF, gem5::BaseKvmCPU::getGuestData(), gem5::BaseKvmCPU::getKvmRunState(), handleIOMiscReg32(), gem5::ArmISA::i, IO_PCI_CONF_ADDR, IO_PCI_CONF_DATA_BASE, gem5::X86ISA::misc_reg::PciConfigAddress, gem5::ThreadContext::readMiscRegNoEffect(), gem5::MemCmd::ReadReq, gem5::BaseKvmCPU::KVMCpuPort::submitIO(), gem5::BaseKvmCPU::tc, gem5::Request::UNCACHEABLE, gem5::MemCmd::WriteReq, gem5::X86ISA::x86IOAddress(), and gem5::X86ISA::x86PciConfigAddress().

◆ handleKvmExitIRQWindowOpen()

|

overrideprotectedvirtual |

The guest exited because an interrupt window was requested.

The guest exited because an interrupt window was requested (request_interrupt_window in the kvm_run structure was set to 1 before calling kvmRun) and it is now ready to receive

- Returns

- Number of ticks spent servicing the IRQ

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1366 of file x86_cpu.cc.

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Definition at line 543 of file x86_cpu.cc.

References gem5::Kvm::capDebugRegs(), gem5::Kvm::capExtendedCPUID(), gem5::Kvm::capSetTSSAddress(), gem5::Kvm::capUserNMI(), gem5::Kvm::capVCPUEvents(), gem5::Kvm::capXCRs(), gem5::Kvm::capXSave(), haveDebugRegs, haveXCRs, haveXSave, gem5::BaseKvmCPU::init(), gem5::KvmVM::kvm, panic, useXSave, gem5::BaseKvmCPU::vm, and warn.

◆ ioctlRun()

|

overrideprotectedvirtual |

Override for synchronizing state in kvm_run.

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1404 of file x86_cpu.cc.

References gem5::X86ISA::misc_reg::ApicBase, gem5::X86ISA::misc_reg::Cr8, gem5::BaseKvmCPU::getKvmRunState(), gem5::BaseKvmCPU::ioctlRun(), gem5::ThreadContext::readMiscReg(), gem5::ThreadContext::setMiscReg(), and gem5::BaseKvmCPU::tc.

◆ kvmRun()

Request KVM to run the guest for a given number of ticks.

The method returns the approximate number of ticks executed.

- Note

- The returned number of ticks can be both larger or smaller than the requested number of ticks. A smaller number can, for example, occur when the guest executes MMIO. A larger number is typically due to performance counter inaccuracies.

- This method is virtual in order to allow implementations to check for architecture specific events (e.g., interrupts) before entering the VM.

- It is the response of the caller (normally tick()) to make sure that the KVM state is synchronized and that the TC is invalidated after entering KVM.

- This method does not normally cause any state transitions. However, if it may suspend the CPU by suspending the thread, which leads to a transition to the Idle state. In such a case, kvm must not be entered.

- Parameters

-

ticks Number of ticks to execute, set to 0 to exit immediately after finishing pending operations.

- Returns

- Number of ticks executed (see note)

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1198 of file x86_cpu.cc.

References gem5::BaseKvmCPU::_status, deliverInterrupts(), DPRINTF, gem5::BaseKvmCPU::getKvmRunState(), gem5::BaseKvmCPU::Idle, gem5::BaseCPU::interrupts, gem5::BaseKvmCPU::kvmRun(), and gem5::BaseKvmCPU::syncThreadContext().

◆ kvmRunDrain()

|

overrideprotectedvirtual |

Run the virtual CPU until draining completes.

In addition to the base functionality provided by BaseKvmCPU::kvmRunDrain(), this method handles x86-specific cases where there are pending interrupt events in the virtual CPU. These are handled by requesting an interrupt window if interrupts are pending (causing the vCPU to execute until interrupts can be delivered again).

- Returns

- Number of ticks executed

Reimplemented from gem5::BaseKvmCPU.

Definition at line 1246 of file x86_cpu.cc.

References archIsDrained(), DPRINTF, gem5::BaseKvmCPU::getKvmRunState(), gem5::BaseKvmCPU::kvmRun(), and gem5::sim_clock::as_float::ms.

◆ setCPUID() [1/2]

|

protected |

Definition at line 1481 of file x86_cpu.cc.

References gem5::MipsISA::cpuid, and setCPUID().

◆ setCPUID() [2/2]

|

protected |

Methods to access CPUID information using the extended API.

Only available if Kvm::capExtendedCPUID() is true.

Definition at line 1473 of file x86_cpu.cc.

References gem5::MipsISA::cpuid, gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by setCPUID(), and updateCPUID().

◆ setDebugRegisters()

|

protected |

Definition at line 1583 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

◆ setMSR()

|

protected |

Definition at line 1522 of file x86_cpu.cc.

References gem5::MipsISA::index, and setMSRs().

◆ setMSRs() [1/2]

|

protected |

Definition at line 1501 of file x86_cpu.cc.

References setMSRs().

◆ setMSRs() [2/2]

|

protected |

Methods to access MSRs in the guest.

Definition at line 1493 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by setMSR(), setMSRs(), and updateKvmStateMSRs().

◆ setVCpuEvents()

|

protected |

Definition at line 1630 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

◆ setXCRs()

|

protected |

Definition at line 1601 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

◆ setXSave()

|

protected |

Definition at line 1615 of file x86_cpu.cc.

References gem5::BaseKvmCPU::ioctl(), and panic.

Referenced by updateKvmStateFPUXSave().

◆ startup()

|

overridevirtual |

startup() is the final initialization call before simulation.

All state is initialized (including unserialized state, if any, such as the curTick() value), so this is the appropriate place to schedule initial event(s) for objects that need them.

Reimplemented from gem5::SimObject.

Definition at line 576 of file x86_cpu.cc.

References gem5::BaseKvmCPU::startup(), and updateCPUID().

◆ stutterPC()

|

inlineoverrideprotectedvirtual |

Modify a PCStatePtr's value so that its next PC is the current PC.

This needs to be implemented in KVM base classes since modifying the next PC value is an ISA specific operation. This is only used in doMMIOAccess, for reasons explained in a comment there.

Implements gem5::BaseKvmCPU.

Definition at line 97 of file x86_cpu.hh.

References gem5::MipsISA::pc.

◆ updateCPUID()

|

private |

Transfer gem5's CPUID values into the virtual CPU.

Definition at line 1437 of file x86_cpu.cc.

References gem5::MipsISA::cpuid, gem5::X86ISA::doCpuid(), gem5::makeKvmCpuid(), gem5::X86ISA::CpuidResult::rax, setCPUID(), and gem5::BaseKvmCPU::tc.

Referenced by startup().

◆ updateKvmState()

|

overrideprotectedvirtual |

Update the KVM state from the current thread context.

The base CPU calls this method before starting the guest CPU when the contextDirty flag is set. The architecture dependent CPU implementation is expected to update all guest state (registers, special registers, and FPU state).

Implements gem5::BaseKvmCPU.

Definition at line 694 of file x86_cpu.cc.

References DPRINTF, dump(), updateKvmStateFPU(), updateKvmStateMSRs(), updateKvmStateRegs(), and updateKvmStateSRegs().

Referenced by deliverInterrupts().

◆ updateKvmStateFPU()

|

private |

Update FPU and SIMD registers.

This method uses the appropriate (depending on availability and user configuration) kernel API by calling updateKvmStateFPULegacy() or updateKvmStateFPUXSave().

Definition at line 921 of file x86_cpu.cc.

References updateKvmStateFPULegacy(), updateKvmStateFPUXSave(), and useXSave.

Referenced by updateKvmState().

◆ updateKvmStateFPULegacy()

|

private |

Update FPU and SIMD registers using the legacy API.

- Note

- This method should normally only be called by updateKvmStateFPU() which automatically chooses between available APIs.

Definition at line 872 of file x86_cpu.cc.

References gem5::X86ISA::misc_reg::Fioff, gem5::X86ISA::misc_reg::Fiseg, gem5::X86ISA::misc_reg::Fooff, gem5::X86ISA::misc_reg::Foseg, gem5::ThreadContext::readMiscRegNoEffect(), gem5::BaseKvmCPU::setFPUState(), gem5::BaseKvmCPU::tc, gem5::updateKvmStateFPUCommon(), and warn_once.

Referenced by updateKvmStateFPU().

◆ updateKvmStateFPUXSave()

|

private |

Update FPU and SIMD registers using the XSave API.

- Note

- This method should normally only be called by updateKvmStateFPU() which automatically chooses between available APIs.

Definition at line 896 of file x86_cpu.cc.

References gem5::X86ISA::misc_reg::Fioff, gem5::X86ISA::misc_reg::Fiseg, gem5::X86ISA::misc_reg::Fooff, gem5::X86ISA::misc_reg::Foseg, gem5::ThreadContext::readMiscRegNoEffect(), setXSave(), gem5::BaseKvmCPU::tc, gem5::updateKvmStateFPUCommon(), and warn_once.

Referenced by updateKvmStateFPU().

◆ updateKvmStateMSRs()

|

private |

Update MSR registers.

Definition at line 930 of file x86_cpu.cc.

References DPRINTF, gem5::ArmISA::e, getMsrIntersection(), gem5::X86ISA::msrMap, gem5::ThreadContext::readMiscReg(), setMSRs(), and gem5::BaseKvmCPU::tc.

Referenced by updateKvmState().

◆ updateKvmStateRegs()

|

private |

Support routines to update the state of the KVM CPU from gem5's state representation.

Update integer registers

Definition at line 707 of file x86_cpu.cc.

References gem5::X86ISA::misc_reg::CsBase, FOREACH_IREG, gem5::X86ISA::getRFlags(), gem5::PCStateBase::instAddr(), gem5::ThreadContext::pcState(), gem5::ThreadContext::readMiscReg(), gem5::BaseKvmCPU::setRegisters(), and gem5::BaseKvmCPU::tc.

Referenced by updateKvmState().

◆ updateKvmStateSRegs()

|

private |

Update control registers (CRx, segments, etc.)

Definition at line 769 of file x86_cpu.cc.

References gem5::forceSegAccessed(), FOREACH_DTABLE, FOREACH_SEGMENT, FOREACH_SREG, hack, gem5::ThreadContext::readMiscReg(), gem5::X86ISA::misc_reg::Rflags, SEG_CS_TYPE_ACCESSED, SEG_CS_TYPE_READ_ACCESSED, SEG_SYS_TYPE_TSS_AVAILABLE, SEG_SYS_TYPE_TSS_BUSY, gem5::BaseKvmCPU::setSpecialRegisters(), and gem5::BaseKvmCPU::tc.

Referenced by updateKvmState().

◆ updateThreadContext()

|

overrideprotectedvirtual |

Update the current thread context with the KVM state.

The base CPU after the guest updates any of the KVM state. In practice, this happens after kvmRun is called. The architecture dependent code is expected to read the state of the guest CPU and update gem5's thread state.

Implements gem5::BaseKvmCPU.

Definition at line 952 of file x86_cpu.cc.

References DPRINTF, dump(), gem5::BaseKvmCPU::getFPUState(), gem5::BaseKvmCPU::getRegisters(), gem5::BaseKvmCPU::getSpecialRegisters(), getXSave(), gem5::X86ISA::misc_reg::M5Reg, gem5::ThreadContext::setMiscReg(), gem5::BaseKvmCPU::tc, updateThreadContextFPU(), updateThreadContextMSRs(), updateThreadContextRegs(), updateThreadContextSRegs(), updateThreadContextXSave(), and useXSave.

◆ updateThreadContextFPU()

|

private |

Update FPU and SIMD registers using the legacy API.

Definition at line 1091 of file x86_cpu.cc.

References gem5::X86ISA::misc_reg::Fioff, gem5::X86ISA::misc_reg::Fiseg, gem5::X86ISA::misc_reg::Fooff, gem5::X86ISA::misc_reg::Foseg, gem5::ThreadContext::setMiscRegNoEffect(), gem5::BaseKvmCPU::tc, and gem5::updateThreadContextFPUCommon().

Referenced by updateThreadContext().

◆ updateThreadContextMSRs()

|

private |

Update MSR registers.

Definition at line 1115 of file x86_cpu.cc.

References gem5::ArmISA::at, DPRINTF, getMsrIntersection(), getMSRs(), gem5::ArmISA::i, gem5::X86ISA::msrMap, gem5::ThreadContext::setMiscReg(), and gem5::BaseKvmCPU::tc.

Referenced by updateThreadContext().

◆ updateThreadContextRegs()

|

private |

Support routines to update the state of gem5's thread context from KVM's state representation.

Update integer registers

Definition at line 986 of file x86_cpu.cc.

References FOREACH_IREG, gem5::ThreadContext::pcState(), gem5::X86ISA::setRFlags(), and gem5::BaseKvmCPU::tc.

Referenced by updateThreadContext().

◆ updateThreadContextSRegs()

|

private |

Update control registers (CRx, segments, etc.)

Definition at line 1040 of file x86_cpu.cc.

References FOREACH_DTABLE, FOREACH_SEGMENT, FOREACH_SREG, and gem5::BaseKvmCPU::getKvmRunState().

Referenced by updateThreadContext().

◆ updateThreadContextXSave()

|

private |

Update FPU and SIMD registers using the XSave API.

Definition at line 1102 of file x86_cpu.cc.

References gem5::FXSave::ctrl64, gem5::X86ISA::misc_reg::Fioff, gem5::X86ISA::misc_reg::Fiseg, gem5::X86ISA::misc_reg::Fooff, gem5::X86ISA::misc_reg::Foseg, gem5::ThreadContext::setMiscRegNoEffect(), gem5::BaseKvmCPU::tc, and gem5::updateThreadContextFPUCommon().

Referenced by updateThreadContext().

Member Data Documentation

◆ cachedMsrIntersection

|

mutableprivate |

Cached intersection of supported MSRs.

Definition at line 255 of file x86_cpu.hh.

Referenced by getMsrIntersection().

◆ haveDebugRegs

|

private |

Kvm::capDebugRegs() available?

Definition at line 259 of file x86_cpu.hh.

Referenced by dumpDebugRegs(), and init().

◆ haveXCRs

|

private |

Kvm::capXCRs() available?

Definition at line 268 of file x86_cpu.hh.

Referenced by dumpXCRs(), and init().

◆ haveXSave

|

private |

Kvm::capXSave() available?

Definition at line 261 of file x86_cpu.hh.

Referenced by dumpXSave(), and init().

◆ useXSave

|

private |

Should the XSave interface be used to sync the FPU and SIMD registers?

Definition at line 266 of file x86_cpu.hh.

Referenced by dump(), init(), updateKvmStateFPU(), and updateThreadContext().

The documentation for this class was generated from the following files:

- arch/x86/kvm/x86_cpu.hh

- arch/x86/kvm/x86_cpu.cc