#include <reg_bank.hh>

Classes | |

| class | Register |

| class | RegisterAdder |

| class | RegisterBase |

| class | RegisterBuf |

| class | RegisterLBuf |

| class | RegisterRao |

| class | RegisterRaz |

| class | RegisterRoFill |

Public Types | |

| using | Register8 = Register<uint8_t> |

| using | Register8LE = Register<uint8_t, ByteOrder::little> |

| using | Register8BE = Register<uint8_t, ByteOrder::big> |

| using | Register16 = Register<uint16_t> |

| using | Register16LE = Register<uint16_t, ByteOrder::little> |

| using | Register16BE = Register<uint16_t, ByteOrder::big> |

| using | Register32 = Register<uint32_t> |

| using | Register32LE = Register<uint32_t, ByteOrder::little> |

| using | Register32BE = Register<uint32_t, ByteOrder::big> |

| using | Register64 = Register<uint64_t> |

| using | Register64LE = Register<uint64_t, ByteOrder::little> |

| using | Register64BE = Register<uint64_t, ByteOrder::big> |

Public Member Functions | |

| void | setDebugFlag (const ::gem5::debug::SimpleFlag &flag) |

| constexpr | RegisterBank (const std::string &new_name, Addr new_base) |

| virtual | ~RegisterBank () |

| RegisterBank (RegisterBank &&)=default | |

| void | addRegisters (std::initializer_list< RegisterAdder > adders) |

| template<class FillerReg> | |

| void | addRegistersAt (std::initializer_list< RegisterAdder > adders) |

| void | addRegister (RegisterAdder reg) |

| Addr | base () const |

| Addr | size () const |

| const std::string & | name () const |

| virtual void | read (Addr addr, void *buf, Addr bytes) |

| virtual void | write (Addr addr, const void *buf, Addr bytes) |

| virtual void | reset () |

Static Public Member Functions | |

| template<typename Data> | |

| static constexpr Data | readWithMask (const Data &value, const Data &bitmask) |

| template<typename Data> | |

| static constexpr Data | writeWithMask (const Data &old, const Data &value, const Data &bitmask) |

Private Attributes | |

| std::map< Addr, std::reference_wrapper< RegisterBase > > | _offsetMap |

| const ::gem5::debug::SimpleFlag * | _debug_flag = nullptr |

| Addr | _base = 0 |

| Addr | _size = 0 |

| const std::string | _name |

| std::vector< std::unique_ptr< RegisterBase > > | owned |

Detailed Description

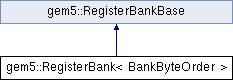

class gem5::RegisterBank< BankByteOrder >

Definition at line 356 of file reg_bank.hh.

Member Typedef Documentation

◆ Register16

| using gem5::RegisterBank< BankByteOrder >::Register16 = Register<uint16_t> |

Definition at line 919 of file reg_bank.hh.

◆ Register16BE

| using gem5::RegisterBank< BankByteOrder >::Register16BE = Register<uint16_t, ByteOrder::big> |

Definition at line 921 of file reg_bank.hh.

◆ Register16LE

| using gem5::RegisterBank< BankByteOrder >::Register16LE = Register<uint16_t, ByteOrder::little> |

Definition at line 920 of file reg_bank.hh.

◆ Register32

| using gem5::RegisterBank< BankByteOrder >::Register32 = Register<uint32_t> |

Definition at line 922 of file reg_bank.hh.

◆ Register32BE

| using gem5::RegisterBank< BankByteOrder >::Register32BE = Register<uint32_t, ByteOrder::big> |

Definition at line 924 of file reg_bank.hh.

◆ Register32LE

| using gem5::RegisterBank< BankByteOrder >::Register32LE = Register<uint32_t, ByteOrder::little> |

Definition at line 923 of file reg_bank.hh.

◆ Register64

| using gem5::RegisterBank< BankByteOrder >::Register64 = Register<uint64_t> |

Definition at line 925 of file reg_bank.hh.

◆ Register64BE

| using gem5::RegisterBank< BankByteOrder >::Register64BE = Register<uint64_t, ByteOrder::big> |

Definition at line 927 of file reg_bank.hh.

◆ Register64LE

| using gem5::RegisterBank< BankByteOrder >::Register64LE = Register<uint64_t, ByteOrder::little> |

Definition at line 926 of file reg_bank.hh.

◆ Register8

| using gem5::RegisterBank< BankByteOrder >::Register8 = Register<uint8_t> |

Definition at line 916 of file reg_bank.hh.

◆ Register8BE

| using gem5::RegisterBank< BankByteOrder >::Register8BE = Register<uint8_t, ByteOrder::big> |

Definition at line 918 of file reg_bank.hh.

◆ Register8LE

| using gem5::RegisterBank< BankByteOrder >::Register8LE = Register<uint8_t, ByteOrder::little> |

Definition at line 917 of file reg_bank.hh.

Constructor & Destructor Documentation

◆ RegisterBank() [1/2]

|

inlineconstexpr |

Definition at line 930 of file reg_bank.hh.

◆ ~RegisterBank()

|

inlinevirtual |

Definition at line 934 of file reg_bank.hh.

◆ RegisterBank() [2/2]

|

default |

Member Function Documentation

◆ addRegister()

|

inline |

Definition at line 1024 of file reg_bank.hh.

◆ addRegisters()

|

inline |

Definition at line 958 of file reg_bank.hh.

Referenced by gem5::RegisterBank< ByteOrder::little >::addRegister().

◆ addRegistersAt()

|

inline |

Definition at line 985 of file reg_bank.hh.

◆ base()

|

inline |

Definition at line 1026 of file reg_bank.hh.

Referenced by gem5::RegisterBank< ByteOrder::little >::read(), and gem5::RegisterBank< ByteOrder::little >::write().

◆ name()

|

inline |

◆ read()

|

inlinevirtual |

Definition at line 1031 of file reg_bank.hh.

◆ readWithMask()

|

inlinestaticconstexpr |

Definition at line 362 of file reg_bank.hh.

Referenced by gem5::RegisterBank< ByteOrder::little >::writeWithMask().

◆ reset()

|

inlinevirtual |

Definition at line 1121 of file reg_bank.hh.

◆ setDebugFlag()

|

inline |

Definition at line 900 of file reg_bank.hh.

◆ size()

|

inline |

Definition at line 1027 of file reg_bank.hh.

Referenced by gem5::RegisterBank< ByteOrder::little >::read(), and gem5::RegisterBank< ByteOrder::little >::write().

◆ write()

|

inlinevirtual |

Definition at line 1075 of file reg_bank.hh.

◆ writeWithMask()

|

inlinestaticconstexpr |

Definition at line 369 of file reg_bank.hh.

Referenced by gem5::RegisterBank< BankByteOrder >::Register< Data, RegByteOrder >::defaultPartialWriter(), gem5::RegisterBank< BankByteOrder >::Register< Data, RegByteOrder >::update(), and gem5::RegisterBank< BankByteOrder >::Register< Data, RegByteOrder >::update().

Member Data Documentation

◆ _base

|

private |

Definition at line 909 of file reg_bank.hh.

◆ _debug_flag

|

private |

Definition at line 908 of file reg_bank.hh.

◆ _name

|

private |

Definition at line 911 of file reg_bank.hh.

◆ _offsetMap

|

private |

Definition at line 906 of file reg_bank.hh.

◆ _size

|

private |

Definition at line 910 of file reg_bank.hh.

◆ owned

|

private |

Definition at line 912 of file reg_bank.hh.

The documentation for this class was generated from the following file:

- dev/reg_bank.hh

Generated on Sat Oct 18 2025 08:06:53 for gem5 by doxygen 1.14.0