A very simple cache object. More...

#include <simple_cache.hh>

Classes | |

| class | CPUSidePort |

| Port on the CPU-side that receives requests. More... | |

| class | MemSidePort |

| Port on the memory-side that receives responses. More... | |

| struct | SimpleCacheStats |

| Cache statistics. More... | |

Public Member Functions | |

| SimpleCache (SimpleCacheParams *params) | |

| constructor More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. More... | |

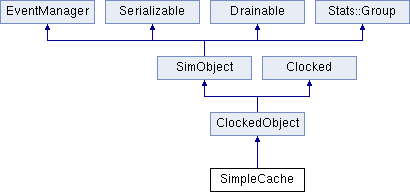

Public Member Functions inherited from ClockedObject Public Member Functions inherited from ClockedObject | |

| ClockedObject (const ClockedObjectParams *p) | |

| const Params * | params () const |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from SimObject Public Member Functions inherited from SimObject | |

| const Params * | params () const |

| SimObject (const Params *_params) | |

| virtual | ~SimObject () |

| virtual const std::string | name () const |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| virtual void | regProbePoints () |

| Register probe points for this object. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. More... | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from EventManager Public Member Functions inherited from EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. More... | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. More... | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from Drainable Public Member Functions inherited from Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Public Member Functions inherited from Stats::Group Public Member Functions inherited from Stats::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. More... | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. More... | |

| virtual void | resetStats () |

| Callback to reset stats. More... | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. More... | |

| void | addStat (Stats::Info *info) |

| Register a stat with this group. More... | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. More... | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. More... | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. More... | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. More... | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

Public Member Functions inherited from Clocked Public Member Functions inherited from Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Attributes | |

| SimpleCache::SimpleCacheStats | stats |

Protected Attributes inherited from SimObject Protected Attributes inherited from SimObject | |

| const SimObjectParams * | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from EventManager Protected Attributes inherited from EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

Private Member Functions | |

| bool | handleRequest (PacketPtr pkt, int port_id) |

| Handle the request from the CPU side. More... | |

| bool | handleResponse (PacketPtr pkt) |

| Handle the respone from the memory side. More... | |

| void | sendResponse (PacketPtr pkt) |

| Send the packet to the CPU side. More... | |

| void | handleFunctional (PacketPtr pkt) |

| Handle a packet functionally. More... | |

| void | accessTiming (PacketPtr pkt) |

| Access the cache for a timing access. More... | |

| bool | accessFunctional (PacketPtr pkt) |

| This is where we actually update / read from the cache. More... | |

| void | insert (PacketPtr pkt) |

| Insert a block into the cache. More... | |

| AddrRangeList | getAddrRanges () const |

| Return the address ranges this cache is responsible for. More... | |

| void | sendRangeChange () const |

| Tell the CPU side to ask for our memory ranges. More... | |

Private Attributes | |

| const Cycles | latency |

| Latency to check the cache. Number of cycles for both hit and miss. More... | |

| const unsigned | blockSize |

| The block size for the cache. More... | |

| const unsigned | capacity |

| Number of blocks in the cache (size of cache / block size) More... | |

| std::vector< CPUSidePort > | cpuPorts |

| Instantiation of the CPU-side port. More... | |

| MemSidePort | memPort |

| Instantiation of the memory-side port. More... | |

| bool | blocked |

| True if this cache is currently blocked waiting for a response. More... | |

| PacketPtr | originalPacket |

| Packet that we are currently handling. More... | |

| int | waitingPortId |

| The port to send the response when we recieve it back. More... | |

| Tick | missTime |

| For tracking the miss latency. More... | |

| std::unordered_map< Addr, uint8_t * > | cacheStore |

| An incredibly simple cache storage. Maps block addresses to data. More... | |

Additional Inherited Members | |

Public Types inherited from ClockedObject Public Types inherited from ClockedObject | |

| typedef ClockedObjectParams | Params |

| Parameters of ClockedObject. More... | |

Public Types inherited from SimObject Public Types inherited from SimObject | |

| typedef SimObjectParams | Params |

Static Public Member Functions inherited from SimObject Static Public Member Functions inherited from SimObject | |

| static void | serializeAll (CheckpointOut &cp) |

| Serialize all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| Serializes all the SimObjects. More... | |

| static void | unserializeGlobals (CheckpointIn &cp) |

Public Attributes inherited from ClockedObject Public Attributes inherited from ClockedObject | |

| PowerState * | powerState |

Protected Member Functions inherited from Drainable Protected Member Functions inherited from Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. More... | |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from Clocked Protected Member Functions inherited from Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. More... | |

Detailed Description

A very simple cache object.

Has a fully-associative data store with random replacement. This cache is fully blocking (not non-blocking). Only a single request can be outstanding at a time. This cache is a writeback cache.

Definition at line 46 of file simple_cache.hh.

Constructor & Destructor Documentation

◆ SimpleCache()

| SimpleCache::SimpleCache | ( | SimpleCacheParams * | params | ) |

constructor

Definition at line 35 of file simple_cache.cc.

References cpuPorts, csprintf(), ArmISA::i, SimObject::name(), and ClockedObject::params().

Member Function Documentation

◆ accessFunctional()

|

private |

This is where we actually update / read from the cache.

This function is executed on both timing and functional accesses.

- Returns

- true if a hit, false otherwise

Definition at line 339 of file simple_cache.cc.

References blockSize, cacheStore, Packet::getBlockAddr(), Packet::isRead(), Packet::isWrite(), panic, Packet::setDataFromBlock(), and Packet::writeDataToBlock().

Referenced by accessTiming(), handleFunctional(), and handleResponse().

◆ accessTiming()

|

private |

Access the cache for a timing access.

This is called after the cache access latency has already elapsed.

Definition at line 281 of file simple_cache.cc.

References accessFunctional(), addr, Packet::allocate(), blockSize, curTick(), DDUMP, DPRINTF, Packet::getAddr(), Packet::getBlockAddr(), Packet::getConstPtr(), Packet::getSize(), SimpleCache::SimpleCacheStats::hits, Packet::isRead(), Packet::isWrite(), Packet::makeResponse(), memPort, SimpleCache::SimpleCacheStats::misses, missTime, Packet::needsResponse(), originalPacket, panic, panic_if, Packet::print(), MemCmd::ReadReq, Packet::req, SimpleCache::MemSidePort::sendPacket(), sendResponse(), and stats.

Referenced by handleRequest().

◆ getAddrRanges()

|

private |

Return the address ranges this cache is responsible for.

Just use the same as the next upper level of the hierarchy.

- Returns

- the address ranges this cache is responsible for

Definition at line 410 of file simple_cache.cc.

References DPRINTF, RequestPort::getAddrRanges(), and memPort.

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from SimObject.

Definition at line 54 of file simple_cache.cc.

References cpuPorts, SimObject::getPort(), InvalidPortID, memPort, and panic_if.

◆ handleFunctional()

|

private |

Handle a packet functionally.

Update the data on a write and get the data on a read. Called from CPU port on a recv functional.

- Parameters

-

packet to functionally handle

Definition at line 271 of file simple_cache.cc.

References accessFunctional(), Packet::makeResponse(), memPort, and RequestPort::sendFunctional().

◆ handleRequest()

|

private |

Handle the request from the CPU side.

Called from the CPU port on a timing request.

- Parameters

-

requesting packet id of the port to send the response

- Returns

- true if we can handle the request this cycle, false if the requestor needs to retry later

Definition at line 191 of file simple_cache.cc.

References accessTiming(), blocked, Clocked::clockEdge(), DPRINTF, Packet::getAddr(), latency, SimObject::name(), EventManager::schedule(), and waitingPortId.

◆ handleResponse()

|

private |

Handle the respone from the memory side.

Called from the memory port on a timing response.

- Parameters

-

responding packet

- Returns

- true if we can handle the response this cycle, false if the responder needs to retry later

Definition at line 216 of file simple_cache.cc.

References accessFunctional(), blocked, curTick(), DPRINTF, Packet::getAddr(), insert(), Packet::makeResponse(), SimpleCache::SimpleCacheStats::missLatency, missTime, originalPacket, panic_if, Stats::DistBase< Derived, Stor >::sample(), sendResponse(), and stats.

◆ insert()

|

private |

Insert a block into the cache.

If there is no room left in the cache, then this function evicts a random entry t make room for the new block.

- Parameters

-

packet with the data (and address) to insert into the cache

Definition at line 359 of file simple_cache.cc.

References blockSize, cacheStore, capacity, data, Packet::dataDynamic(), DDUMP, DPRINTF, Packet::getAddr(), Packet::getBlockAddr(), Packet::getConstPtr(), Packet::isResponse(), memPort, Packet::print(), Random::random(), random_mt, SimpleCache::MemSidePort::sendPacket(), MemCmd::WritebackDirty, and Packet::writeDataToBlock().

Referenced by handleResponse().

◆ sendRangeChange()

|

private |

Tell the CPU side to ask for our memory ranges.

Definition at line 418 of file simple_cache.cc.

References cpuPorts.

◆ sendResponse()

|

private |

Send the packet to the CPU side.

This function assumes the pkt is already a response packet and forwards it to the correct port. This function also unblocks this object and cleans up the whole request.

- Parameters

-

the packet to send to the cpu side

Definition at line 246 of file simple_cache.cc.

References blocked, cpuPorts, DPRINTF, Packet::getAddr(), and waitingPortId.

Referenced by accessTiming(), and handleResponse().

Member Data Documentation

◆ blocked

|

private |

True if this cache is currently blocked waiting for a response.

Definition at line 279 of file simple_cache.hh.

Referenced by handleRequest(), handleResponse(), and sendResponse().

◆ blockSize

|

private |

The block size for the cache.

Definition at line 267 of file simple_cache.hh.

Referenced by accessFunctional(), accessTiming(), and insert().

◆ cacheStore

|

private |

An incredibly simple cache storage. Maps block addresses to data.

Definition at line 292 of file simple_cache.hh.

Referenced by accessFunctional(), and insert().

◆ capacity

|

private |

Number of blocks in the cache (size of cache / block size)

Definition at line 270 of file simple_cache.hh.

Referenced by insert().

◆ cpuPorts

|

private |

Instantiation of the CPU-side port.

Definition at line 273 of file simple_cache.hh.

Referenced by getPort(), sendRangeChange(), sendResponse(), and SimpleCache().

◆ latency

|

private |

Latency to check the cache. Number of cycles for both hit and miss.

Definition at line 264 of file simple_cache.hh.

Referenced by handleRequest().

◆ memPort

|

private |

Instantiation of the memory-side port.

Definition at line 276 of file simple_cache.hh.

Referenced by accessTiming(), getAddrRanges(), getPort(), handleFunctional(), and insert().

◆ missTime

|

private |

For tracking the miss latency.

Definition at line 289 of file simple_cache.hh.

Referenced by accessTiming(), and handleResponse().

◆ originalPacket

|

private |

Packet that we are currently handling.

Used for upgrading to larger cache line sizes

Definition at line 283 of file simple_cache.hh.

Referenced by accessTiming(), and handleResponse().

◆ stats

|

protected |

Referenced by accessTiming(), and handleResponse().

◆ waitingPortId

|

private |

The port to send the response when we recieve it back.

Definition at line 286 of file simple_cache.hh.

Referenced by handleRequest(), and sendResponse().

The documentation for this class was generated from the following files:

- learning_gem5/part2/simple_cache.hh

- learning_gem5/part2/simple_cache.cc