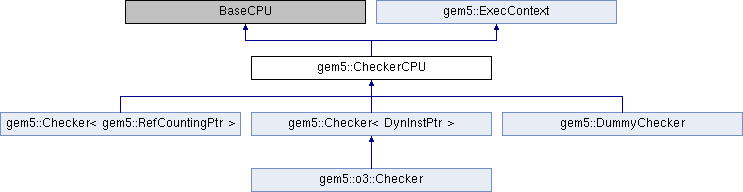

CheckerCPU class. More...

#include <cpu.hh>

Public Member Functions | |

| void | init () override |

| PARAMS (CheckerCPU) | |

| CheckerCPU (const Params &p) | |

| virtual | ~CheckerCPU () |

| void | setSystem (System *system) |

| void | setIcachePort (RequestPort *icache_port) |

| void | setDcachePort (RequestPort *dcache_port) |

| Port & | getDataPort () override |

| Port & | getInstPort () override |

| BaseMMU * | getMMUPtr () |

| virtual Counter | totalInsts () const override |

| virtual Counter | totalOps () const override |

| void | serialize (CheckpointOut &cp) const override |

| void | unserialize (CheckpointIn &cp) override |

| RegVal | getRegOperand (const StaticInst *si, int idx) override |

| void | getRegOperand (const StaticInst *si, int idx, void *val) override |

| void * | getWritableRegOperand (const StaticInst *si, int idx) override |

| void | setRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setRegOperand (const StaticInst *si, int idx, const void *val) override |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| Fault | initiateMemMgmtCmd (Request::Flags flags) override |

| Initiate a memory management command with no valid address. More... | |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| const PCStateBase & | pcState () const override |

| void | pcState (const PCStateBase &val) override |

| RegVal | readMiscRegNoEffect (int misc_reg) const |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a miscellaneous register, handling any architectural side effects due to reading that register. More... | |

| void | setMiscRegNoEffect (int misc_reg, RegVal val) |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a miscellaneous register, handling any architectural side effects due to writing that register. More... | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | recordPCChange (const PCStateBase &val) |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. More... | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| RequestPtr | genMemFragmentRequest (Addr frag_addr, int size, Request::Flags flags, const std::vector< bool > &byte_enable, int &frag_size, int &size_left) const |

| Helper function used to generate the request for a single fragment of a memory access. More... | |

| Fault | readMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable) override |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable) override |

| Fault | amoMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. More... | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. More... | |

| void | wakeup (ThreadID tid) override |

| void | handleError () |

| bool | checkFlags (const RequestPtr &unverified_req, Addr vAddr, Addr pAddr, int flags) |

| Checks if the flags set by the Checker and Checkee match. More... | |

| void | dumpAndExit () |

| ThreadContext * | tcBase () const override |

| Returns a pointer to the ThreadContext. More... | |

| SimpleThread * | threadBase () |

Public Member Functions inherited from gem5::ExecContext Public Member Functions inherited from gem5::ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Perform an atomic memory read operation. More... | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Initiate a timing memory read operation. More... | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable)=0 |

| For atomic-mode contexts, perform an atomic memory write operation. More... | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More... | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More... | |

Public Attributes | |

| SimpleThread * | thread |

| Counter | numLoad |

| Counter | startNumLoad |

| InstResult | unverifiedResult |

| RequestPtr | unverifiedReq |

| uint8_t * | unverifiedMemData |

| bool | changedPC |

| bool | willChangePC |

| std::unique_ptr< PCStateBase > | newPCState |

| bool | exitOnError |

| bool | updateOnError |

| bool | warnOnlyOnLoadError |

| InstSeqNum | youngestSN |

Protected Attributes | |

| RequestorID | requestorId |

| id attached to all issued requests More... | |

| std::vector< Process * > | workload |

| System * | systemPtr |

| RequestPort * | icachePort |

| RequestPort * | dcachePort |

| ThreadContext * | tc |

| BaseMMU * | mmu |

| std::queue< InstResult > | result |

| StaticInstPtr | curStaticInst |

| StaticInstPtr | curMacroStaticInst |

| Counter | numInst |

| Counter | startNumInst |

| std::queue< int > | miscRegIdxs |

Detailed Description

CheckerCPU class.

Dynamically verifies instructions as they are completed by making sure that the instruction and its results match the independent execution of the benchmark inside the checker. The checker verifies instructions in order, regardless of the order in which instructions complete. There are certain results that can not be verified, specifically the result of a store conditional or the values of uncached accesses. In these cases, and with instructions marked as "IsUnverifiable", the checker assumes that the value from the main CPU's execution is correct and simply copies that value. It provides a CheckerThreadContext (see checker/thread_context.hh) that provides hooks for updating the Checker's state through any ThreadContext accesses. This allows the checker to be able to correctly verify instructions, even with external accesses to the ThreadContext that change state.

Constructor & Destructor Documentation

◆ CheckerCPU()

| gem5::CheckerCPU::CheckerCPU | ( | const Params & | p | ) |

Definition at line 65 of file cpu.cc.

References changedPC, curMacroStaticInst, curStaticInst, exitOnError, mmu, numInst, numLoad, gem5::VegaISA::p, startNumInst, startNumLoad, updateOnError, warnOnlyOnLoadError, willChangePC, workload, and youngestSN.

◆ ~CheckerCPU()

Member Function Documentation

◆ amoMem()

|

inlineoverride |

◆ armMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

◆ checkFlags()

| bool gem5::CheckerCPU::checkFlags | ( | const RequestPtr & | unverified_req, |

| Addr | vAddr, | ||

| Addr | pAddr, | ||

| int | flags | ||

| ) |

◆ demapPage()

|

inlineoverridevirtual |

Invalidate a page in the DTLB and ITLB.

Implements gem5::ExecContext.

Definition at line 341 of file cpu.hh.

References gem5::BaseMMU::demapPage(), mmu, and gem5::MipsISA::vaddr.

◆ dumpAndExit()

| void gem5::CheckerCPU::dumpAndExit | ( | ) |

Definition at line 373 of file cpu.cc.

References gem5::curTick(), panic, gem5::SimpleThread::pcState(), thread, and warn.

Referenced by gem5::Checker< gem5::RefCountingPtr >::dumpAndExit(), handleError(), and gem5::Checker< gem5::RefCountingPtr >::handleError().

◆ genMemFragmentRequest()

| RequestPtr gem5::CheckerCPU::genMemFragmentRequest | ( | Addr | frag_addr, |

| int | size, | ||

| Request::Flags | flags, | ||

| const std::vector< bool > & | byte_enable, | ||

| int & | frag_size, | ||

| int & | size_left | ||

| ) | const |

Helper function used to generate the request for a single fragment of a memory access.

Takes care of setting up the appropriate byte-enable mask for the fragment, given the mask for the entire memory access.

- Parameters

-

frag_addr Start address of the fragment. size Total size of the memory access in bytes. flags Request flags. byte_enable Byte-enable mask for the entire memory access. [out] frag_size Fragment size. [in,out] size_left Size left to be processed in the memory access.

- Returns

- Pointer to the allocated Request, nullptr if the byte-enable mask is all-false for the fragment.

Definition at line 140 of file cpu.cc.

References gem5::addrBlockOffset(), gem5::ThreadContext::contextId(), flags, gem5::PCStateBase::instAddr(), gem5::isAnyActiveElement(), gem5::SimpleThread::pcState(), requestorId, tc, and thread.

Referenced by readMem(), and writeMem().

◆ getAddrMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

◆ getDataPort()

|

inlineoverride |

Definition at line 104 of file cpu.hh.

References dcachePort.

◆ getHtmTransactionalDepth()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 265 of file cpu.hh.

References gem5::SimpleThread::htmTransactionStarts, gem5::SimpleThread::htmTransactionStops, and thread.

Referenced by inHtmTransactionalState().

◆ getHtmTransactionUid()

|

inlineoverridevirtual |

◆ getInstPort()

|

inlineoverride |

Definition at line 113 of file cpu.hh.

References icachePort.

◆ getMMUPtr()

|

inline |

◆ getRegOperand() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 177 of file cpu.hh.

References gem5::SimpleThread::getReg(), gem5::InvalidRegClass, gem5::MipsISA::is, gem5::ArmISA::si, and thread.

◆ getRegOperand() [2/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 186 of file cpu.hh.

References gem5::SimpleThread::getReg(), gem5::ArmISA::si, thread, and gem5::X86ISA::val.

◆ getWritableRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 192 of file cpu.hh.

References gem5::SimpleThread::getWritableReg(), gem5::ArmISA::si, and thread.

◆ handleError()

|

inline |

Definition at line 410 of file cpu.hh.

References dumpAndExit(), and exitOnError.

Referenced by readMem(), gem5::Checker< gem5::RefCountingPtr >::verify(), and writeMem().

◆ inHtmTransactionalState()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 259 of file cpu.hh.

References getHtmTransactionalDepth().

◆ init()

|

override |

Definition at line 59 of file cpu.cc.

References gem5::ThreadContext::getIsaPtr(), gem5::System::getRequestorId(), requestorId, gem5::BaseISA::setThreadContext(), systemPtr, and tc.

◆ initiateMemMgmtCmd()

|

inlineoverridevirtual |

Initiate a memory management command with no valid address.

Currently, these instructions need to bypass squashing in the O3 model Examples include HTM commands and TLBI commands. e.g. tell Ruby we're starting/stopping a HTM transaction, or tell Ruby to issue a TLBI operation

Implements gem5::ExecContext.

Definition at line 252 of file cpu.hh.

References gem5::NoFault, and panic.

◆ mwait()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

◆ mwaitAtomic()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 351 of file cpu.hh.

References gem5::SimpleThread::mmu, tc, and thread.

◆ newHtmTransactionUid()

|

inlineoverridevirtual |

◆ PARAMS()

| gem5::CheckerCPU::PARAMS | ( | CheckerCPU | ) |

◆ pcState() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 272 of file cpu.hh.

References gem5::SimpleThread::pcState(), and thread.

Referenced by gem5::Checker< gem5::RefCountingPtr >::advancePC(), gem5::Checker< gem5::RefCountingPtr >::handlePendingInt(), and gem5::Checker< gem5::RefCountingPtr >::verify().

◆ pcState() [2/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 277 of file cpu.hh.

References DPRINTF, gem5::SimpleThread::pcState(), thread, and gem5::X86ISA::val.

◆ readMem()

|

override |

Definition at line 167 of file cpu.cc.

References gem5::X86ISA::addr, checkFlags(), gem5::Packet::createRead(), gem5::curTick(), data, gem5::Packet::dataStatic(), dcachePort, flags, genMemFragmentRequest(), handleError(), mmu, gem5::Request::NO_ACCESS, gem5::NoFault, gem5::BaseMMU::Read, gem5::RequestPort::sendFunctional(), tc, gem5::BaseMMU::translateFunctional(), unverifiedMemData, unverifiedReq, and warn.

◆ readMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 226 of file cpu.hh.

References gem5::SimpleThread::readMemAccPredicate(), and thread.

◆ readMiscReg()

|

inlineoverridevirtual |

Reads a miscellaneous register, handling any architectural side effects due to reading that register.

Implements gem5::ExecContext.

Definition at line 292 of file cpu.hh.

References gem5::SimpleThread::readMiscReg(), and thread.

◆ readMiscRegNoEffect()

|

inline |

Definition at line 286 of file cpu.hh.

References gem5::SimpleThread::readMiscRegNoEffect(), and thread.

◆ readMiscRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 316 of file cpu.hh.

References gem5::MiscRegClass, gem5::SimpleThread::readMiscReg(), gem5::X86ISA::reg, gem5::ArmISA::si, and thread.

◆ readPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 217 of file cpu.hh.

References gem5::SimpleThread::readPredicate(), and thread.

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements gem5::ExecContext.

Definition at line 399 of file cpu.hh.

References gem5::SimpleThread::readStCondFailures(), and thread.

◆ recordPCChange()

|

inline |

Definition at line 334 of file cpu.hh.

References changedPC, newPCState, gem5::ArmISA::set, and gem5::X86ISA::val.

Referenced by gem5::CheckerThreadContext< TC >::pcState().

◆ serialize()

|

override |

◆ setDcachePort()

| void gem5::CheckerCPU::setDcachePort | ( | RequestPort * | dcache_port | ) |

Definition at line 124 of file cpu.cc.

References dcachePort.

◆ setIcachePort()

| void gem5::CheckerCPU::setIcachePort | ( | RequestPort * | icache_port | ) |

Definition at line 118 of file cpu.cc.

References icachePort.

◆ setMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 232 of file cpu.hh.

References gem5::SimpleThread::setMemAccPredicate(), thread, and gem5::X86ISA::val.

◆ setMiscReg()

|

inlineoverridevirtual |

Sets a miscellaneous register, handling any architectural side effects due to writing that register.

Implements gem5::ExecContext.

Definition at line 307 of file cpu.hh.

References DPRINTF, miscRegIdxs, gem5::SimpleThread::setMiscReg(), thread, and gem5::X86ISA::val.

Referenced by setMiscRegOperand().

◆ setMiscRegNoEffect()

|

inline |

Definition at line 298 of file cpu.hh.

References DPRINTF, miscRegIdxs, gem5::SimpleThread::setMiscRegNoEffect(), thread, and gem5::X86ISA::val.

◆ setMiscRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 324 of file cpu.hh.

References gem5::RegId::index(), gem5::MiscRegClass, gem5::X86ISA::reg, setMiscReg(), gem5::ArmISA::si, and gem5::X86ISA::val.

◆ setPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 220 of file cpu.hh.

References gem5::SimpleThread::setPredicate(), thread, and gem5::X86ISA::val.

◆ setRegOperand() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 208 of file cpu.hh.

References gem5::InvalidRegClass, gem5::MipsISA::is, gem5::SimpleThread::setReg(), gem5::ArmISA::si, thread, and gem5::X86ISA::val.

◆ setRegOperand() [2/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 198 of file cpu.hh.

References gem5::InvalidRegClass, gem5::MipsISA::is, result, gem5::SimpleThread::setReg(), gem5::ArmISA::si, thread, and gem5::X86ISA::val.

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements gem5::ExecContext.

◆ setSystem()

| void gem5::CheckerCPU::setSystem | ( | System * | system | ) |

Definition at line 96 of file cpu.cc.

References gem5::FullSystem, gem5::SimpleThread::getTC(), mmu, gem5::VegaISA::p, gem5::X86ISA::system, systemPtr, tc, thread, and workload.

Referenced by gem5::BaseSimpleCPU::BaseSimpleCPU().

◆ tcBase()

|

inlineoverridevirtual |

Returns a pointer to the ThreadContext.

Implements gem5::ExecContext.

Definition at line 421 of file cpu.hh.

References tc.

◆ threadBase()

|

inline |

◆ totalInsts()

|

inlineoverridevirtual |

◆ totalOps()

|

inlineoverridevirtual |

◆ unserialize()

|

override |

◆ wakeup()

◆ writeMem()

|

override |

Definition at line 251 of file cpu.cc.

References gem5::X86ISA::addr, checkFlags(), gem5::curTick(), data, flags, genMemFragmentRequest(), handleError(), mmu, gem5::NoFault, gem5::Request::STORE_NO_DATA, tc, gem5::BaseMMU::translateFunctional(), unverifiedMemData, unverifiedReq, warn, and gem5::BaseMMU::Write.

Member Data Documentation

◆ changedPC

| bool gem5::CheckerCPU::changedPC |

Definition at line 428 of file cpu.hh.

Referenced by CheckerCPU(), and recordPCChange().

◆ curMacroStaticInst

|

protected |

Definition at line 139 of file cpu.hh.

Referenced by CheckerCPU().

◆ curStaticInst

|

protected |

Definition at line 138 of file cpu.hh.

Referenced by CheckerCPU().

◆ dcachePort

|

protected |

Definition at line 128 of file cpu.hh.

Referenced by getDataPort(), readMem(), and setDcachePort().

◆ exitOnError

| bool gem5::CheckerCPU::exitOnError |

Definition at line 431 of file cpu.hh.

Referenced by CheckerCPU(), handleError(), and gem5::Checker< gem5::RefCountingPtr >::handleError().

◆ icachePort

|

protected |

Definition at line 127 of file cpu.hh.

Referenced by getInstPort(), and setIcachePort().

◆ miscRegIdxs

|

protected |

Definition at line 145 of file cpu.hh.

Referenced by setMiscReg(), and setMiscRegNoEffect().

◆ mmu

|

protected |

Definition at line 132 of file cpu.hh.

Referenced by CheckerCPU(), demapPage(), getMMUPtr(), readMem(), setSystem(), and writeMem().

◆ newPCState

| std::unique_ptr<PCStateBase> gem5::CheckerCPU::newPCState |

Definition at line 430 of file cpu.hh.

Referenced by recordPCChange().

◆ numInst

|

protected |

Definition at line 142 of file cpu.hh.

Referenced by CheckerCPU().

◆ numLoad

| Counter gem5::CheckerCPU::numLoad |

Definition at line 159 of file cpu.hh.

Referenced by CheckerCPU().

◆ requestorId

|

protected |

id attached to all issued requests

Definition at line 88 of file cpu.hh.

Referenced by genMemFragmentRequest(), and init().

◆ result

|

protected |

Definition at line 136 of file cpu.hh.

Referenced by setRegOperand().

◆ startNumInst

|

protected |

Definition at line 143 of file cpu.hh.

Referenced by CheckerCPU().

◆ startNumLoad

| Counter gem5::CheckerCPU::startNumLoad |

Definition at line 160 of file cpu.hh.

Referenced by CheckerCPU().

◆ systemPtr

|

protected |

Definition at line 125 of file cpu.hh.

Referenced by init(), and setSystem().

◆ tc

|

protected |

Definition at line 130 of file cpu.hh.

Referenced by genMemFragmentRequest(), init(), mwaitAtomic(), readMem(), setSystem(), tcBase(), and writeMem().

◆ thread

| SimpleThread* gem5::CheckerCPU::thread |

Definition at line 150 of file cpu.hh.

Referenced by dumpAndExit(), genMemFragmentRequest(), getHtmTransactionalDepth(), getRegOperand(), getWritableRegOperand(), mwaitAtomic(), pcState(), readMemAccPredicate(), readMiscReg(), readMiscRegNoEffect(), readMiscRegOperand(), readPredicate(), readStCondFailures(), setMemAccPredicate(), setMiscReg(), setMiscRegNoEffect(), setPredicate(), setRegOperand(), setSystem(), and threadBase().

◆ unverifiedMemData

| uint8_t* gem5::CheckerCPU::unverifiedMemData |

Definition at line 426 of file cpu.hh.

Referenced by readMem(), and writeMem().

◆ unverifiedReq

| RequestPtr gem5::CheckerCPU::unverifiedReq |

Definition at line 425 of file cpu.hh.

Referenced by readMem(), and writeMem().

◆ unverifiedResult

| InstResult gem5::CheckerCPU::unverifiedResult |

◆ updateOnError

| bool gem5::CheckerCPU::updateOnError |

Definition at line 432 of file cpu.hh.

Referenced by CheckerCPU(), and gem5::Checker< gem5::RefCountingPtr >::handleError().

◆ warnOnlyOnLoadError

| bool gem5::CheckerCPU::warnOnlyOnLoadError |

Definition at line 433 of file cpu.hh.

Referenced by CheckerCPU().

◆ willChangePC

| bool gem5::CheckerCPU::willChangePC |

Definition at line 429 of file cpu.hh.

Referenced by CheckerCPU().

◆ workload

|

protected |

Definition at line 123 of file cpu.hh.

Referenced by CheckerCPU(), and setSystem().

◆ youngestSN

| InstSeqNum gem5::CheckerCPU::youngestSN |

Definition at line 435 of file cpu.hh.

Referenced by CheckerCPU().

The documentation for this class was generated from the following files: