#include <exported_clock_rate_control.hh>

Public Types | |

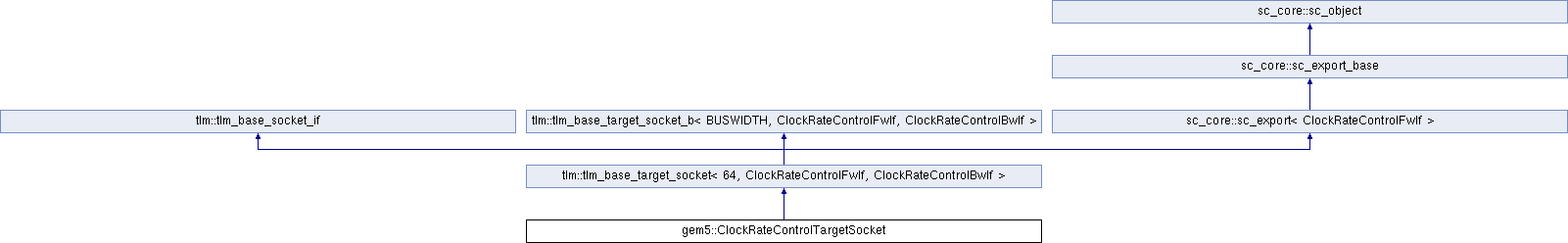

| typedef tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > | Base |

| Public Types inherited from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > | |

| typedef ClockRateControlFwIf | fw_interface_type |

| typedef ClockRateControlBwIf | bw_interface_type |

| typedef sc_core::sc_port< bw_interface_type, 1, sc_core::SC_ONE_OR_MORE_BOUND > | port_type |

| typedef sc_core::sc_export< fw_interface_type > | export_type |

| typedef tlm_base_initiator_socket_b< BUSWIDTH, fw_interface_type, bw_interface_type > | base_initiator_socket_type |

| typedef tlm_base_target_socket_b< BUSWIDTH, fw_interface_type, bw_interface_type > | base_type |

Public Member Functions | |

| const char * | kind () const override |

| std::type_index | get_protocol_types () const override |

| virtual void | bind (base_initiator_socket_type &s) |

| The following warning is disabled because the bind methods are overloaded in the derived class and the base class. | |

| virtual void | bind (base_type &s) |

| virtual void | bind (fw_interface_type &ifs) |

| void | operator() (base_initiator_socket_type &s) |

| void | operator() (base_type &s) |

| void | operator() (fw_interface_type &s) |

| Public Member Functions inherited from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > | |

| tlm_base_target_socket () | |

| tlm_base_target_socket (const char *name) | |

| void | operator() (base_initiator_socket_type &s) |

| void | operator() (base_type &s) |

| void | operator() (fw_interface_type &s) |

| int | size () const |

| bw_interface_type * | operator-> () |

| bw_interface_type * | operator[] (int i) |

| virtual sc_core::sc_port_base & | get_port_base () |

| virtual sc_core::sc_port_base const & | get_port_base () const |

| virtual sc_core::sc_export_base & | get_export_base () |

| virtual sc_core::sc_export_base const & | get_export_base () const |

| virtual unsigned int | get_bus_width () const |

| virtual tlm_socket_category | get_socket_category () const |

| virtual sc_core::sc_port_b< ClockRateControlBwIf > & | get_base_port () |

| virtual sc_core::sc_port_b< ClockRateControlBwIf > const & | get_base_port () const |

| virtual ClockRateControlFwIf & | get_base_interface () |

| virtual ClockRateControlFwIf const & | get_base_interface () const |

| virtual sc_core::sc_export< ClockRateControlFwIf > & | get_base_export () |

| virtual sc_core::sc_export< ClockRateControlFwIf > const & | get_base_export () const |

| Public Member Functions inherited from tlm::tlm_base_target_socket_b< BUSWIDTH, FW_IF, BW_IF > | |

| virtual | ~tlm_base_target_socket_b () |

| Public Member Functions inherited from sc_core::sc_export< IF > | |

| sc_export () | |

| sc_export (const char *n) | |

| virtual | ~sc_export () |

| void | operator() (IF &i) |

| The following warning is disabled because the bind methods are overloaded in the derived class and the base class. | |

| virtual void | bind (IF &i) |

| operator IF & () | |

| operator const IF & () const | |

| IF * | operator-> () |

| const IF * | operator-> () const |

| sc_interface * | get_iterface () override |

| const sc_interface * | get_interface () const override |

| Public Member Functions inherited from sc_core::sc_export_base | |

| sc_export_base (const char *n) | |

| ~sc_export_base () | |

| Public Member Functions inherited from sc_core::sc_object | |

| const char * | name () const |

| const char * | basename () const |

| virtual void | print (std::ostream &=std::cout) const |

| virtual void | dump (std::ostream &=std::cout) const |

| virtual const std::vector< sc_object * > & | get_child_objects () const |

| virtual const std::vector< sc_event * > & | get_child_events () const |

| sc_object * | get_parent_object () const |

| bool | add_attribute (sc_attr_base &) |

| sc_attr_base * | get_attribute (const std::string &) |

| sc_attr_base * | remove_attribute (const std::string &) |

| void | remove_all_attributes () |

| int | num_attributes () const |

| sc_attr_cltn & | attr_cltn () |

| const sc_attr_cltn & | attr_cltn () const |

| sc_simcontext * | simcontext () const |

Additional Inherited Members | |

| Protected Member Functions inherited from tlm::tlm_base_socket_if | |

| virtual | ~tlm_base_socket_if () |

| Protected Member Functions inherited from sc_core::sc_export< IF > | |

| void | before_end_of_elaboration () override |

| void | end_of_elaboration () override |

| void | start_of_simulation () override |

| void | end_of_simulation () override |

| Protected Member Functions inherited from sc_core::sc_object | |

| sc_object () | |

| sc_object (const char *) | |

| sc_object (const sc_object &) | |

| sc_object & | operator= (const sc_object &) |

| virtual | ~sc_object () |

| Protected Attributes inherited from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf > | |

| port_type | m_port |

Detailed Description

Definition at line 99 of file exported_clock_rate_control.hh.

Member Typedef Documentation

◆ Base

| typedef tlm::tlm_base_target_socket<64, ClockRateControlFwIf, ClockRateControlBwIf> gem5::ClockRateControlTargetSocket::Base |

Definition at line 105 of file exported_clock_rate_control.hh.

Member Function Documentation

◆ bind() [1/3]

|

inlinevirtual |

The following warning is disabled because the bind methods are overloaded in the derived class and the base class.

In GCC v13+ this 'overloaded-virtual' warning is strict enough to trigger here (though the code is correct). Please check section 9.3 of SystemC 2.3.1 release note for more details.

Reimplemented from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf >.

Definition at line 107 of file target_socket.hh.

◆ bind() [2/3]

|

inlinevirtual |

Reimplemented from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf >.

Definition at line 122 of file target_socket.hh.

◆ bind() [3/3]

|

inlinevirtual |

Reimplemented from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf >.

Definition at line 137 of file target_socket.hh.

◆ get_protocol_types()

|

inlineoverridevirtual |

Implements tlm::tlm_base_socket_if.

Definition at line 119 of file exported_clock_rate_control.hh.

◆ kind()

|

inlineoverridevirtual |

Reimplemented from tlm::tlm_base_target_socket< 64, ClockRateControlFwIf, ClockRateControlBwIf >.

Definition at line 113 of file exported_clock_rate_control.hh.

◆ operator()() [1/3]

|

inline |

Definition at line 115 of file target_socket.hh.

◆ operator()() [2/3]

|

inline |

Definition at line 130 of file target_socket.hh.

◆ operator()() [3/3]

|

inline |

Definition at line 147 of file target_socket.hh.

The documentation for this class was generated from the following file:

- arch/arm/fastmodel/protocol/exported_clock_rate_control.hh

Generated on Sat Oct 18 2025 08:06:50 for gem5 by doxygen 1.14.0