#include <op_encodings.hh>

Public Member Functions | |

| Inst_SMEM (InFmt_SMEM *, const std::string &opcode) | |

| ~Inst_SMEM () | |

| int | instSize () const override |

| void | generateDisassembly () override |

| bool | isScalarRegister (int opIdx) override |

| bool | isVectorRegister (int opIdx) override |

| int | getRegisterIndex (int opIdx, GPUDynInstPtr gpuDynInst) override |

Public Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst Public Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst | |

| GCN3GPUStaticInst (const std::string &opcode) | |

| ~GCN3GPUStaticInst () | |

| bool | isFlatScratchRegister (int opIdx) override |

| bool | isExecMaskRegister (int opIdx) override |

| bool | isSrcOperand (int opIdx) override |

| bool | isDstOperand (int opIdx) override |

| int | getOperandSize (int opIdx) override |

| int | coalescerTokenCount () const override |

| Return the number of tokens needed by the coalescer. More... | |

| ScalarRegU32 | srcLiteral () const override |

Public Member Functions inherited from GPUStaticInst Public Member Functions inherited from GPUStaticInst | |

| GPUStaticInst (const std::string &opcode) | |

| void | instAddr (int inst_addr) |

| int | instAddr () const |

| int | nextInstAddr () const |

| void | instNum (int num) |

| int | instNum () |

| void | ipdInstNum (int num) |

| int | ipdInstNum () const |

| virtual void | execute (GPUDynInstPtr gpuDynInst)=0 |

| const std::string & | disassemble () |

| virtual int | getNumOperands ()=0 |

| virtual bool | isCondRegister (int operandIndex)=0 |

| virtual int | numDstRegOperands ()=0 |

| virtual int | numSrcRegOperands ()=0 |

| virtual bool | isValid () const =0 |

| bool | isALU () const |

| bool | isBranch () const |

| bool | isNop () const |

| bool | isReturn () const |

| bool | isUnconditionalJump () const |

| bool | isSpecialOp () const |

| bool | isWaitcnt () const |

| bool | isBarrier () const |

| bool | isMemFence () const |

| bool | isMemRef () const |

| bool | isFlat () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isAtomicNoRet () const |

| bool | isAtomicRet () const |

| bool | isScalar () const |

| bool | readsSCC () const |

| bool | writesSCC () const |

| bool | readsVCC () const |

| bool | writesVCC () const |

| bool | isAtomicAnd () const |

| bool | isAtomicOr () const |

| bool | isAtomicXor () const |

| bool | isAtomicCAS () const |

| bool | isAtomicExch () const |

| bool | isAtomicAdd () const |

| bool | isAtomicSub () const |

| bool | isAtomicInc () const |

| bool | isAtomicDec () const |

| bool | isAtomicMax () const |

| bool | isAtomicMin () const |

| bool | isArgLoad () const |

| bool | isGlobalMem () const |

| bool | isLocalMem () const |

| bool | isArgSeg () const |

| bool | isGlobalSeg () const |

| bool | isGroupSeg () const |

| bool | isKernArgSeg () const |

| bool | isPrivateSeg () const |

| bool | isReadOnlySeg () const |

| bool | isSpillSeg () const |

| bool | isWorkitemScope () const |

| bool | isWavefrontScope () const |

| bool | isWorkgroupScope () const |

| bool | isDeviceScope () const |

| bool | isSystemScope () const |

| bool | isNoScope () const |

| bool | isRelaxedOrder () const |

| bool | isAcquire () const |

| bool | isRelease () const |

| bool | isAcquireRelease () const |

| bool | isNoOrder () const |

| bool | isGloballyCoherent () const |

| Coherence domain of a memory instruction. More... | |

| bool | isSystemCoherent () const |

| virtual void | initiateAcc (GPUDynInstPtr gpuDynInst) |

| virtual void | completeAcc (GPUDynInstPtr gpuDynInst) |

| virtual uint32_t | getTargetPc () |

| void | setFlag (Flags flag) |

| virtual void | execLdAcq (GPUDynInstPtr gpuDynInst) |

| virtual void | execSt (GPUDynInstPtr gpuDynInst) |

| virtual void | execAtomic (GPUDynInstPtr gpuDynInst) |

| virtual void | execAtomicAcq (GPUDynInstPtr gpuDynInst) |

Protected Member Functions | |

| template<int N> | |

| void | initMemRead (GPUDynInstPtr gpuDynInst) |

| initiate a memory read access for N dwords More... | |

| template<int N> | |

| void | initMemWrite (GPUDynInstPtr gpuDynInst) |

| initiate a memory write access for N dwords More... | |

| void | calcAddr (GPUDynInstPtr gpuDynInst, ConstScalarOperandU64 &addr, ScalarRegU32 offset) |

Protected Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst Protected Member Functions inherited from Gcn3ISA::GCN3GPUStaticInst | |

| void | panicUnimplemented () const |

Protected Attributes | |

| InFmt_SMEM | instData |

| InFmt_SMEM_1 | extData |

Protected Attributes inherited from Gcn3ISA::GCN3GPUStaticInst Protected Attributes inherited from Gcn3ISA::GCN3GPUStaticInst | |

| ScalarRegU32 | _srcLiteral |

| if the instruction has a src literal - an immediate value that is part of the instruction stream - we store that here More... | |

Protected Attributes inherited from GPUStaticInst Protected Attributes inherited from GPUStaticInst | |

| const std::string | opcode |

| std::string | disassembly |

| int | _instNum |

| int | _instAddr |

| int | _ipdInstNum |

| Identifier of the immediate post-dominator instruction. More... | |

| std::bitset< Num_Flags > | _flags |

Additional Inherited Members | |

Public Attributes inherited from GPUStaticInst Public Attributes inherited from GPUStaticInst | |

| Enums::StorageClassType | executed_as |

Static Public Attributes inherited from GPUStaticInst Static Public Attributes inherited from GPUStaticInst | |

| static uint64_t | dynamic_id_count |

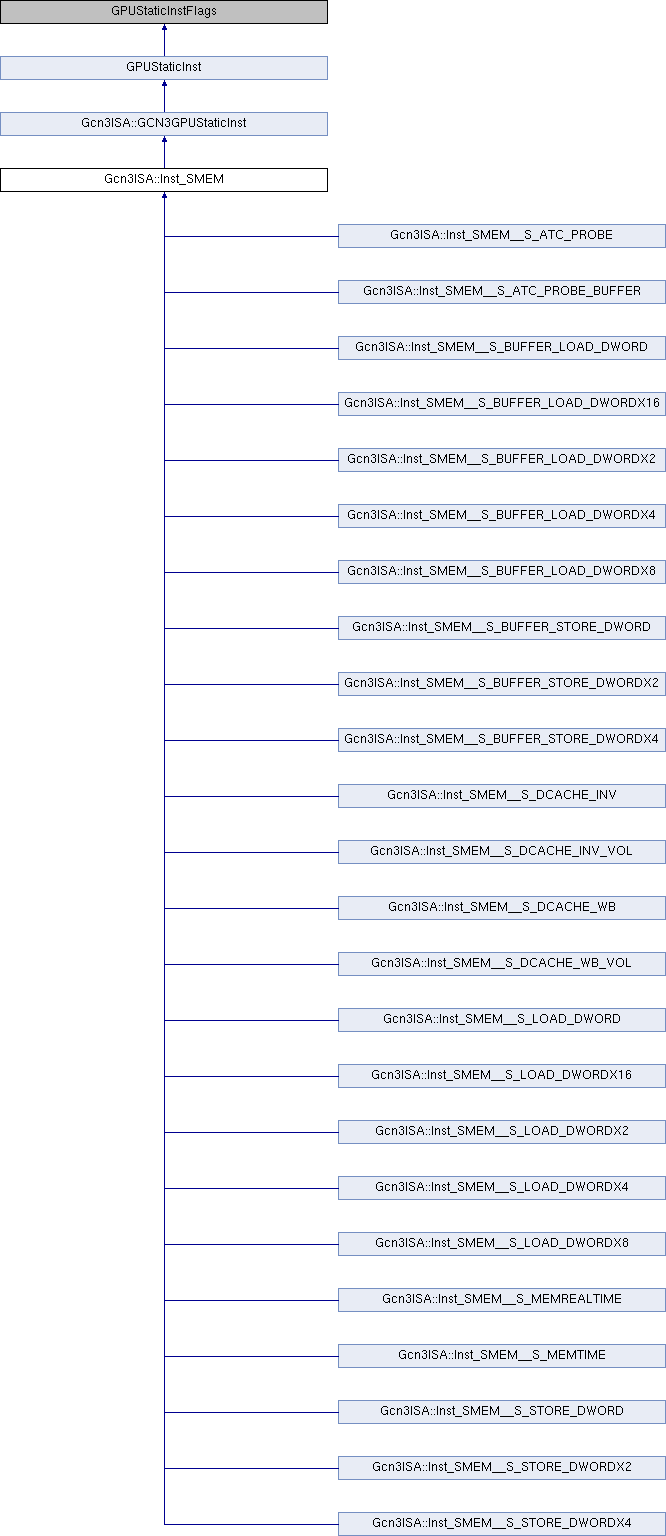

Detailed Description

Definition at line 156 of file op_encodings.hh.

Constructor & Destructor Documentation

◆ Inst_SMEM()

| Gcn3ISA::Inst_SMEM::Inst_SMEM | ( | InFmt_SMEM * | iFmt, |

| const std::string & | opcode | ||

| ) |

Definition at line 556 of file op_encodings.cc.

References Gcn3ISA::GCN3GPUStaticInst::_srcLiteral, extData, Gcn3ISA::InFmt_SMEM::GLC, instData, and GPUStaticInst::setFlag().

◆ ~Inst_SMEM()

| Gcn3ISA::Inst_SMEM::~Inst_SMEM | ( | ) |

Definition at line 572 of file op_encodings.cc.

Member Function Documentation

◆ calcAddr()

|

inlineprotected |

Definition at line 273 of file op_encodings.hh.

References ArmISA::offset, Gcn3ISA::ScalarOperand< DataType, Const, NumDwords >::rawData(), and MipsISA::vaddr.

Referenced by Gcn3ISA::Inst_SMEM__S_LOAD_DWORD::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX2::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX4::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX8::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX16::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORD::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORDX2::execute(), and Gcn3ISA::Inst_SMEM__S_STORE_DWORDX4::execute().

◆ generateDisassembly()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 583 of file op_encodings.cc.

References GPUStaticInst::disassembly, extData, GPUStaticInst::getNumOperands(), Gcn3ISA::GCN3GPUStaticInst::getOperandSize(), Gcn3ISA::InFmt_SMEM::IMM, instData, GPUStaticInst::numDstRegOperands(), Gcn3ISA::InFmt_SMEM_1::OFFSET, Gcn3ISA::InFmt_SMEM::SBASE, and Gcn3ISA::InFmt_SMEM::SDATA.

◆ getRegisterIndex()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 652 of file op_encodings.cc.

References extData, fatal, GPUStaticInst::getNumOperands(), Gcn3ISA::InFmt_SMEM::IMM, instData, Gcn3ISA::InFmt_SMEM_1::OFFSET, Gcn3ISA::opSelectorToRegIdx(), Gcn3ISA::InFmt_SMEM::SBASE, and Gcn3ISA::InFmt_SMEM::SDATA.

◆ initMemRead()

|

inlineprotected |

initiate a memory read access for N dwords

the base address of the cache line where the the last byte of the request will be stored.

if the base cache line address of the last byte is greater than the address of the first byte then we have a misaligned access.

Definition at line 175 of file op_encodings.hh.

References Packet::dataStatic(), MemCmd::ReadReq, roundDown(), Request::splitOnVaddr(), and MipsISA::vaddr.

◆ initMemWrite()

|

inlineprotected |

initiate a memory write access for N dwords

the base address of the cache line where the the last byte of the request will be stored.

if the base cache line address of the last byte is greater than the address of the first byte then we have a misaligned access.

Definition at line 226 of file op_encodings.hh.

References Packet::dataStatic(), MemCmd::ReadReq, roundDown(), Request::splitOnVaddr(), MipsISA::vaddr, and MemCmd::WriteReq.

◆ instSize()

|

overridevirtual |

Implements GPUStaticInst.

Definition at line 577 of file op_encodings.cc.

◆ isScalarRegister()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 618 of file op_encodings.cc.

References extData, fatal, GPUStaticInst::getNumOperands(), Gcn3ISA::InFmt_SMEM::IMM, instData, Gcn3ISA::isScalarReg(), Gcn3ISA::InFmt_SMEM_1::OFFSET, and Gcn3ISA::InFmt_SMEM::SDATA.

◆ isVectorRegister()

|

overridevirtual |

Reimplemented from Gcn3ISA::GCN3GPUStaticInst.

Definition at line 642 of file op_encodings.cc.

References GPUStaticInst::getNumOperands().

Member Data Documentation

◆ extData

|

protected |

Definition at line 285 of file op_encodings.hh.

Referenced by Gcn3ISA::Inst_SMEM__S_LOAD_DWORD::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX2::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX4::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX8::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX16::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORD::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORDX2::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORDX4::execute(), generateDisassembly(), getRegisterIndex(), Inst_SMEM(), and isScalarRegister().

◆ instData

|

protected |

Definition at line 283 of file op_encodings.hh.

Referenced by Gcn3ISA::Inst_SMEM__S_LOAD_DWORD::completeAcc(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX2::completeAcc(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX4::completeAcc(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX8::completeAcc(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX16::completeAcc(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORD::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX2::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX4::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX8::execute(), Gcn3ISA::Inst_SMEM__S_LOAD_DWORDX16::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORD::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORDX2::execute(), Gcn3ISA::Inst_SMEM__S_STORE_DWORDX4::execute(), generateDisassembly(), getRegisterIndex(), Gcn3ISA::Inst_SMEM__S_STORE_DWORD::initiateAcc(), Gcn3ISA::Inst_SMEM__S_STORE_DWORDX2::initiateAcc(), Gcn3ISA::Inst_SMEM__S_STORE_DWORDX4::initiateAcc(), Inst_SMEM(), and isScalarRegister().

The documentation for this class was generated from the following files:

- arch/gcn3/insts/op_encodings.hh

- arch/gcn3/insts/op_encodings.cc