Memory access queuing. More...

#include <fetch1.hh>

Public Types | |

| enum | FetchRequestState { NotIssued, InTranslation, Translated, RequestIssuing, Complete } |

| Progress of this request through address translation and memory. More... | |

Public Member Functions | |

| void | makePacket () |

| Make a packet to use with the memory transaction. More... | |

| void | reportData (std::ostream &os) const |

| Report interface. More... | |

| bool | isDiscardable () const |

| Is this line out of date with the current stream/prediction sequence and can it be discarded without orphaning in flight TLB lookups/memory accesses? More... | |

| bool | isComplete () const |

| Is this a complete read line or fault. More... | |

| FetchRequest (Fetch1 &fetch_, InstId id_, TheISA::PCState pc_) | |

| ~FetchRequest () | |

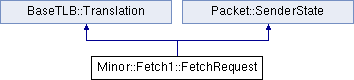

Public Member Functions inherited from BaseTLB::Translation Public Member Functions inherited from BaseTLB::Translation | |

| virtual | ~Translation () |

| virtual bool | squashed () const |

| This function is used by the page table walker to determine if it should translate the a pending request or if the underlying request has been squashed. More... | |

Public Member Functions inherited from Packet::SenderState Public Member Functions inherited from Packet::SenderState | |

| SenderState () | |

| virtual | ~SenderState () |

Public Attributes | |

| FetchRequestState | state |

| InstId | id |

| Identity of the line that this request will generate. More... | |

| PacketPtr | packet |

| FetchRequests carry packets while they're in the requests and transfers responses queues. More... | |

| RequestPtr | request |

| The underlying request that this fetch represents. More... | |

| TheISA::PCState | pc |

| PC to fixup with line address. More... | |

| Fault | fault |

| Fill in a fault if one happens during fetch, check this by picking apart the response packet. More... | |

Public Attributes inherited from Packet::SenderState Public Attributes inherited from Packet::SenderState | |

| SenderState * | predecessor |

Protected Member Functions | |

| void | markDelayed () |

| BaseTLB::Translation interface. More... | |

| void | finish (const Fault &fault_, const RequestPtr &request_, ThreadContext *tc, BaseTLB::Mode mode) |

| Interface for ITLB responses. More... | |

Protected Attributes | |

| Fetch1 & | fetch |

| Owning fetch unit. More... | |

Detailed Description

Memory access queuing.

A request can be submitted by pushing it onto the requests queue after issuing an ITLB lookup (state becomes InTranslation) with a FetchSenderState senderState containing the current lineSeqNum and stream/predictionSeqNum.

Translated packets (state becomes Translation) are then passed to the memory system and the transfers queue (state becomes RequestIssuing). Retries are handled by leaving the packet on the requests queue and changing the state to IcacheNeedsRetry).

Responses from the memory system alter the request object (state become Complete). Responses can be picked up from the head of the transfers queue to pass on to Fetch2. Structure to hold SenderState info through translation and memory accesses.

Member Enumeration Documentation

◆ FetchRequestState

Constructor & Destructor Documentation

◆ FetchRequest()

◆ ~FetchRequest()

Member Function Documentation

◆ finish()

|

protectedvirtual |

Interface for ITLB responses.

Populates self and then passes the request on to the ports' handleTLBResponse member function

Implements BaseTLB::Translation.

Definition at line 230 of file fetch1.cc.

References Minor::Pipeline::Fetch1StageId.

◆ isComplete()

|

inline |

Is this a complete read line or fault.

Definition at line 152 of file fetch1.hh.

References Complete, and state.

Referenced by Minor::Fetch1::evaluate().

◆ isDiscardable()

| bool Minor::Fetch1::FetchRequest::isDiscardable | ( | ) | const |

Is this line out of date with the current stream/prediction sequence and can it be discarded without orphaning in flight TLB lookups/memory accesses?

Definition at line 741 of file fetch1.cc.

References Minor::Fetch1::Fetch1ThreadInfo::predictionSeqNum, and Minor::Fetch1::Fetch1ThreadInfo::streamSeqNum.

Referenced by Minor::Fetch1::evaluate(), and Minor::Fetch1::tryToSendToTransfers().

◆ makePacket()

| void Minor::Fetch1::FetchRequest::makePacket | ( | ) |

Make a packet to use with the memory transaction.

Definition at line 218 of file fetch1.cc.

References Packet::allocate(), packet, Packet::pushSenderState(), MemCmd::ReadReq, and request.

Referenced by Minor::Fetch1::tryToSendToTransfers().

◆ markDelayed()

|

inlineprotectedvirtual |

BaseTLB::Translation interface.

Interface for ITLB responses. We can handle delay, so don't do anything

Implements BaseTLB::Translation.

◆ reportData()

| void Minor::Fetch1::FetchRequest::reportData | ( | std::ostream & | os | ) | const |

Member Data Documentation

◆ fault

| Fault Minor::Fetch1::FetchRequest::fault |

Fill in a fault if one happens during fetch, check this by picking apart the response packet.

Definition at line 138 of file fetch1.hh.

Referenced by Minor::Fetch1::handleTLBResponse(), Minor::Fetch1::minorTraceResponseLine(), Minor::Fetch1::processResponse(), and Minor::Fetch1::tryToSendToTransfers().

◆ fetch

|

protected |

◆ id

| InstId Minor::Fetch1::FetchRequest::id |

Identity of the line that this request will generate.

Definition at line 122 of file fetch1.hh.

Referenced by Minor::Fetch1::evaluate(), Minor::Fetch1::fetchLine(), Minor::Fetch1::minorTraceResponseLine(), Minor::Fetch1::processResponse(), Minor::Fetch1::recvTimingResp(), and Minor::Fetch1::tryToSend().

◆ packet

| PacketPtr Minor::Fetch1::FetchRequest::packet |

FetchRequests carry packets while they're in the requests and transfers responses queues.

When a Packet returns from the memory system, its request needs to have its packet updated as this may have changed in flight

Definition at line 128 of file fetch1.hh.

Referenced by makePacket(), Minor::Fetch1::minorTraceResponseLine(), Minor::Fetch1::processResponse(), Minor::Fetch1::recvTimingResp(), Minor::Fetch1::tryToSend(), and Minor::Fetch1::tryToSendToTransfers().

◆ pc

| TheISA::PCState Minor::Fetch1::FetchRequest::pc |

PC to fixup with line address.

Definition at line 134 of file fetch1.hh.

Referenced by Minor::Fetch1::processResponse().

◆ request

| RequestPtr Minor::Fetch1::FetchRequest::request |

The underlying request that this fetch represents.

Definition at line 131 of file fetch1.hh.

Referenced by Minor::Fetch1::fetchLine(), FetchRequest(), Minor::Fetch1::handleTLBResponse(), makePacket(), Minor::Fetch1::minorTraceResponseLine(), and Minor::Fetch1::processResponse().

◆ state

| FetchRequestState Minor::Fetch1::FetchRequest::state |

Definition at line 119 of file fetch1.hh.

Referenced by Minor::Fetch1::fetchLine(), Minor::Fetch1::handleTLBResponse(), isComplete(), Minor::Fetch1::recvTimingResp(), Minor::Fetch1::tryToSend(), and Minor::Fetch1::tryToSendToTransfers().

The documentation for this class was generated from the following files: