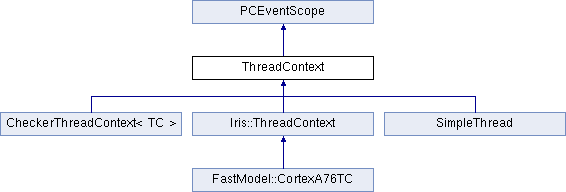

ThreadContext is the external interface to all thread state for anything outside of the CPU. More...

#include <thread_context.hh>

Public Types | |

| enum | Status { Active, Suspended, Halting, Halted } |

Public Member Functions | |

| virtual | ~ThreadContext () |

| virtual BaseCPU * | getCpuPtr ()=0 |

| virtual int | cpuId () const =0 |

| virtual uint32_t | socketId () const =0 |

| virtual int | threadId () const =0 |

| virtual void | setThreadId (int id)=0 |

| virtual ContextID | contextId () const =0 |

| virtual void | setContextId (ContextID id)=0 |

| virtual BaseTLB * | getITBPtr ()=0 |

| virtual BaseTLB * | getDTBPtr ()=0 |

| virtual CheckerCPU * | getCheckerCpuPtr ()=0 |

| virtual BaseISA * | getIsaPtr ()=0 |

| virtual TheISA::Decoder * | getDecoderPtr ()=0 |

| virtual System * | getSystemPtr ()=0 |

| virtual PortProxy & | getPhysProxy ()=0 |

| virtual PortProxy & | getVirtProxy ()=0 |

| virtual void | initMemProxies (ThreadContext *tc)=0 |

| Initialise the physical and virtual port proxies and tie them to the data port of the CPU. More... | |

| virtual Process * | getProcessPtr ()=0 |

| virtual void | setProcessPtr (Process *p)=0 |

| virtual Status | status () const =0 |

| virtual void | setStatus (Status new_status)=0 |

| virtual void | activate ()=0 |

| Set the status to Active. More... | |

| virtual void | suspend ()=0 |

| Set the status to Suspended. More... | |

| virtual void | halt ()=0 |

| Set the status to Halted. More... | |

| void | quiesce () |

| Quiesce thread context. More... | |

| void | quiesceTick (Tick resume) |

| Quiesce, suspend, and schedule activate at resume. More... | |

| virtual void | takeOverFrom (ThreadContext *old_context)=0 |

| virtual void | regStats (const std::string &name) |

| virtual void | scheduleInstCountEvent (Event *event, Tick count)=0 |

| virtual void | descheduleInstCountEvent (Event *event)=0 |

| virtual Tick | getCurrentInstCount ()=0 |

| virtual Tick | readLastActivate ()=0 |

| virtual Tick | readLastSuspend ()=0 |

| virtual void | copyArchRegs (ThreadContext *tc)=0 |

| virtual void | clearArchRegs ()=0 |

| virtual RegVal | readIntReg (RegIndex reg_idx) const =0 |

| virtual RegVal | readFloatReg (RegIndex reg_idx) const =0 |

| virtual const VecRegContainer & | readVecReg (const RegId ®) const =0 |

| virtual VecRegContainer & | getWritableVecReg (const RegId ®)=0 |

| virtual const VecElem & | readVecElem (const RegId ®) const =0 |

| virtual const VecPredRegContainer & | readVecPredReg (const RegId ®) const =0 |

| virtual VecPredRegContainer & | getWritableVecPredReg (const RegId ®)=0 |

| virtual RegVal | readCCReg (RegIndex reg_idx) const =0 |

| virtual void | setIntReg (RegIndex reg_idx, RegVal val)=0 |

| virtual void | setFloatReg (RegIndex reg_idx, RegVal val)=0 |

| virtual void | setVecReg (const RegId ®, const VecRegContainer &val)=0 |

| virtual void | setVecElem (const RegId ®, const VecElem &val)=0 |

| virtual void | setVecPredReg (const RegId ®, const VecPredRegContainer &val)=0 |

| virtual void | setCCReg (RegIndex reg_idx, RegVal val)=0 |

| virtual TheISA::PCState | pcState () const =0 |

| virtual void | pcState (const TheISA::PCState &val)=0 |

| void | setNPC (Addr val) |

| virtual void | pcStateNoRecord (const TheISA::PCState &val)=0 |

| virtual Addr | instAddr () const =0 |

| virtual Addr | nextInstAddr () const =0 |

| virtual MicroPC | microPC () const =0 |

| virtual RegVal | readMiscRegNoEffect (RegIndex misc_reg) const =0 |

| virtual RegVal | readMiscReg (RegIndex misc_reg)=0 |

| virtual void | setMiscRegNoEffect (RegIndex misc_reg, RegVal val)=0 |

| virtual void | setMiscReg (RegIndex misc_reg, RegVal val)=0 |

| virtual RegId | flattenRegId (const RegId ®Id) const =0 |

| virtual unsigned | readStCondFailures () const =0 |

| virtual void | setStCondFailures (unsigned sc_failures)=0 |

| virtual Counter | readFuncExeInst () const =0 |

| virtual void | syscall ()=0 |

| virtual int | exit () |

| virtual void | htmAbortTransaction (uint64_t htm_uid, HtmFailureFaultCause cause)=0 |

| virtual BaseHTMCheckpointPtr & | getHtmCheckpointPtr ()=0 |

| virtual void | setHtmCheckpointPtr (BaseHTMCheckpointPtr cpt)=0 |

| virtual ConstVecLane8 | readVec8BitLaneReg (const RegId ®) const =0 |

| Vector Register Lane Interfaces. More... | |

| virtual ConstVecLane16 | readVec16BitLaneReg (const RegId ®) const =0 |

| Reads source vector 16bit operand. More... | |

| virtual ConstVecLane32 | readVec32BitLaneReg (const RegId ®) const =0 |

| Reads source vector 32bit operand. More... | |

| virtual ConstVecLane64 | readVec64BitLaneReg (const RegId ®) const =0 |

| Reads source vector 64bit operand. More... | |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::Byte > &val)=0 |

| Write a lane of the destination vector register. More... | |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::TwoByte > &val)=0 |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::FourByte > &val)=0 |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::EightByte > &val)=0 |

| virtual RegVal | readIntRegFlat (RegIndex idx) const =0 |

| Flat register interfaces. More... | |

| virtual void | setIntRegFlat (RegIndex idx, RegVal val)=0 |

| virtual RegVal | readFloatRegFlat (RegIndex idx) const =0 |

| virtual void | setFloatRegFlat (RegIndex idx, RegVal val)=0 |

| virtual const VecRegContainer & | readVecRegFlat (RegIndex idx) const =0 |

| virtual VecRegContainer & | getWritableVecRegFlat (RegIndex idx)=0 |

| virtual void | setVecRegFlat (RegIndex idx, const VecRegContainer &val)=0 |

| virtual const VecElem & | readVecElemFlat (RegIndex idx, const ElemIndex &elemIdx) const =0 |

| virtual void | setVecElemFlat (RegIndex idx, const ElemIndex &elemIdx, const VecElem &val)=0 |

| virtual const VecPredRegContainer & | readVecPredRegFlat (RegIndex idx) const =0 |

| virtual VecPredRegContainer & | getWritableVecPredRegFlat (RegIndex idx)=0 |

| virtual void | setVecPredRegFlat (RegIndex idx, const VecPredRegContainer &val)=0 |

| virtual RegVal | readCCRegFlat (RegIndex idx) const =0 |

| virtual void | setCCRegFlat (RegIndex idx, RegVal val)=0 |

Public Member Functions inherited from PCEventScope Public Member Functions inherited from PCEventScope | |

| virtual bool | remove (PCEvent *event)=0 |

| virtual bool | schedule (PCEvent *event)=0 |

Static Public Member Functions | |

| static void | compare (ThreadContext *one, ThreadContext *two) |

| function to compare two thread contexts (for debugging) More... | |

Public Attributes | |

| int | intResult = DefaultIntResult |

| double | floatResult = DefaultFloatResult |

| int | intOffset = 0 |

Static Public Attributes | |

| static const int | ints [] |

| static const double | floats [] |

| static const int | DefaultIntResult = 0 |

| static const double | DefaultFloatResult = 0.0 |

Protected Types | |

| typedef TheISA::MachInst | MachInst |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | VecElem = TheISA::VecElem |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

Detailed Description

ThreadContext is the external interface to all thread state for anything outside of the CPU.

It provides all accessor methods to state that might be needed by external objects, ranging from register values to things such as kernel stats. It is an abstract base class; the CPU can create its own ThreadContext by deriving from it.

The ThreadContext is slightly different than the ExecContext. The ThreadContext provides access to an individual thread's state; an ExecContext provides ISA access to the CPU (meaning it is implicitly multithreaded on SMT systems). Additionally the ThreadState is an abstract class that exactly defines the interface; the ExecContext is a more implicit interface that must be implemented so that the ISA can access whatever state it needs.

Definition at line 88 of file thread_context.hh.

Member Typedef Documentation

◆ MachInst

|

protected |

Definition at line 91 of file thread_context.hh.

◆ VecElem

|

protected |

Definition at line 93 of file thread_context.hh.

◆ VecPredRegContainer

|

protected |

Definition at line 94 of file thread_context.hh.

◆ VecRegContainer

|

protected |

Definition at line 92 of file thread_context.hh.

Member Enumeration Documentation

◆ Status

Definition at line 98 of file thread_context.hh.

Constructor & Destructor Documentation

◆ ~ThreadContext()

|

inlinevirtual |

Reimplemented in Iris::ThreadContext.

Definition at line 118 of file thread_context.hh.

Member Function Documentation

◆ activate()

|

pure virtual |

Set the status to Active.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by cloneFunc(), execveFunc(), Process::initState(), FVPBasePwrCtrl::startCoreUp(), PseudoInst::wakeCPU(), and FutexMap::wakeup_bitset().

◆ clearArchRegs()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by cloneFunc(), execveFunc(), and ArmISA::Reset::invoke().

◆ compare()

|

static |

function to compare two thread contexts (for debugging)

Definition at line 55 of file thread_context.cc.

References contextId(), cpuId(), DPRINTF, ArmISA::i, ArmISA::NumCCRegs, ArmISA::NumFloatRegs, ArmISA::NumIntRegs, ArmISA::NumMiscRegs, ArmISA::NumVecPredRegs, ArmISA::NumVecRegs, Ps2::one, panic, pcState(), readCCReg(), readFloatReg(), readIntReg(), readMiscRegNoEffect(), readVecPredReg(), readVecReg(), ArmISA::t1, ArmISA::t2, VecPredRegClass, and VecRegClass.

◆ contextId()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::ISA::addressTranslation(), ArmISA::ISA::addressTranslation64(), FVPBasePwrCtrl::clearStandByWfi(), FVPBasePwrCtrl::clearWakeRequest(), cloneFunc(), compare(), SimpleThread::copyState(), BaseKvmCPU::doMMIOAccess(), execveFunc(), X86ISA::TLB::finalizePhysical(), CheckerCPU::genMemFragmentRequest(), ArmPPIGen::get(), FVPBasePwrCtrl::getCorePwrStatus(), getcpuFunc(), ArmISA::ISA::getGenericTimer(), X86KvmCPU::handleKvmExitIO(), FVPBasePwrCtrl::powerCoreOff(), FVPBasePwrCtrl::powerCoreOn(), quiesce(), quiesceTick(), X86ISA::ISA::readMiscReg(), RiscvISA::ISA::readMiscReg(), BaseCPU::registerThreadContexts(), FVPBasePwrCtrl::setStandByWfi(), ArmISA::PMU::setThreadContext(), ArmISA::ISA::setupThreadContext(), FVPBasePwrCtrl::setWakeRequest(), FVPBasePwrCtrl::startCoreUp(), BaseCPU::takeOverFrom(), takeOverFrom(), ArmInterruptPin::targetContext(), X86ISA::GpuTLB::translate(), TranslatingPortProxy::tryMemsetBlob(), TranslatingPortProxy::tryReadBlob(), TranslatingPortProxy::tryWriteBlob(), and ArmISA::TLB::updateMiscReg().

◆ copyArchRegs()

|

pure virtual |

Implemented in SimpleThread, and CheckerThreadContext< TC >.

Referenced by takeOverFrom().

◆ cpuId()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by cloneFunc(), compare(), ArmISA::getAff0(), ArmISA::getAff1(), ArmISA::getMPIDR(), ArmISA::DumpStats::process(), X86ISA::Interrupts::setThreadContext(), and Trace::InstPBTrace::traceInst().

◆ descheduleInstCountEvent()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by BaseRemoteGDB::descheduleInstCommitEvent().

◆ exit()

|

inlinevirtual |

Definition at line 302 of file thread_context.hh.

◆ flattenRegId()

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by Minor::flattenRegIndex(), DefaultRename< Impl >::renameDestRegs(), and DefaultRename< Impl >::renameSrcRegs().

◆ getCheckerCpuPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by BaseCPU::flushTLBs(), ArmISA::TLBIALL::operator()(), ArmISA::TLBIASID::operator()(), ArmISA::TLBIALLN::operator()(), ArmISA::TLBIMVAA::operator()(), ArmISA::TLBIMVA::operator()(), ArmISA::TLBIIPA::operator()(), ArmISA::SkipFunc::returnFromFuncIn(), ArmISA::ISA::setMiscReg(), and BaseCPU::takeOverFrom().

◆ getCpuPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by Linux::devRandom(), SparcISA::TLB::doMmuRegRead(), SparcISA::TLB::doMmuRegWrite(), BaseStackTrace::dump(), PseudoInst::dumpresetstats(), PseudoInst::dumpstats(), ArmISA::TableWalker::fetchDescriptor(), ArmISA::Stage2MMU::Stage2Translation::finish(), PseudoInst::initParam(), RiscvISA::RiscvFault::invoke(), ArmISA::Reset::invoke(), ArmISA::AbortFault< DataAbort >::invoke(), ArmISA::SystemError::invoke(), ArmISA::ArmSev::invoke(), PseudoInst::loadsymbol(), PseudoInst::m5checkpoint(), Linux::openSpecialFile(), FVPBasePwrCtrl::powerCoreOff(), FVPBasePwrCtrl::powerCoreOn(), ArmISA::DumpStats::process(), PseudoInst::quiesceCycles(), PseudoInst::quiesceSkip(), X86ISA::ISA::readMiscReg(), RiscvISA::ISA::readMiscReg(), SparcISA::ISA::readMiscReg(), ArmISA::ISA::readMiscReg(), MipsISA::readRegOtherThread(), System::Threads::replace(), PseudoInst::resetstats(), ArmISA::sendEvent(), X86ISA::ISA::setMiscReg(), RiscvISA::ISA::setMiscReg(), MipsISA::ISA::setMiscReg(), SparcISA::ISA::setMiscReg(), MipsISA::setRegOtherThread(), Trace::TarmacContext::tarmacCpuName(), PseudoInst::workbegin(), and PseudoInst::workend().

◆ getCurrentInstCount()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by BaseRemoteGDB::scheduleInstCommitEvent().

◆ getDecoderPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by Minor::Fetch2::evaluate(), GenericHtmFailureFault::invoke(), SparcISA::ISA::setMiscReg(), ArmISA::ISA::setMiscReg(), X86ISA::ISA::setThreadContext(), SimpleThread::takeOverFrom(), O3ThreadContext< Impl >::takeOverFrom(), and X86ISA::ISA::updateHandyM5Reg().

◆ getDTBPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by RiscvISA::RemoteGDB::acc(), X86ISA::RemoteGDB::acc(), X86ISA::copyMiscRegs(), ArmISA::copyRegs(), BaseKvmCPU::doMMIOAccess(), BaseCPU::flushTLBs(), SparcISA::FastDataAccessMMUMiss::invoke(), X86ISA::PageFault::invoke(), Trace::TarmacParserRecord::readMemNoEffect(), Minor::LSQ::SplitDataRequest::sendNextFragmentToTranslation(), X86ISA::ISA::setMiscReg(), Minor::LSQ::SingleDataRequest::startAddrTranslation(), BaseCPU::takeOverFrom(), Trace::TarmacTracerRecordV8::TraceInstEntryV8::TraceInstEntryV8(), Trace::TarmacTracerRecordV8::TraceMemEntryV8::TraceMemEntryV8(), RiscvISA::TLB::translateFunctional(), TranslatingPortProxy::tryTLBsOnce(), and tryTranslate().

◆ getHtmCheckpointPtr()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by SimpleExecContext::getHtmTransactionUid(), GenericHtmFailureFault::invoke(), and SimpleExecContext::newHtmTransactionUid().

◆ getIsaPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by MiscRegOp64::checkEL2Trap(), ArmISA::ArmStaticInst::getCurSveVecLenInBits(), ArmISA::ISA::getSelfDebug(), ArmISA::mcrMrc15TrapToHyp(), BaseCPU::registerThreadContexts(), ArmISA::snsBankedIndex64(), and BaseCPU::takeOverFrom().

◆ getITBPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by X86ISA::copyMiscRegs(), ArmISA::copyRegs(), SparcISA::TLB::doMmuRegRead(), SparcISA::TLB::doMmuRegWrite(), BaseCPU::flushTLBs(), SparcISA::TLB::GetTsbPtr(), SparcISA::FastInstructionAccessMMUMiss::invoke(), X86ISA::PageFault::invoke(), X86ISA::ISA::setMiscReg(), BaseCPU::takeOverFrom(), and tryTranslate().

◆ getPhysProxy()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by SparcISA::TLB::translateFunctional().

◆ getProcessPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by _llseekFunc(), PowerISA::RemoteGDB::acc(), SparcISA::RemoteGDB::acc(), MipsISA::RemoteGDB::acc(), RiscvISA::RemoteGDB::acc(), X86ISA::RemoteGDB::acc(), ArmISA::RemoteGDB::acc(), acceptFunc(), accessFunc(), bindFunc(), brkFunc(), chdirFunc(), chmodFunc(), chownFunc(), cloneFunc(), closeFunc(), connectFunc(), dup2Func(), dupFunc(), eventfdFunc(), execveFunc(), exitImpl(), fallocateFunc(), fchmodFunc(), fchownFunc(), fcntl64Func(), fcntlFunc(), SETranslatingPortProxy::fixupAddr(), fstat64Func(), fstatat64Func(), fstatfsFunc(), fstatFunc(), ftruncate64Func(), ftruncateFunc(), futexFunc(), getcwdFunc(), getegidFunc(), geteuidFunc(), getgidFunc(), getpeernameFunc(), getpgrpFunc(), getpidFunc(), getppidFunc(), getsocknameFunc(), getsockoptFunc(), gettidFunc(), getuidFunc(), GenericPageTableFault::invoke(), SparcISA::FastInstructionAccessMMUMiss::invoke(), SparcISA::FastDataAccessMMUMiss::invoke(), SparcISA::SpillNNormal::invoke(), SparcISA::FillNNormal::invoke(), SparcISA::TrapInstruction::invoke(), X86ISA::PageFault::invoke(), ioctlFunc(), X86ISA::GpuTLB::issueTLBLookup(), linkFunc(), listenFunc(), lseekFunc(), lstat64Func(), lstatFunc(), X86ISA::m5PageFault(), mkdirFunc(), mknodFunc(), HSADriver::mmap(), Shader::mmap(), mmapFunc(), mremapFunc(), munmapFunc(), HSADriver::open(), openatFunc(), pipe2Func(), pollFunc(), pread64Func(), pwrite64Func(), readFunc(), readlinkFunc(), readvFunc(), recvfromFunc(), X86ISA::GpuTLB::CpuSidePort::recvFunctional(), recvmsgFunc(), BaseCPU::registerThreadContexts(), renameFunc(), rmdirFunc(), selectFunc(), sendmsgFunc(), ComputeUnit::sendRequest(), sendtoFunc(), setpgidFunc(), setsockoptFunc(), setThreadArea32Func(), setTidAddressFunc(), shutdownFunc(), socketFunc(), socketpairFunc(), stat64Func(), statfsFunc(), statFunc(), symlinkFunc(), sysinfoFunc(), takeOverFrom(), tgkillFunc(), X86ISA::TLB::translate(), RiscvISA::TLB::translate(), X86ISA::GpuTLB::translate(), MipsISA::TLB::translateAtomic(), PowerISA::TLB::translateData(), MipsISA::TLB::translateFunctional(), RiscvISA::TLB::translateFunctional(), X86ISA::TLB::translateFunctional(), PowerISA::TLB::translateFunctional(), SparcISA::TLB::translateFunctional(), PowerISA::TLB::translateInst(), ArmISA::TLB::translateSe(), X86ISA::GpuTLB::translationReturn(), truncate64Func(), truncateFunc(), SparcISA::unameFunc(), unameFunc(), unameFunc32(), unameFunc64(), unlinkFunc(), utimesFunc(), wait4Func(), writeFunc(), and writevFunc().

◆ getSystemPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by _llseekFunc(), PseudoInst::addsymbol(), PseudoInst::arm(), ArmISA::TLBIOp::broadcast(), cloneFunc(), Linux::cpuOnline(), SparcISA::TLB::doMmuRegWrite(), BaseStackTrace::dump(), exitFutexWake(), exitImpl(), futexFunc(), ArmSemihosting::gatherHeapInfo(), ArmSystem::getArmSystem(), getcpuFunc(), getpagesizeFunc(), getrlimitFunc(), System::Threads::insert(), RiscvISA::Reset::invoke(), ArmISA::Reset::invoke(), PseudoInst::loadsymbol(), mmap2Func(), mmapFunc(), mremapFunc(), munmapFunc(), pollFunc(), ArmSemihosting::portProxy(), ArmISA::DumpStats::process(), quiesce(), quiesceTick(), PseudoInst::readfile(), ArmISA::ISA::readMiscReg(), selectFunc(), setpgidFunc(), takeOverFrom(), tgkillFunc(), DistIface::toggleSync(), wait4Func(), PseudoInst::wakeCPU(), PseudoInst::workbegin(), and PseudoInst::workend().

◆ getVirtProxy()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by _llseekFunc(), acceptFunc(), accessFunc(), PseudoInst::addsymbol(), archPrctlFunc(), bindFunc(), chdirFunc(), chmodFunc(), chownFunc(), cloneFunc(), connectFunc(), Linux::ThreadInfo::curTaskInfo(), Linux::ThreadInfo::curTaskMmFromTaskStruct(), Linux::ThreadInfo::curTaskNameFromTaskStruct(), Linux::ThreadInfo::curTaskPIDFromTaskStruct(), Linux::ThreadInfo::curTaskStartFromTaskStruct(), Linux::ThreadInfo::curTaskTGIDFromTaskStruct(), execveFunc(), exitFutexWake(), Sparc32Process::flushWindows(), Sparc64Process::flushWindows(), fstatat64Func(), futexFunc(), GuestABI::Argument< Aapcs32, Composite, typename std::enable_if< IsAapcs32Composite< Composite >::value >::type >::get(), Linux::ThreadInfo::get_data(), SparcISA::getArgument(), ArmISA::getArgument(), getcwdFunc(), gethostnameFunc(), getpeernameFunc(), SparcISA::getresuidFunc(), getsocknameFunc(), getsockoptFunc(), ArmLinuxProcess32::initState(), GPUComputeDriver::ioctl(), ioctlFunc(), linkFunc(), lstat64Func(), lstatFunc(), X86ISA::m5PageFault(), mkdirFunc(), mknodFunc(), openatFunc(), pipe2Func(), pollFunc(), ArmSemihosting::portProxy(), pread64Func(), Linux::printk(), pwrite64Func(), BaseRemoteGDB::read(), PseudoInst::readfile(), readFunc(), readlinkFunc(), Trace::TarmacParserRecord::readMemNoEffect(), readvFunc(), recvfromFunc(), recvmsgFunc(), renameFunc(), Process::replicatePage(), rmdirFunc(), sendmsgFunc(), sendtoFunc(), setsockoptFunc(), setThreadArea32Func(), setTLSFunc32(), socketpairFunc(), stat64Func(), statfsFunc(), statFunc(), symlinkFunc(), sysctlFunc(), timeFunc(), truncate64Func(), truncateFunc(), unlinkFunc(), utimesFunc(), wait4Func(), BaseRemoteGDB::write(), PseudoInst::writefile(), writeFunc(), and writevFunc().

◆ getWritableVecPredReg()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ getWritableVecPredRegFlat()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

◆ getWritableVecReg()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::RemoteGDB::AArch64GdbRegCache::setRegs(), and ArmV8KvmCPU::updateThreadContext().

◆ getWritableVecRegFlat()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

◆ halt()

|

pure virtual |

Set the status to Halted.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by exitImpl().

◆ htmAbortTransaction()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by GenericHtmFailureFault::invoke().

◆ initMemProxies()

|

pure virtual |

Initialise the physical and virtual port proxies and tie them to the data port of the CPU.

tc ThreadContext for the virtual-to-physical translation

Implemented in SimpleThread, and CheckerThreadContext< TC >.

Referenced by BaseKvmCPU::init(), and MinorCPU::init().

◆ instAddr()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by RiscvISA::RiscvFault::invoke(), BaseCPU::mwaitAtomic(), X86ISA::TLB::translate(), X86ISA::GpuTLB::translate(), Minor::Execute::tryPCEvents(), ArmV8KvmCPU::updateKvmState(), ArmKvmCPU::updateKvmStateCore(), and X86KvmCPU::updateKvmStateRegs().

◆ microPC()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

◆ nextInstAddr()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by Trace::ArmNativeTrace::check().

◆ pcState() [1/2]

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::ISA::addressTranslation(), ArmISA::ISA::addressTranslation64(), GenericISA::M5DebugFault::advancePC(), ArmISA::SoftwareStep::advanceSS(), MipsProcess::argsInit(), RiscvProcess::argsInit(), PowerProcess::argsInit(), ArmProcess::argsInit(), X86ISA::X86Process::argsInit(), Trace::SparcNativeTrace::check(), cloneFunc(), BaseRemoteGDB::cmd_async_cont(), BaseRemoteGDB::cmd_async_step(), BaseRemoteGDB::cmd_cont(), BaseRemoteGDB::cmd_step(), Minor::Execute::commit(), Minor::Execute::commitInst(), compare(), O3ThreadContext< Impl >::copyArchRegs(), PowerISA::copyRegs(), X86ISA::copyRegs(), RiscvISA::copyRegs(), ArmISA::copyRegs(), SparcISA::copyRegs(), MipsISA::copyRegs(), ArmISA::copyVecRegs(), SparcISA::doNormalFault(), SparcISA::doREDFault(), Minor::Execute::executeMemRefInst(), execveFunc(), PowerISA::RemoteGDB::PowerGdbRegCache::getRegs(), RiscvISA::RemoteGDB::RiscvGdbRegCache::getRegs(), SparcISA::RemoteGDB::SPARCGdbRegCache::getRegs(), MipsISA::RemoteGDB::MipsGdbRegCache::getRegs(), ArmISA::RemoteGDB::AArch32GdbRegCache::getRegs(), X86ISA::RemoteGDB::X86GdbRegCache::getRegs(), SparcISA::RemoteGDB::SPARC64GdbRegCache::getRegs(), ArmISA::RemoteGDB::AArch64GdbRegCache::getRegs(), X86ISA::RemoteGDB::AMD64GdbRegCache::getRegs(), SparcProcess::handleTrap(), X86ISA::FsWorkload::initState(), FullO3CPU< O3CPUImpl >::insertThread(), FaultBase::invoke(), X86ISA::X86FaultBase::invoke(), SparcISA::SparcFaultBase::invoke(), SESyscallFault::invoke(), ReExec::invoke(), MipsISA::MipsFaultBase::invoke(), X86ISA::X86Trap::invoke(), SparcISA::PowerOnReset::invoke(), SyscallRetryFault::invoke(), RiscvISA::RiscvFault::invoke(), RiscvISA::Reset::invoke(), MipsISA::ResetFault::invoke(), ArmISA::ArmFault::invoke(), SparcISA::SpillNNormal::invoke(), MipsISA::TlbFault< TlbInvalidFault >::invoke(), SparcISA::FillNNormal::invoke(), SparcISA::TrapInstruction::invoke(), X86ISA::PageFault::invoke(), ArmISA::Reset::invoke(), ArmISA::SupervisorCall::invoke(), X86ISA::InitInterrupt::invoke(), X86ISA::StartupInterrupt::invoke(), ArmISA::ArmFault::invoke64(), RiscvISA::RiscvFault::invokeSE(), RiscvISA::UnknownInstFault::invokeSE(), RiscvISA::IllegalInstFault::invokeSE(), RiscvISA::UnimplementedFault::invokeSE(), RiscvISA::IllegalFrmFault::invokeSE(), ioctlFunc(), mmapFunc(), SkipFuncBase::process(), PseudoInst::pseudoInstWork(), Trace::TarmacParserRecord::readMemNoEffect(), ArmISA::ISA::readMiscReg(), ArmISA::HTMCheckpoint::restore(), ArmISA::SkipFunc::returnFromFuncIn(), ArmISA::HTMCheckpoint::save(), serialize(), MipsISA::MipsFaultBase::setExceptionState(), RiscvISA::ISA::setMiscReg(), ArmISA::ISA::setMiscReg(), setNPC(), PowerISA::RemoteGDB::PowerGdbRegCache::setRegs(), SparcISA::RemoteGDB::SPARCGdbRegCache::setRegs(), RiscvISA::RemoteGDB::RiscvGdbRegCache::setRegs(), MipsISA::RemoteGDB::MipsGdbRegCache::setRegs(), ArmISA::RemoteGDB::AArch32GdbRegCache::setRegs(), X86ISA::RemoteGDB::X86GdbRegCache::setRegs(), SparcISA::RemoteGDB::SPARC64GdbRegCache::setRegs(), ArmISA::RemoteGDB::AArch64GdbRegCache::setRegs(), X86ISA::RemoteGDB::AMD64GdbRegCache::setRegs(), X86ISA::I386LinuxProcess::syscall(), Minor::Execute::takeInterrupt(), ArmISA::SelfDebug::testBreakPoints(), BaseRemoteGDB::trap(), Minor::Execute::tryPCEvents(), Minor::Execute::tryToBranch(), unserialize(), Trace::X86NativeTrace::ThreadState::update(), Trace::ArmNativeTrace::ThreadState::update(), ArmKvmCPU::updateTCStateCore(), ArmV8KvmCPU::updateThreadContext(), X86KvmCPU::updateThreadContextRegs(), and Minor::Fetch1::wakeupFetch().

◆ pcState() [2/2]

|

pure virtual |

Implemented in SimpleThread, and CheckerThreadContext< TC >.

◆ pcStateNoRecord()

|

pure virtual |

Implemented in SimpleThread, and CheckerThreadContext< TC >.

Referenced by ArmISA::SkipFunc::returnFromFuncIn(), and ArmISA::ISA::setMiscReg().

◆ quiesce()

| void ThreadContext::quiesce | ( | ) |

Quiesce thread context.

Definition at line 129 of file thread_context.cc.

References contextId(), getSystemPtr(), System::Threads::quiesce(), and System::threads.

Referenced by PseudoInst::quiesce(), and DistIface::toggleSync().

◆ quiesceTick()

| void ThreadContext::quiesceTick | ( | Tick | resume | ) |

Quiesce, suspend, and schedule activate at resume.

Definition at line 136 of file thread_context.cc.

References contextId(), getSystemPtr(), System::Threads::quiesceTick(), and System::threads.

Referenced by FreeBSD::onUDelay(), Linux::onUDelay(), PseudoInst::quiesceCycles(), PseudoInst::quiesceNs(), PseudoInst::quiesceSkip(), and DistIface::toggleSync().

◆ readCCReg()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by compare(), ArmISA::copyRegs(), X86ISA::getRFlags(), ArmISA::ArmFault::invoke(), ArmISA::ArmFault::invoke64(), ArmISA::ISA::readMiscReg(), Trace::ArmNativeTrace::ThreadState::update(), Trace::TarmacTracerRecord::TraceRegEntry::updateCC(), ArmV8KvmCPU::updateKvmState(), and Trace::TarmacTracerRecord::TraceRegEntry::updateMisc().

◆ readCCRegFlat()

Implemented in SimpleThread, CheckerThreadContext< TC >, Iris::ThreadContext, and FastModel::CortexA76TC.

Referenced by X86ISA::copyRegs(), and serialize().

◆ readFloatReg()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by compare(), PowerISA::copyRegs(), RiscvISA::copyRegs(), SparcISA::copyRegs(), PowerISA::RemoteGDB::PowerGdbRegCache::getRegs(), MipsISA::RemoteGDB::MipsGdbRegCache::getRegs(), MipsISA::readRegOtherThread(), Trace::X86NativeTrace::ThreadState::update(), Trace::TarmacTracerRecord::TraceRegEntry::updateFloat(), and updateKvmStateFPUCommon().

◆ readFloatRegFlat()

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by X86ISA::copyRegs(), ArmISA::copyRegs(), MipsISA::copyRegs(), serialize(), and ArmKvmCPU::updateKvmStateVFP().

◆ readFuncExeInst()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by O3ThreadContext< Impl >::copyArchRegs(), SimpleThread::copyState(), SimpleThread::takeOverFrom(), and O3ThreadContext< Impl >::takeOverFrom().

◆ readIntReg()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by PowerISA::BranchRegCond::branchTarget(), ArmSemihosting::call32(), ArmSemihosting::call64(), Trace::SparcNativeTrace::check(), compare(), PowerISA::copyRegs(), RiscvISA::copyRegs(), SparcISA::copyRegs(), SparcISA::doNormalFault(), SparcISA::doREDFault(), TimingExprReadIntReg::eval(), Sparc32Process::flushWindows(), Sparc64Process::flushWindows(), GuestABI::Argument< X86PseudoInstABI, uint64_t >::get(), GuestABI::Argument< ABI, Arg, typename std::enable_if< std::is_base_of< GenericSyscallABI64, ABI >::value &&std::is_integral< Arg >::value >::type >::get(), GuestABI::Argument< ABI, Arg, typename std::enable_if<!ABI::template IsWide< Arg >::value >::type >::get(), GuestABI::enable_if< std::is_integral< Integer >::value &&(sizeof(Integer)<=sizeof(uint32_t)) >::type >::get(), GuestABI::Argument< ABI, Arg, Enabled >::type >< Integer >::get(), GuestABI::enable_if< std::is_integral< Integer >::value &&(sizeof(Integer)<=8) >::type >::get(), GuestABI::Argument< Aapcs32, Composite, typename std::enable_if< IsAapcs32Composite< Composite >::value >::type >::get(), GuestABI::Argument< Aapcs64, Composite, typename std::enable_if< IsAapcs64Composite< Composite >::value &&!IsAapcs64Hxa< Composite >::value >::type >::get(), SparcISA::getArgument(), X86ISA::getArgument(), ArmISA::getArgument(), RiscvISA::getArgument(), PowerISA::RemoteGDB::PowerGdbRegCache::getRegs(), RiscvISA::RemoteGDB::RiscvGdbRegCache::getRegs(), SparcISA::RemoteGDB::SPARCGdbRegCache::getRegs(), MipsISA::RemoteGDB::MipsGdbRegCache::getRegs(), ArmISA::RemoteGDB::AArch32GdbRegCache::getRegs(), X86ISA::RemoteGDB::X86GdbRegCache::getRegs(), SparcISA::RemoteGDB::SPARC64GdbRegCache::getRegs(), ArmISA::RemoteGDB::AArch64GdbRegCache::getRegs(), X86ISA::RemoteGDB::AMD64GdbRegCache::getRegs(), ArmISA::DumpStats::getTaskDetails(), ArmISA::DumpStats64::getTaskDetails(), ArmISA::ArmFault::invoke(), GenericSyscallABI32::mergeRegs(), GuestABI::Result< Aapcs32, Composite, typename std::enable_if< IsAapcs32Composite< Composite >::value >::type >::prepare(), ArmISA::ISA::readMiscReg(), MipsISA::readRegOtherThread(), ArmISA::SkipFunc::returnFromFuncIn(), ArmISA::HTMCheckpoint::save(), GuestABI::Result< PowerProcess::SyscallABI, SyscallReturn >::store(), GuestABI::Result< ABI, SyscallReturn, typename std::enable_if< std::is_base_of< SparcProcess::SyscallABI, ABI >::value >::type >::store(), GuestABI::Result< Aapcs64, Composite, typename std::enable_if< IsAapcs64Composite< Composite >::value &&!IsAapcs64Hxa< Composite >::value >::type >::store(), PowerLinuxProcess::syscall(), SparcISA::SparcSolarisProcess::syscall(), MipsLinuxProcess::syscall(), RiscvLinuxProcess64::syscall(), X86ISA::X86_64LinuxProcess::syscall(), SparcISA::Sparc32LinuxProcess::syscall(), X86ISA::I386LinuxProcess::syscall(), SparcISA::Sparc64LinuxProcess::syscall(), RiscvLinuxProcess32::syscall(), ArmFreebsdProcess32::syscall(), ArmLinuxProcess32::syscall(), ArmLinuxProcess64::syscall(), ArmFreebsdProcess64::syscall(), Trace::X86NativeTrace::ThreadState::update(), Trace::ArmNativeTrace::ThreadState::update(), Trace::TarmacTracerRecord::TraceRegEntry::updateInt(), and ArmV8KvmCPU::updateKvmState().

◆ readIntRegFlat()

Flat register interfaces.

Some architectures have different registers visible in different modes. Such architectures "flatten" a register (see flattenRegId()) to map it into the gem5 register file. This interface provides a flat interface to the underlying register file, which allows for example serialization code to access all registers.

Implemented in SimpleThread, CheckerThreadContext< TC >, Iris::ThreadContext, and FastModel::CortexA76TC.

Referenced by X86ISA::copyRegs(), ArmISA::copyRegs(), MipsISA::copyRegs(), FastModel::CortexA76TC::readIntRegFlat(), serialize(), and ArmKvmCPU::updateKvmStateCore().

◆ readLastActivate()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by PseudoInst::quiesceTime().

◆ readLastSuspend()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by PseudoInst::quiesceTime().

◆ readMiscReg()

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by ArmISA::AArch32isUndefinedGenericTimer(), RiscvISA::RemoteGDB::acc(), ArmISA::addPAC(), ArmISA::addPACDA(), ArmISA::addPACDB(), ArmISA::addPACGA(), ArmISA::addPACIA(), ArmISA::addPACIB(), ArmISA::VectorCatch::addressMatching(), ArmProcess64::armHwcapImpl(), ArmISA::authDA(), ArmISA::authDB(), ArmISA::authIA(), ArmISA::authIB(), MipsISA::MipsFaultBase::base(), ArmISA::calculateBottomPACBit(), ArmISA::calculateTBI(), ArmISA::canReadAArch64SysReg(), ArmISA::canWriteAArch64SysReg(), ArmISA::ArmStaticInst::checkAdvSIMDOrFPEnabled32(), MiscRegOp64::checkEL1Trap(), MiscRegOp64::checkEL2Trap(), MiscRegOp64::checkEL3Trap(), ArmISA::ArmStaticInst::checkFPAdvSIMDTrap64(), ArmISA::Interrupts::checkInterrupts(), ArmISA::TLB::checkPAN(), ArmISA::ArmStaticInst::checkSveEnabled(), ArmISA::computeAddrTop(), ArmISA::condGenericTimerCommonEL0SystemAccessTrapEL2(), ArmISA::condGenericTimerCommonEL1SystemAccessTrapEL2(), ArmISA::condGenericTimerPhysEL1SystemAccessTrapEL2(), ArmISA::condGenericTimerPhysHypTrap(), ArmISA::condGenericTimerSystemAccessTrapEL1(), X86ISA::copyMiscRegs(), ArmISA::debugTargetFrom(), SparcISA::TLB::doMmuRegRead(), SparcISA::TLB::doMmuRegWrite(), RiscvISA::TLB::doTranslate(), ArmKvmCPU::dumpKvmStateCoProc(), ArmISA::PrefetchAbort::ec(), ArmISA::DataAbort::ec(), ArmISA::EL2Enabled(), ArmISA::ELIsInHost(), ArmISA::ELStateUsingAArch32K(), ArmISA::VectorCatch::exceptionTrapping(), MiscRegImplDefined64::execute(), Sparc32Process::flushWindows(), Sparc64Process::flushWindows(), SparcISA::RemoteGDB::gdbRegs(), ArmISA::ArmStaticInst::generalExceptionsToAArch64(), ArmISA::BrkPoint::getAddrfromReg(), ArmISA::WatchPoint::getAddrfromReg(), ArmISA::BrkPoint::getContextfromReg(), ArmISA::BrkPoint::getControlReg(), ArmISA::getExecutingAsid(), ArmISA::Interrupts::getInterrupt(), RiscvISA::TLB::getMemPriv(), SparcISA::RemoteGDB::SPARCGdbRegCache::getRegs(), SparcISA::RemoteGDB::SPARC64GdbRegCache::getRegs(), ArmISA::getRestoredITBits(), ArmISA::ArmFault::getVector(), ArmISA::Reset::getVector(), ArmISA::ArmFault::getVector64(), ArmISA::VectorCatch::getVectorBase(), ArmISA::BrkPoint::getVMIDfromReg(), RiscvISA::Interrupts::globalMask(), ArmISA::HavePACExt(), ArmISA::HaveSecureEL2Ext(), ArmISA::HaveVirtHostExt(), ArmISA::illegalExceptionReturn(), ArmISA::inAArch64(), ArmISA::SelfDebug::init(), ArmProcess32::initState(), ArmProcess64::initState(), MipsISA::inUserMode(), RiscvISA::RiscvFault::invoke(), RiscvISA::Reset::invoke(), MipsISA::CoprocessorUnusableFault::invoke(), ArmISA::ArmFault::invoke(), ArmISA::Reset::invoke(), X86ISA::InitInterrupt::invoke(), X86ISA::StartupInterrupt::invoke(), ArmISA::AbortFault< DataAbort >::invoke(), ArmISA::ArmFault::invoke64(), ArmISA::SelfDebug::isDebugEnabled(), ArmISA::SelfDebug::isDebugEnabledForEL32(), ArmISA::isGenericTimerCommonEL0HypTrap(), ArmISA::isGenericTimerCommonEL0SystemAccessTrapEL2(), ArmISA::isGenericTimerPhysEL0SystemAccessTrapEL2(), ArmISA::isGenericTimerPhysEL1SystemAccessTrapEL2(), ArmISA::isGenericTimerSystemAccessTrapEL1(), ArmISA::isGenericTimerSystemAccessTrapEL3(), ArmISA::isGenericTimerVirtSystemAccessTrapEL2(), ArmISA::isSecure(), ArmISA::isSecureBelowEL3(), ArmISA::IsSecureEL2Enabled(), ArmISA::isUnpriviledgeAccess(), ArmISA::ArmStaticInst::isWFxTrapping(), X86KvmCPU::kvmRunWrapper(), ArmISA::longDescFormatInUse(), X86ISA::m5PageFault(), ArmISA::mcrMrc15TrapToHyp(), ArmISA::mcrrMrrc15TrapToHyp(), ArmISA::TableWalker::memAttrs(), ArmISA::TableWalker::memAttrsAArch64(), ArmISA::TableWalker::memAttrsLPAE(), ArmISA::ArmFaultVals< FastInterrupt >::offset(), MipsISA::TlbRefillFault::offset(), ArmISA::TLBIALL::operator()(), ArmISA::TLBIASID::operator()(), ArmISA::TLBIMVAA::operator()(), ArmISA::TLBIMVA::operator()(), ArmISA::TableWalker::processWalk(), ArmISA::TableWalker::processWalkAArch64(), ArmISA::TableWalker::processWalkLPAE(), ArmISA::purifyTaggedAddr(), ArmISA::readMPIDR(), MipsISA::readRegOtherThread(), ArmISA::s1TranslationRegime(), ArmISA::HTMCheckpoint::save(), ArmISA::sendEvent(), Iris::Interrupts::serialize(), MipsISA::MipsFaultBase::setExceptionState(), ArmISA::ISA::setMiscReg(), MipsISA::TlbFault< TlbInvalidFault >::setTlbExceptionState(), ArmISA::snsBankedIndex(), ArmISA::snsBankedIndex64(), ArmISA::ArmStaticInst::softwareBreakpoint32(), ArmISA::SPAlignmentCheckEnabled(), ArmV8KvmCPU::startup(), ArmISA::stripPAC(), ArmISA::Interrupts::takeInt(), ArmISA::WatchPoint::test(), ArmISA::BrkPoint::testAddrMatch(), ArmISA::BrkPoint::testAddrMissMatch(), ArmISA::BrkPoint::testContextMatch(), ArmISA::BrkPoint::testVMIDMatch(), RiscvISA::TLB::translate(), RiscvISA::TLB::translateFunctional(), ArmISA::TLB::translateMmuOff(), Trace::ArmNativeTrace::ThreadState::update(), ArmISA::ArmFault::update(), ArmV8KvmCPU::updateKvmState(), ArmKvmCPU::updateKvmStateCore(), updateKvmStateFPUCommon(), X86KvmCPU::updateKvmStateMSRs(), X86KvmCPU::updateKvmStateRegs(), X86KvmCPU::updateKvmStateSRegs(), ArmKvmCPU::updateKvmStateVFP(), ArmISA::TLB::updateMiscReg(), ArmISA::upperAndLowerRange(), and ArmISA::TableWalker::walk().

◆ readMiscRegNoEffect()

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by ArmISA::AbortFault< DataAbort >::abortDisable(), ArmISA::Interrupt::abortDisable(), ArmISA::FastInterrupt::abortDisable(), archPrctlFunc(), MipsISA::Interrupts::checkInterrupts(), SparcISA::Interrupts::checkInterrupts(), ArmISA::ArmStaticInst::checkSETENDEnabled(), compare(), ArmISA::condGenericTimerCommonEL1SystemAccessTrapEL2(), SparcISA::copyMiscRegs(), X86ISA::copyMiscRegs(), ArmISA::copyRegs(), SparcISA::copyRegs(), MipsISA::copyRegs(), ArmISA::currOpMode(), ArmISA::debugTargetFrom(), SparcISA::doNormalFault(), SparcISA::doREDFault(), ArmKvmCPU::dumpKvmStateCoProc(), SparcISA::enterREDState(), X86ISA::TLB::finalizePhysical(), ArmISA::FastInterrupt::fiqDisable(), X86ISA::RemoteGDB::gdbRegs(), MipsISA::getCauseIP(), SparcISA::getExecutingAsid(), SparcISA::getHyperVector(), MipsISA::Interrupts::getInterrupt(), SparcISA::Interrupts::getInterrupt(), SparcISA::getPrivVector(), MipsISA::RemoteGDB::MipsGdbRegCache::getRegs(), ArmISA::RemoteGDB::AArch32GdbRegCache::getRegs(), X86ISA::RemoteGDB::X86GdbRegCache::getRegs(), ArmISA::RemoteGDB::AArch64GdbRegCache::getRegs(), X86ISA::RemoteGDB::AMD64GdbRegCache::getRegs(), X86ISA::getRFlags(), ArmISA::ArmFault::getVector(), ArmISA::Reset::getVector(), X86KvmCPU::handleIOMiscReg32(), X86KvmCPU::handleKvmExitIO(), ArmISA::SelfDebug::init(), X86ISA::FsWorkload::initState(), MipsISA::Interrupts::interruptsPending(), SparcISA::inUserMode(), X86ISA::inUserMode(), ArmISA::inUserMode(), SparcISA::SparcFaultBase::invoke(), X86ISA::X86FaultBase::invoke(), SparcISA::PowerOnReset::invoke(), MipsISA::ResetFault::invoke(), SparcISA::FastInstructionAccessMMUMiss::invoke(), ArmISA::ArmFault::invoke(), SparcISA::FastDataAccessMMUMiss::invoke(), X86ISA::PageFault::invoke(), ArmISA::VirtualDataAbort::invoke(), ArmISA::isBigEndian64(), MipsISA::InterruptFault::offset(), MipsISA::Interrupts::onCpuTimerInterrupt(), X86ISA::GpuTLB::pagingProtectionChecks(), ArmISA::UndefinedInstruction::routeToHyp(), ArmISA::SupervisorCall::routeToHyp(), ArmISA::SupervisorTrap::routeToHyp(), ArmISA::PrefetchAbort::routeToHyp(), ArmISA::DataAbort::routeToHyp(), ArmISA::Interrupt::routeToHyp(), ArmISA::FastInterrupt::routeToHyp(), ArmISA::PCAlignmentFault::routeToHyp(), ArmISA::SPAlignmentFault::routeToHyp(), ArmISA::SystemError::routeToHyp(), ArmISA::SoftwareBreakpoint::routeToHyp(), ArmISA::HardwareBreakpoint::routeToHyp(), ArmISA::Watchpoint::routeToHyp(), ArmISA::SoftwareStepFault::routeToHyp(), ArmISA::IllegalInstSetStateFault::routeToHyp(), ArmISA::PrefetchAbort::routeToMonitor(), ArmISA::DataAbort::routeToMonitor(), ArmISA::Interrupt::routeToMonitor(), ArmISA::FastInterrupt::routeToMonitor(), ArmISA::SystemError::routeToMonitor(), Iris::ISA::serialize(), Iris::Interrupts::serialize(), MipsISA::setCauseIP(), setKvmDTableReg(), setKvmSegmentReg(), ArmISA::ISA::setMiscReg(), X86ISA::RemoteGDB::X86GdbRegCache::setRegs(), X86ISA::RemoteGDB::AMD64GdbRegCache::setRegs(), GuestABI::Result< ABI, SyscallReturn, typename std::enable_if< std::is_base_of< SparcProcess::SyscallABI, ABI >::value >::type >::store(), X86ISA::GpuTLB::tlbLookup(), X86ISA::TLB::translate(), X86ISA::GpuTLB::translate(), SparcISA::TLB::translateData(), SparcISA::TLB::translateFunctional(), SparcISA::TLB::translateInst(), X86ISA::TLB::translateInt(), X86ISA::GpuTLB::translateInt(), Trace::ArmNativeTrace::ThreadState::update(), ArmISA::ArmFault::update(), Trace::TarmacTracerRecord::TraceRegEntry::updateInt(), ArmKvmCPU::updateKvmStateCoProc(), updateKvmStateFPUCommon(), X86KvmCPU::updateKvmStateFPULegacy(), X86KvmCPU::updateKvmStateFPUXSave(), Trace::TarmacTracerRecord::TraceRegEntry::updateMisc(), and ArmKvmCPU::updateTCStateCore().

◆ readStCondFailures()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

◆ readVec16BitLaneReg()

|

pure virtual |

Reads source vector 16bit operand.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ readVec32BitLaneReg()

|

pure virtual |

Reads source vector 32bit operand.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ readVec64BitLaneReg()

|

pure virtual |

Reads source vector 64bit operand.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ readVec8BitLaneReg()

|

pure virtual |

Vector Register Lane Interfaces.

Reads source vector 8bit operand.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ readVecElem()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ readVecElemFlat()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::copyVecRegs().

◆ readVecPredReg()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by compare(), ArmISA::HTMCheckpoint::save(), and Trace::TarmacTracerRecordV8::TraceRegEntryV8::updatePred().

◆ readVecPredRegFlat()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by serialize().

◆ readVecReg()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by compare(), GuestABI::Argument< Aapcs32Vfp, Float, typename std::enable_if< std::is_floating_point< Float >::value >::type >::get(), GuestABI::Argument< Aapcs32Vfp, HA, typename std::enable_if< IsAapcs32HomogeneousAggregate< HA >::value >::type >::get(), ArmISA::RemoteGDB::AArch64GdbRegCache::getRegs(), ArmISA::HTMCheckpoint::save(), GuestABI::Result< Aapcs32Vfp, Float, typename std::enable_if< std::is_floating_point< Float >::value >::type >::store(), GuestABI::Result< Aapcs32Vfp, HA, typename std::enable_if< IsAapcs32HomogeneousAggregate< HA >::value >::type >::store(), Trace::ArmNativeTrace::ThreadState::update(), ArmV8KvmCPU::updateKvmState(), and Trace::TarmacTracerRecordV8::TraceRegEntryV8::updateVec().

◆ readVecRegFlat()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by ArmISA::copyVecRegs(), and serialize().

◆ regStats()

|

inlinevirtual |

Reimplemented in Iris::ThreadContext, and CheckerThreadContext< TC >.

Definition at line 183 of file thread_context.hh.

Referenced by CheckerThreadContext< TC >::regStats().

◆ scheduleInstCountEvent()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ElasticTrace::regProbeListeners(), and BaseRemoteGDB::scheduleInstCommitEvent().

◆ setCCReg()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::copyRegs(), ArmISA::ISA::setMiscReg(), X86ISA::setRFlags(), GuestABI::Result< ABI, SyscallReturn, typename std::enable_if< std::is_base_of< ArmFreebsdProcessBits::SyscallABI, ABI >::value >::type >::store(), and ArmV8KvmCPU::updateThreadContext().

◆ setCCRegFlat()

Implemented in SimpleThread, CheckerThreadContext< TC >, Iris::ThreadContext, and FastModel::CortexA76TC.

Referenced by X86ISA::copyRegs(), and unserialize().

◆ setContextId()

|

pure virtual |

Implemented in Iris::ThreadContext, SimpleThread, and CheckerThreadContext< TC >.

Referenced by BaseCPU::registerThreadContexts(), and takeOverFrom().

◆ setFloatReg()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by PowerISA::copyRegs(), RiscvISA::copyRegs(), SparcISA::copyRegs(), MipsISA::setRegOtherThread(), PowerISA::RemoteGDB::PowerGdbRegCache::setRegs(), MipsISA::RemoteGDB::MipsGdbRegCache::setRegs(), and updateThreadContextFPUCommon().

◆ setFloatRegFlat()

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by X86ISA::copyRegs(), ArmISA::copyRegs(), MipsISA::copyRegs(), unserialize(), and ArmKvmCPU::updateTCStateVFP().

◆ setHtmCheckpointPtr()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by ArmISA::ISA::startup().

◆ setIntReg()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by X86Linux::archClone(), RiscvLinux64::archClone(), SparcLinux::archClone(), ArmLinux32::archClone(), RiscvLinux32::archClone(), ArmLinux64::archClone(), RiscvProcess::argsInit(), MipsProcess::argsInit(), PowerProcess::argsInit(), ArmProcess::argsInit(), X86ISA::X86Process::argsInit(), cloneFunc(), PowerISA::copyRegs(), RiscvISA::copyRegs(), SparcISA::copyRegs(), Sparc32Process::flushWindows(), Sparc64Process::flushWindows(), SparcProcess::initState(), X86ISA::X86FaultBase::invoke(), ArmISA::ArmFault::invoke(), X86ISA::InitInterrupt::invoke(), ArmISA::HTMCheckpoint::restore(), ArmISA::ISA::setMiscReg(), MipsISA::setRegOtherThread(), PowerISA::RemoteGDB::PowerGdbRegCache::setRegs(), SparcISA::RemoteGDB::SPARCGdbRegCache::setRegs(), RiscvISA::RemoteGDB::RiscvGdbRegCache::setRegs(), MipsISA::RemoteGDB::MipsGdbRegCache::setRegs(), ArmISA::RemoteGDB::AArch32GdbRegCache::setRegs(), X86ISA::RemoteGDB::X86GdbRegCache::setRegs(), SparcISA::RemoteGDB::SPARC64GdbRegCache::setRegs(), ArmISA::RemoteGDB::AArch64GdbRegCache::setRegs(), X86ISA::RemoteGDB::AMD64GdbRegCache::setRegs(), GuestABI::Result< X86PseudoInstABI, T >::store(), GuestABI::Result< ABI, SyscallReturn, typename std::enable_if< std::is_base_of< ArmFreebsdProcessBits::SyscallABI, ABI >::value >::type >::store(), GuestABI::Result< ABI, SyscallReturn, typename std::enable_if< std::is_base_of< ArmLinuxProcessBits::SyscallABI, ABI >::value >::type >::store(), GuestABI::Result< MipsProcess::SyscallABI, SyscallReturn >::store(), GuestABI::Result< PowerProcess::SyscallABI, SyscallReturn >::store(), GuestABI::Result< RiscvProcess::SyscallABI, SyscallReturn >::store(), GuestABI::Result< ABI, SyscallReturn, typename std::enable_if< std::is_base_of< X86Linux::SyscallABI, ABI >::value >::type >::store(), GuestABI::Result< ABI, SyscallReturn, typename std::enable_if< std::is_base_of< SparcProcess::SyscallABI, ABI >::value >::type >::store(), GuestABI::enable_if< std::is_integral< Integer >::value &&(sizeof(Integer)< sizeof(uint32_t)) >::type >::store(), GuestABI::Result< Aapcs32, Integer, typename std::enable_if< std::is_integral< Integer >::value &&(sizeof(Integer)==sizeof(uint32_t)) >::type >::store(), GuestABI::Result< Aapcs32, Integer, typename std::enable_if< std::is_integral< Integer >::value &&(sizeof(Integer)==sizeof(uint64_t)) >::type >::store(), GuestABI::enable_if< std::is_integral< Integer >::value &&(sizeof(Integer)<=8) >::type >::store(), GuestABI::Result< ABI, Ret, Enabled >::type >< Integer >::store(), GuestABI::Result< Aapcs32, Composite, typename std::enable_if< IsAapcs32Composite< Composite >::value >::type >::store(), GuestABI::Result< Aapcs64, Composite, typename std::enable_if< IsAapcs64Composite< Composite >::value &&!IsAapcs64Hxa< Composite >::value >::type >::store(), GuestABI::Result< ArmSemihosting::Abi32, ArmSemihosting::RetErrno >::store(), GuestABI::Result< ArmSemihosting::Abi64, ArmSemihosting::RetErrno >::store(), and ArmV8KvmCPU::updateThreadContext().

◆ setIntRegFlat()

Implemented in Iris::ThreadContext, SimpleThread, CheckerThreadContext< TC >, and FastModel::CortexA76TC.

Referenced by X86ISA::copyRegs(), ArmISA::copyRegs(), MipsISA::copyRegs(), FastModel::CortexA76TC::setIntRegFlat(), unserialize(), ArmKvmCPU::updateTCStateCore(), and ArmV8KvmCPU::updateThreadContext().

◆ setMiscReg()

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by ArmLinux::archClone(), SparcLinux::archClone(), SparcISA::copyMiscRegs(), X86ISA::copyMiscRegs(), ArmISA::copyRegs(), SparcISA::copyRegs(), SparcISA::TLB::doMmuRegWrite(), SparcISA::doNormalFault(), SparcISA::doREDFault(), SparcISA::enterREDState(), Sparc32Process::flushWindows(), Sparc64Process::flushWindows(), X86KvmCPU::handleIOMiscReg32(), SparcProcess::initState(), ArmProcess32::initState(), X86ISA::FsWorkload::initState(), ArmProcess64::initState(), X86ISA::X86_64Process::initState(), Sparc32Process::initState(), X86ISA::I386Process::initState(), Sparc64Process::initState(), X86ISA::installSegDesc(), SparcISA::PowerOnReset::invoke(), RiscvISA::RiscvFault::invoke(), RiscvISA::Reset::invoke(), MipsISA::ResetFault::invoke(), ArmISA::ArmFault::invoke(), X86ISA::PageFault::invoke(), ArmISA::Reset::invoke(), X86ISA::InitInterrupt::invoke(), X86ISA::StartupInterrupt::invoke(), ArmISA::AbortFault< DataAbort >::invoke(), ArmISA::PCAlignmentFault::invoke(), ArmISA::HardwareBreakpoint::invoke(), ArmISA::Watchpoint::invoke(), ArmISA::ArmSev::invoke(), ArmISA::ArmFault::invoke64(), X86KvmCPU::kvmRunWrapper(), ArmISA::HTMCheckpoint::restore(), Iris::Interrupts::serialize(), setContextSegment(), GenericTimer::setMiscReg(), ArmISA::ISA::setMiscReg(), MipsISA::setRegOtherThread(), ArmISA::RemoteGDB::AArch32GdbRegCache::setRegs(), X86ISA::RemoteGDB::X86GdbRegCache::setRegs(), X86ISA::RemoteGDB::AMD64GdbRegCache::setRegs(), X86ISA::setRFlags(), ArmISA::ArmFault::setSyndrome(), setTLSFunc32(), setTLSFunc64(), ArmKvmCPU::updateTCStateCore(), ArmKvmCPU::updateTCStateVFP(), ArmV8KvmCPU::updateThreadContext(), X86KvmCPU::updateThreadContext(), and X86KvmCPU::updateThreadContextMSRs().

◆ setMiscRegNoEffect()

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by X86Linux::archClone(), SparcLinux::archClone(), archPrctlFunc(), SparcISA::copyMiscRegs(), X86ISA::copyMiscRegs(), ArmISA::copyRegs(), MipsISA::copyRegs(), SparcISA::doNormalFault(), SparcISA::doREDFault(), SparcProcess::initState(), X86ISA::X86_64Process::initState(), X86ISA::I386Process::initState(), SparcISA::PowerOnReset::invoke(), MipsISA::CoprocessorUnusableFault::invoke(), MipsISA::AddressFault< TlbInvalidFault >::invoke(), ArmISA::ArmFault::invoke(), ArmISA::VirtualDataAbort::invoke(), MipsISA::setCauseIP(), MipsISA::MipsFaultBase::setExceptionState(), MipsISA::RemoteGDB::MipsGdbRegCache::setRegs(), ArmISA::RemoteGDB::AArch32GdbRegCache::setRegs(), ArmISA::RemoteGDB::AArch64GdbRegCache::setRegs(), setThreadAreaFunc(), MipsISA::TlbFault< TlbInvalidFault >::setTlbExceptionState(), ArmKvmCPU::updateTCStateCoProc(), ArmKvmCPU::updateTCStateCore(), ArmV8KvmCPU::updateThreadContext(), X86KvmCPU::updateThreadContextFPU(), updateThreadContextFPUCommon(), and X86KvmCPU::updateThreadContextXSave().

◆ setNPC()

|

inline |

Definition at line 263 of file thread_context.hh.

References pcState(), and X86ISA::val.

Referenced by execveFunc(), and CheckerThreadContext< TC >::setNPC().

◆ setProcessPtr()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by cloneFunc(), and execveFunc().

◆ setStatus()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by FullO3CPU< O3CPUImpl >::insertThread(), and takeOverFrom().

◆ setStCondFailures()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

◆ setThreadId()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by takeOverFrom().

◆ setVecElem()

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ setVecElemFlat()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::copyVecRegs().

◆ setVecLane() [1/4]

|

pure virtual |

Write a lane of the destination vector register.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ setVecLane() [2/4]

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ setVecLane() [3/4]

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ setVecLane() [4/4]

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

◆ setVecPredReg()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::HTMCheckpoint::restore().

◆ setVecPredRegFlat()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by unserialize().

◆ setVecReg()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by ArmISA::HTMCheckpoint::restore(), GuestABI::Result< Aapcs32Vfp, Float, typename std::enable_if< std::is_floating_point< Float >::value >::type >::store(), and GuestABI::Result< Aapcs32Vfp, HA, typename std::enable_if< IsAapcs32HomogeneousAggregate< HA >::value >::type >::store().

◆ setVecRegFlat()

|

pure virtual |

Implemented in SimpleThread, CheckerThreadContext< TC >, and Iris::ThreadContext.

Referenced by ArmISA::copyVecRegs(), and unserialize().

◆ socketId()

|

pure virtual |

◆ status()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by Minor::Execute::commitInst(), SimpleThread::copyState(), BaseKvmCPU::drainResume(), exitImpl(), Minor::Fetch1::getScheduledThread(), Minor::Execute::issue(), setpgidFunc(), takeOverFrom(), DistIface::toggleSync(), Minor::Execute::tryToBranch(), and PseudoInst::wakeCPU().

◆ suspend()

|

pure virtual |

Set the status to Suspended.

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by FutexMap::suspend_bitset().

◆ syscall()

|

pure virtual |

◆ takeOverFrom()

|

pure virtual |

Implemented in CheckerThreadContext< TC >, and SimpleThread.

Referenced by BaseCPU::takeOverFrom().

◆ threadId()

|

pure virtual |

Implemented in SimpleThread, Iris::ThreadContext, and CheckerThreadContext< TC >.

Referenced by cloneFunc(), SimpleThread::copyState(), ArmISA::getAff0(), ArmISA::Reset::invoke(), ArmISA::AbortFault< DataAbort >::invoke(), ArmISA::SystemError::invoke(), ArmISA::ArmSev::invoke(), RiscvISA::ISA::readMiscReg(), ArmISA::ISA::readMiscReg(), ArmISA::sendEvent(), RiscvISA::ISA::setMiscReg(), BaseCPU::takeOverFrom(), and takeOverFrom().

Member Data Documentation

◆ DefaultFloatResult

|

static |

Definition at line 43 of file guest_abi.test.cc.

Referenced by TEST().

◆ DefaultIntResult

|

static |

Definition at line 42 of file guest_abi.test.cc.

Referenced by TEST().

◆ floatResult

| double ThreadContext::floatResult = DefaultFloatResult |

Definition at line 46 of file guest_abi.test.cc.

Referenced by GuestABI::Result< TestABI_1D, Ret, typename std::enable_if< std::is_floating_point< Ret >::value >::type >::store(), GuestABI::Result< TestABI_2D, Ret, typename std::enable_if< std::is_floating_point< Ret >::value >::type >::store(), and TEST().

◆ floats

|

static |

Definition at line 40 of file guest_abi.test.cc.

Referenced by GuestABI::Argument< TestABI_1D, Arg, typename std::enable_if< std::is_floating_point< Arg >::value >::type >::get(), GuestABI::Argument< TestABI_2D, Arg, typename std::enable_if< std::is_floating_point< Arg >::value >::type >::get(), test2DVoid(), and testIntVoid().

◆ intOffset

| int ThreadContext::intOffset = 0 |

Definition at line 48 of file guest_abi.test.cc.

Referenced by TEST(), and testTcInit().

◆ intResult

| int ThreadContext::intResult = DefaultIntResult |

Definition at line 45 of file guest_abi.test.cc.

Referenced by GuestABI::Result< TestABI_1D, int >::store(), GuestABI::Result< TestABI_2D, int >::store(), and TEST().

◆ ints

|

static |

Definition at line 39 of file guest_abi.test.cc.

Referenced by GuestABI::Argument< TestABI_1D, int >::get(), GuestABI::Argument< TestABI_Prepare, int >::get(), GuestABI::Argument< TestABI_2D, int >::get(), GuestABI::Argument< TestABI_TcInit, int >::get(), test2DVoid(), testIntVoid(), testPrepareInt(), testPrepareVoid(), and testTcInit().

The documentation for this class was generated from the following files:

- cpu/thread_context.hh

- sim/guest_abi.test.cc

- cpu/thread_context.cc