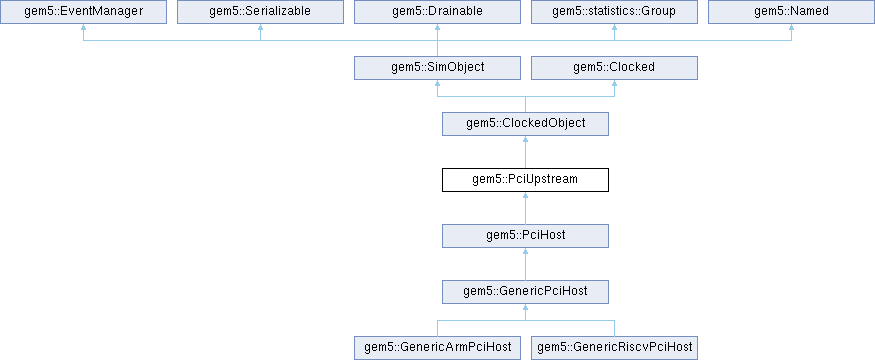

The PCI upstream describes any device (PCI host bridge, PCI-PCI bridge) that are connected upstream of PCI devices (endpoint or bridge). More...

#include <upstream.hh>

Classes | |

| class | DeviceInterface |

| Callback interface from PCI devices to the upstream. More... | |

Public Member Functions | |

| PARAMS (PciUpstream) | |

| PciUpstream (const Params &p) | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| void | sendBusChange () |

| Inform each PCI devices connected to this upstream of a bus number change. | |

Device interface | |

| virtual DeviceInterface | registerDevice (PciDevice *device, PciDevAddr dev_addr, PciIntPin pin) |

| Register a PCI device with the host. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| virtual AddrRange | getConfigAddrRange () const =0 |

| Get the range for the configuration memory space for which this PCI upstream is responsible. | |

| virtual PciBusNum | getBusNum () const =0 |

| Get the PCI bus number assign to that upstream. | |

| PciDevice * | getDevice (const PciDevAddr &addr) |

| Retrieve a PCI device from its bus address. | |

| const PciDevice * | getDevice (const PciDevAddr &addr) const |

| Retrieve a PCI device from its bus address. | |

PciUpstream controller interface | |

| virtual void | interfacePostInt (const PciDevAddr &dev_addr, PciIntPin pin)=0 |

| Post an interrupt to the CPU. | |

| virtual void | interfaceClearInt (const PciDevAddr &dev_addr, PciIntPin pin)=0 |

| Post an interrupt to the CPU. | |

| virtual AddrRange | interfaceConfigRange (const PciDevAddr &dev_addr) const =0 |

| Calculate the physical address range of the PCI device configuration space. | |

| virtual Addr | interfacePioAddr (const PciDevAddr &dev_addr, Addr pci_addr) const =0 |

| Calculate the physical address of an IO location on the PCI bus. | |

| virtual Addr | interfaceMemAddr (const PciDevAddr &dev_addr, Addr pci_addr) const =0 |

| Calculate the physical address of a non-prefetchable memory location in the PCI address space. | |

| virtual Addr | interfaceDmaAddr (const PciDevAddr &dev_addr, Addr pci_addr) const =0 |

| Calculate the physical address of a prefetchable memory location in the PCI address space. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Private Attributes | |

| std::map< PciDevAddr, PciDevice * > | devices |

| Currently registered PCI interfaces. | |

| PciUpDownBridge * | upToDown |

| The two one way bridges to connect both side buses. | |

| PciConfigError * | configErrorDevice |

Additional Inherited Members | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Detailed Description

The PCI upstream describes any device (PCI host bridge, PCI-PCI bridge) that are connected upstream of PCI devices (endpoint or bridge).

The PCI upstream controller has three main responsibilities:

- Bridge all packets between two buses (e.g. system and PCI bus)

- Map and deliver interrupts to the next upstream or CPU.

- Map memory addresses from the PCI bus's various memory spaces (Configuration, legacy IO, non-prefetchable memory, and prefetchable memory) to physical memory.

PCI devices need to register themselves with a PCI upstream using the PciUpstream::registerDevice() call. This call returns a PciUpstream::DeviceInterface that provides for common functionality such as interrupt delivery and memory mapping.

The PciUpstream is an abstract class that provides the device registering part and should be inherited by the actual upstream classes, which must provides implementation for the interrupts and memory mapping.

Definition at line 91 of file upstream.hh.

Constructor & Destructor Documentation

◆ PciUpstream()

| gem5::PciUpstream::PciUpstream | ( | const Params & | p | ) |

Definition at line 69 of file upstream.cc.

References gem5::ClockedObject::ClockedObject(), configErrorDevice, gem5::MipsISA::p, and upToDown.

Referenced by PARAMS(), gem5::PciHost::PciHost(), and registerDevice().

Member Function Documentation

◆ getBusNum()

|

protectedpure virtual |

Get the PCI bus number assign to that upstream.

Implemented in gem5::GenericPciHost.

References gem5::X86ISA::addr.

Referenced by registerDevice().

◆ getConfigAddrRange()

|

protectedpure virtual |

Get the range for the configuration memory space for which this PCI upstream is responsible.

The range should include the full configuration space even where no bus/device are present.

Implemented in gem5::GenericPciHost.

Referenced by init().

◆ getDevice() [1/2]

|

protected |

Retrieve a PCI device from its bus address.

- Returns

- Pointer to a PciDevice instance or nullptr if the device doesn't exist.

Definition at line 99 of file upstream.cc.

References gem5::X86ISA::addr, and devices.

Referenced by gem5::GenericPciHost::mapPciInterrupt().

◆ getDevice() [2/2]

|

protected |

Retrieve a PCI device from its bus address.

- Returns

- Pointer to a constant PciDevice instance or nullptr if the device doesn't exist.

Definition at line 106 of file upstream.cc.

References gem5::X86ISA::addr, and devices.

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Definition at line 76 of file upstream.cc.

References configErrorDevice, getConfigAddrRange(), sendBusChange(), and upToDown.

◆ interfaceClearInt()

|

protectedpure virtual |

Post an interrupt to the CPU.

- Parameters

-

dev_addr The device's position on the PCI bus pin PCI interrupt pin

Implemented in gem5::GenericPciHost.

◆ interfaceConfigRange()

|

protectedpure virtual |

Calculate the physical address range of the PCI device configuration space.

- Parameters

-

dev_addr The device's position on the PCI bus

- Returns

- Configuration address range in the system's physical address space.

Implemented in gem5::GenericPciHost.

◆ interfaceDmaAddr()

|

protectedpure virtual |

Calculate the physical address of a prefetchable memory location in the PCI address space.

- Parameters

-

dev_addr The device's position on the PCI bus pci_addr Address in the PCI DMA memory address space

- Returns

- Address in the system's physical address space.

Implemented in gem5::GenericPciHost.

◆ interfaceMemAddr()

|

protectedpure virtual |

Calculate the physical address of a non-prefetchable memory location in the PCI address space.

- Parameters

-

dev_addr The device's position on the PCI bus pci_addr Address in the PCI memory address space

- Returns

- Address in the system's physical address space.

Implemented in gem5::GenericPciHost.

◆ interfacePioAddr()

|

protectedpure virtual |

Calculate the physical address of an IO location on the PCI bus.

- Parameters

-

dev_addr The device's position on the PCI bus pci_addr Address in the PCI IO address space

- Returns

- Address in the system's physical address space.

Implemented in gem5::GenericPciHost.

◆ interfacePostInt()

|

protectedpure virtual |

Post an interrupt to the CPU.

- Parameters

-

dev_addr The device's position on the PCI bus pin PCI interrupt pin

Implemented in gem5::GenericPciHost.

◆ PARAMS()

| gem5::PciUpstream::PARAMS | ( | PciUpstream | ) |

References gem5::MipsISA::p, and PciUpstream().

◆ registerDevice()

|

virtual |

Register a PCI device with the host.

- Parameters

-

device Device to register dev_addr The device's position on the PCI bus pin Interrupt pin

- Returns

- A device-specific DeviceInterface instance.

Definition at line 84 of file upstream.cc.

References gem5::PciDevAddr::dev, devices, DPRINTF, fatal_if, gem5::PciDevAddr::func, getBusNum(), and PciUpstream().

◆ sendBusChange()

| void gem5::PciUpstream::sendBusChange | ( | ) |

Inform each PCI devices connected to this upstream of a bus number change.

Definition at line 142 of file upstream.cc.

References devices.

Referenced by init().

Member Data Documentation

◆ configErrorDevice

|

private |

Definition at line 325 of file upstream.hh.

Referenced by init(), and PciUpstream().

◆ devices

|

private |

Currently registered PCI interfaces.

Definition at line 320 of file upstream.hh.

Referenced by getDevice(), getDevice(), registerDevice(), and sendBusChange().

◆ upToDown

|

private |

The two one way bridges to connect both side buses.

Definition at line 323 of file upstream.hh.

Referenced by init(), and PciUpstream().

The documentation for this class was generated from the following files:

- dev/pci/upstream.hh

- dev/pci/upstream.cc

Generated on Mon Oct 27 2025 04:13:12 for gem5 by doxygen 1.14.0