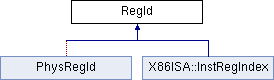

Register ID: describe an architectural register with its class and index. More...

#include <reg_class.hh>

Public Member Functions | |

| RegId () | |

| RegId (RegClass reg_class, RegIndex reg_idx) | |

| RegId (RegClass reg_class, RegIndex reg_idx, ElemIndex elem_idx) | |

| bool | operator== (const RegId &that) const |

| bool | operator!= (const RegId &that) const |

| bool | operator< (const RegId &that) const |

| Order operator. More... | |

| bool | isRenameable () const |

| Return true if this register can be renamed. More... | |

| bool | isZeroReg () const |

| Check if this is the zero register. More... | |

| bool | isIntReg () const |

| bool | isFloatReg () const |

| bool | isVecReg () const |

| true if it is a condition-code physical register. More... | |

| bool | isVecElem () const |

| true if it is a condition-code physical register. More... | |

| bool | isVecPredReg () const |

| true if it is a predicate physical register. More... | |

| bool | isCCReg () const |

| true if it is a condition-code physical register. More... | |

| bool | isMiscReg () const |

| true if it is a condition-code physical register. More... | |

| bool | isRenameable () |

| Return true if this register can be renamed. More... | |

| const RegIndex & | elemIndex () const |

| Elem accessor. More... | |

| const RegClass & | classValue () const |

| Class accessor. More... | |

| const char * | className () const |

| Return a const char* with the register class name. More... | |

| int | getNumPinnedWrites () const |

| void | setNumPinnedWrites (int num_writes) |

| const RegIndex & | index () const |

| Index accessors. More... | |

| RegIndex & | index () |

| RegIndex | flatIndex () const |

| Index flattening. More... | |

Protected Attributes | |

| RegClass | regClass |

| RegIndex | regIdx |

| ElemIndex | elemIdx |

| int | numPinnedWrites |

Static Protected Attributes | |

| static const char * | regClassStrings [] |

| static constexpr size_t | Scale = TheISA::NumVecElemPerVecReg |

Friends | |

| struct | std::hash< RegId > |

| std::ostream & | operator<< (std::ostream &os, const RegId &rid) |

Detailed Description

Register ID: describe an architectural register with its class and index.

This structure is used instead of just the register index to disambiguate between different classes of registers. For example, a integer register with index 3 is represented by Regid(IntRegClass, 3).

Definition at line 75 of file reg_class.hh.

Constructor & Destructor Documentation

◆ RegId() [1/3]

|

inline |

Definition at line 87 of file reg_class.hh.

◆ RegId() [2/3]

Definition at line 89 of file reg_class.hh.

◆ RegId() [3/3]

Definition at line 92 of file reg_class.hh.

References ILLEGAL_ELEM_INDEX, panic_if, and VecElemClass.

Member Function Documentation

◆ className()

|

inline |

Return a const char* with the register class name.

Definition at line 202 of file reg_class.hh.

References regClass.

Referenced by UnifiedFreeList::addReg(), InstructionQueue< Impl >::addToDependents(), InstructionQueue< Impl >::addToProducers(), PhysRegFile::getTrueId(), UnifiedRenameMap::lookup(), PhysRegId::PhysRegId(), MipsISA::readRegOtherThread(), UnifiedRenameMap::rename(), DefaultRename< Impl >::renameDestRegs(), DefaultRename< Impl >::renameSrcRegs(), UnifiedRenameMap::setEntry(), Scoreboard::setReg(), MipsISA::setRegOtherThread(), ElasticTrace::updateRegDep(), and InstructionQueue< Impl >::wakeDependents().

◆ classValue()

|

inline |

Class accessor.

Definition at line 200 of file reg_class.hh.

References regClass.

Referenced by UnifiedFreeList::addReg(), Checker< O3CPUImpl >::copyResult(), Minor::Scoreboard::findIndex(), X86ISA::ISA::flattenRegId(), SparcISA::ISA::flattenRegId(), ArmISA::ISA::flattenRegId(), BaseO3DynInst< Impl >::forwardOldRegs(), PhysRegFile::getTrueId(), UnifiedRenameMap::lookup(), operator<(), operator==(), PhysRegId::PhysRegId(), Minor::printRegName(), MipsISA::readRegOtherThread(), UnifiedRenameMap::rename(), DefaultRename< Impl >::renameSrcRegs(), UnifiedRenameMap::setEntry(), and MipsISA::setRegOtherThread().

◆ elemIndex()

|

inline |

Elem accessor.

Definition at line 198 of file reg_class.hh.

References elemIdx.

Referenced by ArmISA::ISA::flattenRegId(), PhysRegFile::getTrueId(), operator<(), operator==(), PhysRegId::PhysRegId(), Minor::printRegName(), PhysRegFile::readVecElem(), O3ThreadContext< Impl >::readVecElem(), SimpleThread::readVecElem(), PhysRegFile::readVecLane(), SimpleThread::readVecLane(), PhysRegFile::setVecElem(), O3ThreadContext< Impl >::setVecElem(), SimpleThread::setVecElem(), PhysRegFile::setVecLane(), O3ThreadContext< Impl >::setVecLane(), and SimpleThread::setVecLaneT().

◆ flatIndex()

|

inline |

Index flattening.

Required to be able to use a vector for the register mapping.

Definition at line 179 of file reg_class.hh.

References CCRegClass, elemIdx, FloatRegClass, IntRegClass, MiscRegClass, panic, regIdx, VecElemClass, VecPredRegClass, and VecRegClass.

Referenced by Minor::Scoreboard::findIndex(), SimpleRenameMap::lookup(), UnifiedRenameMap::lookup(), std::hash< RegId >::operator()(), SimpleRenameMap::rename(), and SimpleRenameMap::setEntry().

◆ getNumPinnedWrites()

|

inline |

Definition at line 204 of file reg_class.hh.

References numPinnedWrites.

Referenced by SimpleRenameMap::rename(), and DefaultRename< Impl >::renameDestRegs().

◆ index() [1/2]

|

inline |

Index accessors.

Definition at line 173 of file reg_class.hh.

References regIdx.

Referenced by UnifiedFreeList::addReg(), InstructionQueue< Impl >::addToDependents(), InstructionQueue< Impl >::addToProducers(), Checker< O3CPUImpl >::copyResult(), PhysRegId::elemId(), TimingExprSrcReg::eval(), Minor::Scoreboard::findIndex(), X86ISA::ISA::flattenRegId(), SparcISA::ISA::flattenRegId(), ArmISA::ISA::flattenRegId(), MrsOp::generateDisassembly(), PhysRegFile::getTrueId(), SimpleThread::getWritableVecPredReg(), SimpleThread::getWritableVecReg(), FullO3CPU< O3CPUImpl >::insertThread(), X86ISA::MemOp::MemOp(), X86ISA::X86StaticInst::merge(), operator<(), operator==(), PhysRegId::PhysRegId(), X86ISA::X86StaticInst::pick(), MsrBase::printMsrBase(), PowerISA::PowerStaticInst::printReg(), SparcISA::SparcStaticInst::printReg(), X86ISA::X86StaticInst::printReg(), Minor::printRegName(), PhysRegFile::readCCReg(), CheckerCPU::readCCRegOperand(), SimpleExecContext::readCCRegOperand(), Minor::ExecContext::readCCRegOperand(), PhysRegFile::readFloatReg(), Minor::ExecContext::readFloatRegOperandBits(), SimpleExecContext::readFloatRegOperandBits(), CheckerCPU::readFloatRegOperandBits(), PhysRegFile::readIntReg(), Minor::ExecContext::readIntRegOperand(), SimpleExecContext::readIntRegOperand(), CheckerCPU::readIntRegOperand(), BaseO3DynInst< Impl >::readMiscRegOperand(), Minor::ExecContext::readMiscRegOperand(), SimpleExecContext::readMiscRegOperand(), CheckerCPU::readMiscRegOperand(), MipsISA::readRegOtherThread(), PhysRegFile::readVecElem(), SimpleThread::readVecElem(), SimpleThread::readVecLane(), PhysRegFile::readVecPredReg(), Iris::ThreadContext::readVecPredReg(), SimpleThread::readVecPredReg(), PhysRegFile::readVecReg(), Iris::ThreadContext::readVecReg(), SimpleThread::readVecReg(), RiscvISA::registerName(), DefaultRename< Impl >::renameDestRegs(), DefaultRename< Impl >::renameSrcRegs(), PhysRegFile::setCCReg(), SimpleExecContext::setCCRegOperand(), CheckerCPU::setCCRegOperand(), Minor::ExecContext::setCCRegOperand(), PhysRegFile::setFloatReg(), Minor::ExecContext::setFloatRegOperandBits(), SimpleExecContext::setFloatRegOperandBits(), CheckerCPU::setFloatRegOperandBits(), PhysRegFile::setIntReg(), SimpleExecContext::setIntRegOperand(), Minor::ExecContext::setIntRegOperand(), CheckerCPU::setIntRegOperand(), BaseO3DynInst< Impl >::setMiscRegOperand(), Minor::ExecContext::setMiscRegOperand(), SimpleExecContext::setMiscRegOperand(), CheckerCPU::setMiscRegOperand(), Scoreboard::setReg(), MipsISA::setRegOtherThread(), PhysRegFile::setVecElem(), SimpleThread::setVecElem(), PhysRegFile::setVecLane(), SimpleThread::setVecLaneT(), PhysRegFile::setVecPredReg(), SimpleThread::setVecPredReg(), PhysRegFile::setVecReg(), SimpleThread::setVecReg(), X86ISA::X86StaticInst::signedPick(), InstructionQueue< Impl >::wakeDependents(), and X86ISA::X86StaticInst::X86StaticInst().

◆ index() [2/2]

|

inline |

Definition at line 174 of file reg_class.hh.

References regIdx.

◆ isCCReg()

|

inline |

true if it is a condition-code physical register.

Definition at line 158 of file reg_class.hh.

References CCRegClass.

Referenced by PhysRegId::isCCPhysReg(), PowerISA::PowerStaticInst::printReg(), X86ISA::X86StaticInst::printReg(), CheckerCPU::readCCRegOperand(), SimpleExecContext::readCCRegOperand(), Minor::ExecContext::readCCRegOperand(), SimpleExecContext::setCCRegOperand(), CheckerCPU::setCCRegOperand(), and Minor::ExecContext::setCCRegOperand().

◆ isFloatReg()

|

inline |

- Returns

- true if it is a floating-point physical register.

Definition at line 146 of file reg_class.hh.

References FloatRegClass.

Referenced by PhysRegId::isFloatPhysReg(), PowerISA::PowerStaticInst::printReg(), SparcISA::SparcStaticInst::printReg(), X86ISA::X86StaticInst::printReg(), Minor::ExecContext::readFloatRegOperandBits(), SimpleExecContext::readFloatRegOperandBits(), CheckerCPU::readFloatRegOperandBits(), Minor::ExecContext::setFloatRegOperandBits(), SimpleExecContext::setFloatRegOperandBits(), and CheckerCPU::setFloatRegOperandBits().

◆ isIntReg()

|

inline |

- Returns

- true if it is an integer physical register.

Definition at line 143 of file reg_class.hh.

References IntRegClass.

Referenced by PhysRegId::isIntPhysReg(), PowerISA::PowerStaticInst::printReg(), SparcISA::SparcStaticInst::printReg(), X86ISA::X86StaticInst::printReg(), Minor::ExecContext::readIntRegOperand(), SimpleExecContext::readIntRegOperand(), CheckerCPU::readIntRegOperand(), RiscvISA::registerName(), SimpleExecContext::setIntRegOperand(), Minor::ExecContext::setIntRegOperand(), and CheckerCPU::setIntRegOperand().

◆ isMiscReg()

|

inline |

true if it is a condition-code physical register.

Definition at line 161 of file reg_class.hh.

References MiscRegClass.

Referenced by MrsOp::generateDisassembly(), PhysRegId::isMiscPhysReg(), MsrBase::printMsrBase(), PowerISA::PowerStaticInst::printReg(), X86ISA::X86StaticInst::printReg(), BaseO3DynInst< Impl >::readMiscRegOperand(), Minor::ExecContext::readMiscRegOperand(), SimpleExecContext::readMiscRegOperand(), CheckerCPU::readMiscRegOperand(), BaseO3DynInst< Impl >::setMiscRegOperand(), Minor::ExecContext::setMiscRegOperand(), SimpleExecContext::setMiscRegOperand(), CheckerCPU::setMiscRegOperand(), and ElasticTrace::updateRegDep().

◆ isRenameable() [1/2]

|

inline |

Return true if this register can be renamed.

Definition at line 126 of file reg_class.hh.

References MiscRegClass.

Referenced by PhysRegId::isFixedMapping().

◆ isRenameable() [2/2]

|

inline |

Return true if this register can be renamed.

Definition at line 166 of file reg_class.hh.

References MiscRegClass.

◆ isVecElem()

|

inline |

true if it is a condition-code physical register.

Definition at line 152 of file reg_class.hh.

References VecElemClass.

Referenced by PhysRegId::isVectorPhysElem(), Minor::ExecContext::readVecElemOperand(), SimpleExecContext::readVecElemOperand(), Minor::ExecContext::setVecElemOperand(), SimpleExecContext::setVecElemOperand(), and CheckerCPU::setVecElemOperand().

◆ isVecPredReg()

|

inline |

true if it is a predicate physical register.

Definition at line 155 of file reg_class.hh.

References VecPredRegClass.

Referenced by Minor::ExecContext::getWritableVecPredRegOperand(), CheckerCPU::getWritableVecPredRegOperand(), SimpleExecContext::getWritableVecPredRegOperand(), PhysRegId::isVecPredPhysReg(), Minor::ExecContext::readVecPredRegOperand(), CheckerCPU::readVecPredRegOperand(), SimpleExecContext::readVecPredRegOperand(), Minor::ExecContext::setVecPredRegOperand(), SimpleExecContext::setVecPredRegOperand(), and CheckerCPU::setVecPredRegOperand().

◆ isVecReg()

|

inline |

true if it is a condition-code physical register.

Definition at line 149 of file reg_class.hh.

References VecRegClass.

Referenced by Minor::ExecContext::getWritableVecRegOperand(), CheckerCPU::getWritableVecRegOperand(), SimpleExecContext::getWritableVecRegOperand(), PhysRegId::isVectorPhysReg(), CheckerCPU::readVec16BitLaneOperand(), Minor::ExecContext::readVec16BitLaneOperand(), CheckerCPU::readVec32BitLaneOperand(), Minor::ExecContext::readVec32BitLaneOperand(), CheckerCPU::readVec64BitLaneOperand(), Minor::ExecContext::readVec64BitLaneOperand(), CheckerCPU::readVec8BitLaneOperand(), Minor::ExecContext::readVec8BitLaneOperand(), SimpleExecContext::readVecLaneOperand(), Minor::ExecContext::readVecRegOperand(), CheckerCPU::readVecRegOperand(), SimpleExecContext::readVecRegOperand(), CheckerCPU::setVecLaneOperandT(), Minor::ExecContext::setVecLaneOperandT(), SimpleExecContext::setVecLaneOperandT(), Minor::ExecContext::setVecRegOperand(), SimpleExecContext::setVecRegOperand(), and CheckerCPU::setVecRegOperand().

◆ isZeroReg()

|

inline |

Check if this is the zero register.

Returns true if this register is a zero register (needs to have a constant zero value throughout the execution).

Definition at line 137 of file reg_class.hh.

References IntRegClass, and ArmISA::ZeroReg.

Referenced by Minor::Scoreboard::findIndex(), Scoreboard::getReg(), PhysRegId::PhysRegId(), Minor::printRegName(), SimpleRenameMap::rename(), PhysRegFile::setFloatReg(), PhysRegFile::setIntReg(), Scoreboard::unsetReg(), and ElasticTrace::updateRegDep().

◆ operator!=()

|

inline |

Definition at line 109 of file reg_class.hh.

Referenced by PhysRegId::operator!=().

◆ operator<()

|

inline |

Order operator.

The order is required to implement maps with key type RegId

Definition at line 116 of file reg_class.hh.

References classValue(), elemIndex(), and index().

Referenced by PhysRegId::operator<().

◆ operator==()

|

inline |

Definition at line 104 of file reg_class.hh.

References classValue(), elemIndex(), and index().

Referenced by PhysRegId::operator==().

◆ setNumPinnedWrites()

|

inline |

Definition at line 205 of file reg_class.hh.

Referenced by DefaultRename< Impl >::renameDestRegs().

Friends And Related Function Documentation

◆ operator<<

|

friend |

Definition at line 208 of file reg_class.hh.

◆ std::hash< RegId >

|

friend |

Definition at line 84 of file reg_class.hh.

Member Data Documentation

◆ elemIdx

|

protected |

Definition at line 80 of file reg_class.hh.

Referenced by elemIndex(), and flatIndex().

◆ numPinnedWrites

|

protected |

Definition at line 82 of file reg_class.hh.

Referenced by PhysRegId::decrNumPinnedWrites(), getNumPinnedWrites(), PhysRegId::getNumPinnedWrites(), PhysRegId::incrNumPinnedWrites(), and PhysRegId::setNumPinnedWrites().

◆ regClass

|

protected |

Definition at line 78 of file reg_class.hh.

Referenced by className(), classValue(), and std::hash< RegId >::operator()().

◆ regClassStrings

|

staticprotected |

Definition at line 77 of file reg_class.hh.

◆ regIdx

|

protected |

Definition at line 79 of file reg_class.hh.

Referenced by flatIndex(), and index().

◆ Scale

|

staticprotected |

Definition at line 81 of file reg_class.hh.

The documentation for this class was generated from the following files:

- cpu/reg_class.hh

- cpu/reg_class.cc