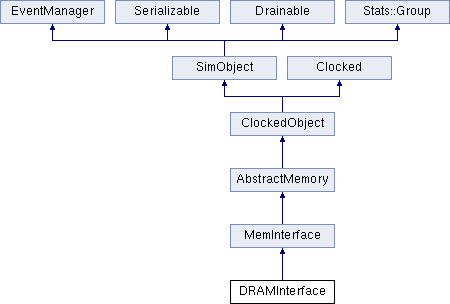

Interface to DRAM devices with media specific parameters, statistics, and functions. More...

#include <mem_interface.hh>

Classes | |

| struct | Command |

| Simple structure to hold the values needed to keep track of commands for DRAMPower. More... | |

| struct | DRAMStats |

| class | Rank |

| Rank class includes a vector of banks. More... | |

| struct | RankStats |

Public Member Functions | |

| void | init () override |

| Initialize the DRAM interface and verify parameters. More... | |

| void | startup () override |

| Iterate through dram ranks and instantiate per rank startup routine. More... | |

| void | setupRank (const uint8_t rank, const bool is_read) override |

| Setup the rank based on packet received. More... | |

| void | drainRanks () |

| Iterate through dram ranks to exit self-refresh in order to drain. More... | |

| bool | allRanksDrained () const override |

| Return true once refresh is complete for all ranks and there are no additional commands enqueued. More... | |

| void | suspend () |

| Iterate through DRAM ranks and suspend them. More... | |

| Tick | commandOffset () const override |

| Tick | accessLatency () const override |

| std::pair< MemPacketQueue::iterator, Tick > | chooseNextFRFCFS (MemPacketQueue &queue, Tick min_col_at) const override |

| For FR-FCFS policy, find first DRAM command that can issue. More... | |

| std::pair< Tick, Tick > | doBurstAccess (MemPacket *mem_pkt, Tick next_burst_at, const std::vector< MemPacketQueue > &queue) |

| Actually do the burst - figure out the latency it will take to service the req based on bank state, channel state etc and then update those states to account for this request. More... | |

| bool | burstReady (MemPacket *pkt) const override |

| Check if a burst operation can be issued to the DRAM. More... | |

| bool | isBusy () |

| This function checks if ranks are actively refreshing and therefore busy. More... | |

| void | addRankToRankDelay (Tick cmd_at) override |

| Add rank to rank delay to bus timing to all DRAM banks in alli ranks when access to an alternate interface is issued. More... | |

| void | respondEvent (uint8_t rank) |

| Complete response process for DRAM when read burst is complete This will update the counters and check if a power down state can be entered. More... | |

| void | checkRefreshState (uint8_t rank) |

| Check the refresh state to determine if refresh needs to be kicked back into action after a read response. More... | |

| DRAMInterface (const DRAMInterfaceParams *_p) | |

Public Member Functions inherited from MemInterface Public Member Functions inherited from MemInterface | |

| void | setCtrl (MemCtrl *_ctrl, unsigned int command_window) |

| Set a pointer to the controller and initialize interface based on controller parameters. More... | |

| Addr | getCtrlAddr (Addr addr) |

| Get an address in a dense range which starts from 0. More... | |

| uint32_t | bytesPerBurst () const |

| Tick | rankDelay () const |

| Determine the required delay for an access to a different rank. More... | |

| Tick | minReadToWriteDataGap () const |

| Tick | minWriteToReadDataGap () const |

| MemPacket * | decodePacket (const PacketPtr pkt, Addr pkt_addr, unsigned int size, bool is_read, bool is_dram) |

| Address decoder to figure out physical mapping onto ranks, banks, and rows. More... | |

| MemInterface (const Params *_p) | |

Public Member Functions inherited from AbstractMemory Public Member Functions inherited from AbstractMemory | |

| AbstractMemory (const Params *p) | |

| virtual | ~AbstractMemory () |

| void | initState () override |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| bool | isNull () const |

| See if this is a null memory that should never store data and always return zero. More... | |

| void | setBackingStore (uint8_t *pmem_addr) |

| Set the host memory backing store to be used by this memory controller. More... | |

| const std::list< LockedAddr > & | getLockedAddrList () const |

| Get the list of locked addresses to allow checkpointing. More... | |

| void | addLockedAddr (LockedAddr addr) |

| Add a locked address to allow for checkpointing. More... | |

| System * | system () const |

| read the system pointer Implemented for completeness with the setter More... | |

| void | system (System *sys) |

| Set the system pointer on this memory This can't be done via a python parameter because the system needs pointers to all the memories and the reverse would create a cycle in the object graph. More... | |

| const Params * | params () const |

| AddrRange | getAddrRange () const |

| Get the address range. More... | |

| uint8_t * | toHostAddr (Addr addr) const |

| Transform a gem5 address space address into its physical counterpart in the host address space. More... | |

| uint64_t | size () const |

| Get the memory size. More... | |

| Addr | start () const |

| Get the start address. More... | |

| bool | isConfReported () const |

| Should this memory be passed to the kernel and part of the OS physical memory layout. More... | |

| bool | isInAddrMap () const |

| Some memories are used as shadow memories or should for other reasons not be part of the global address map. More... | |

| bool | isKvmMap () const |

| When shadow memories are in use, KVM may want to make one or the other, but cannot map both into the guest address space. More... | |

| void | access (PacketPtr pkt) |

| Perform an untimed memory access and update all the state (e.g. More... | |

| void | functionalAccess (PacketPtr pkt) |

| Perform an untimed memory read or write without changing anything but the memory itself. More... | |

Public Member Functions inherited from ClockedObject Public Member Functions inherited from ClockedObject | |

| ClockedObject (const ClockedObjectParams *p) | |

| const Params * | params () const |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from SimObject Public Member Functions inherited from SimObject | |

| const Params * | params () const |

| SimObject (const Params *_params) | |

| virtual | ~SimObject () |

| virtual const std::string | name () const |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | regProbePoints () |

| Register probe points for this object. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. More... | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from EventManager Public Member Functions inherited from EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. More... | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. More... | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from Drainable Public Member Functions inherited from Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Public Member Functions inherited from Stats::Group Public Member Functions inherited from Stats::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. More... | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. More... | |

| virtual void | resetStats () |

| Callback to reset stats. More... | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. More... | |

| void | addStat (Stats::Info *info) |

| Register a stat with this group. More... | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. More... | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. More... | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. More... | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. More... | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

Public Member Functions inherited from Clocked Public Member Functions inherited from Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Private Types | |

| enum | PowerState { PWR_IDLE = 0, PWR_REF, PWR_SREF, PWR_PRE_PDN, PWR_ACT, PWR_ACT_PDN } |

| The power state captures the different operational states of the DRAM and interacts with the bus read/write state machine, and the refresh state machine. More... | |

| enum | RefreshState { REF_IDLE = 0, REF_DRAIN, REF_PD_EXIT, REF_SREF_EXIT, REF_PRE, REF_START, REF_RUN } |

| The refresh state is used to control the progress of the refresh scheduling. More... | |

Private Member Functions | |

| void | activateBank (Rank &rank_ref, Bank &bank_ref, Tick act_tick, uint32_t row) |

| Keep track of when row activations happen, in order to enforce the maximum number of activations in the activation window. More... | |

| void | prechargeBank (Rank &rank_ref, Bank &bank_ref, Tick pre_tick, bool auto_or_preall=false, bool trace=true) |

| Precharge a given bank and also update when the precharge is done. More... | |

| Tick | writeToReadDelay () const override |

| std::pair< std::vector< uint32_t >, bool > | minBankPrep (const MemPacketQueue &queue, Tick min_col_at) const |

| Find which are the earliest banks ready to issue an activate for the enqueued requests. More... | |

| Tick | burstDelay () const |

Static Private Member Functions | |

| static bool | sortTime (const Command &cmd, const Command &cmd_next) |

| Function for sorting Command structures based on timeStamp. More... | |

Private Attributes | |

| const uint32_t | bankGroupsPerRank |

| DRAM specific device characteristics. More... | |

| const bool | bankGroupArch |

| const Tick | tCL |

| DRAM specific timing requirements. More... | |

| const Tick | tBURST_MIN |

| const Tick | tBURST_MAX |

| const Tick | tCCD_L_WR |

| const Tick | tCCD_L |

| const Tick | tRCD |

| const Tick | tRP |

| const Tick | tRAS |

| const Tick | tWR |

| const Tick | tRTP |

| const Tick | tRFC |

| const Tick | tREFI |

| const Tick | tRRD |

| const Tick | tRRD_L |

| const Tick | tPPD |

| const Tick | tAAD |

| const Tick | tXAW |

| const Tick | tXP |

| const Tick | tXS |

| const Tick | clkResyncDelay |

| const bool | dataClockSync |

| const bool | burstInterleave |

| const uint8_t | twoCycleActivate |

| const uint32_t | activationLimit |

| const Tick | wrToRdDlySameBG |

| const Tick | rdToWrDlySameBG |

| Enums::PageManage | pageMgmt |

| const uint32_t | maxAccessesPerRow |

| Max column accesses (read and write) per row, before forefully closing it. More... | |

| uint64_t | timeStampOffset |

| uint8_t | activeRank |

| bool | enableDRAMPowerdown |

| Enable or disable DRAM powerdown states. More... | |

| Tick | lastStatsResetTick |

| The time when stats were last reset used to calculate average power. More... | |

| DRAMStats | stats |

| std::vector< Rank * > | ranks |

| Vector of dram ranks. More... | |

Additional Inherited Members | |

Public Types inherited from MemInterface Public Types inherited from MemInterface | |

| typedef MemInterfaceParams | Params |

Public Types inherited from AbstractMemory Public Types inherited from AbstractMemory | |

| typedef AbstractMemoryParams | Params |

Public Types inherited from ClockedObject Public Types inherited from ClockedObject | |

| typedef ClockedObjectParams | Params |

| Parameters of ClockedObject. More... | |

Public Types inherited from SimObject Public Types inherited from SimObject | |

| typedef SimObjectParams | Params |

Static Public Member Functions inherited from SimObject Static Public Member Functions inherited from SimObject | |

| static void | serializeAll (CheckpointOut &cp) |

| Serialize all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| Serializes all the SimObjects. More... | |

| static void | unserializeGlobals (CheckpointIn &cp) |

Public Attributes inherited from MemInterface Public Attributes inherited from MemInterface | |

| const uint32_t | readBufferSize |

| Buffer sizes for read and write queues in the controller These are passed to the controller on instantiation Defining them here allows for buffers to be resized based on memory type / configuration. More... | |

| const uint32_t | writeBufferSize |

Public Attributes inherited from ClockedObject Public Attributes inherited from ClockedObject | |

| PowerState * | powerState |

Protected Member Functions inherited from MemInterface Protected Member Functions inherited from MemInterface | |

| Tick | readToWriteDelay () const |

| Tick | rankToRankDelay () const |

Protected Member Functions inherited from AbstractMemory Protected Member Functions inherited from AbstractMemory | |

| bool | checkLockedAddrList (PacketPtr pkt) |

| void | trackLoadLocked (PacketPtr pkt) |

| bool | writeOK (PacketPtr pkt) |

Protected Member Functions inherited from Drainable Protected Member Functions inherited from Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. More... | |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from Clocked Protected Member Functions inherited from Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. More... | |

Protected Attributes inherited from MemInterface Protected Attributes inherited from MemInterface | |

| MemCtrl * | ctrl |

| A pointer to the parent MemCtrl instance. More... | |

| unsigned int | maxCommandsPerWindow |

| Number of commands that can issue in the defined controller command window, used to verify command bandwidth. More... | |

| Enums::AddrMap | addrMapping |

| Memory controller configuration initialized based on parameter values. More... | |

| const uint32_t | burstSize |

| General device and channel characteristics The rowsPerBank is determined based on the capacity, number of ranks and banks, the burst size, and the row buffer size. More... | |

| const uint32_t | deviceSize |

| const uint32_t | deviceRowBufferSize |

| const uint32_t | devicesPerRank |

| const uint32_t | rowBufferSize |

| const uint32_t | burstsPerRowBuffer |

| const uint32_t | burstsPerStripe |

| const uint32_t | ranksPerChannel |

| const uint32_t | banksPerRank |

| uint32_t | rowsPerBank |

| const Tick M5_CLASS_VAR_USED | tCK |

| General timing requirements. More... | |

| const Tick | tCS |

| const Tick | tBURST |

| const Tick | tRTW |

| const Tick | tWTR |

Protected Attributes inherited from AbstractMemory Protected Attributes inherited from AbstractMemory | |

| AddrRange | range |

| uint8_t * | pmemAddr |

| MemBackdoor | backdoor |

| const bool | confTableReported |

| const bool | inAddrMap |

| const bool | kvmMap |

| std::list< LockedAddr > | lockedAddrList |

| System * | _system |

| Pointer to the System object. More... | |

| AbstractMemory::MemStats | stats |

Protected Attributes inherited from SimObject Protected Attributes inherited from SimObject | |

| const SimObjectParams * | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from EventManager Protected Attributes inherited from EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

Detailed Description

Interface to DRAM devices with media specific parameters, statistics, and functions.

The DRAMInterface includes a class for individual ranks and per rank functions.

Definition at line 301 of file mem_interface.hh.

Member Enumeration Documentation

◆ PowerState

|

private |

The power state captures the different operational states of the DRAM and interacts with the bus read/write state machine, and the refresh state machine.

PWR_IDLE : The idle state in which all banks are closed From here can transition to: PWR_REF, PWR_ACT, PWR_PRE_PDN

PWR_REF : Auto-refresh state. Will transition when refresh is complete based on power state prior to PWR_REF From here can transition to: PWR_IDLE, PWR_PRE_PDN, PWR_SREF

PWR_SREF : Self-refresh state. Entered after refresh if previous state was PWR_PRE_PDN From here can transition to: PWR_IDLE

PWR_PRE_PDN : Precharge power down state From here can transition to: PWR_REF, PWR_IDLE

PWR_ACT : Activate state in which one or more banks are open From here can transition to: PWR_IDLE, PWR_ACT_PDN

PWR_ACT_PDN : Activate power down state From here can transition to: PWR_ACT

| Enumerator | |

|---|---|

| PWR_IDLE | |

| PWR_REF | |

| PWR_SREF | |

| PWR_PRE_PDN | |

| PWR_ACT | |

| PWR_ACT_PDN | |

Definition at line 347 of file mem_interface.hh.

◆ RefreshState

|

private |

The refresh state is used to control the progress of the refresh scheduling.

When normal operation is in progress the refresh state is idle. Once tREFI has elasped, a refresh event is triggered to start the following STM transitions which are used to issue a refresh and return back to normal operation

REF_IDLE : IDLE state used during normal operation From here can transition to: REF_DRAIN

REF_SREF_EXIT : Exiting a self-refresh; refresh event scheduled after self-refresh exit completes From here can transition to: REF_DRAIN

REF_DRAIN : Drain state in which on going accesses complete. From here can transition to: REF_PD_EXIT

REF_PD_EXIT : Evaluate pwrState and issue wakeup if needed Next state dependent on whether banks are open From here can transition to: REF_PRE, REF_START

REF_PRE : Close (precharge) all open banks From here can transition to: REF_START

REF_START : Issue refresh command and update DRAMPower stats From here can transition to: REF_RUN

REF_RUN : Refresh running, waiting for tRFC to expire From here can transition to: REF_IDLE, REF_SREF_EXIT

| Enumerator | |

|---|---|

| REF_IDLE | |

| REF_DRAIN | |

| REF_PD_EXIT | |

| REF_SREF_EXIT | |

| REF_PRE | |

| REF_START | |

| REF_RUN | |

Definition at line 387 of file mem_interface.hh.

Constructor & Destructor Documentation

◆ DRAMInterface()

| DRAMInterface::DRAMInterface | ( | const DRAMInterfaceParams * | _p | ) |

Definition at line 733 of file mem_interface.cc.

References bankGroupArch, bankGroupsPerRank, MemInterface::banksPerRank, MemInterface::burstSize, MemInterface::burstsPerRowBuffer, ceilLog2(), MemInterface::deviceSize, MemInterface::devicesPerRank, DPRINTF, fatal, fatal_if, ArmISA::i, isPowerOf2(), ranks, MemInterface::ranksPerChannel, MemInterface::rowBufferSize, MemInterface::rowsPerBank, AbstractMemory::size(), MemInterface::tBURST, tCCD_L, tCCD_L_WR, tREFI, tRFC, tRP, tRRD, tRRD_L, ULL, and warn.

Member Function Documentation

◆ accessLatency()

|

inlineoverridevirtual |

Implements MemInterface.

Definition at line 932 of file mem_interface.hh.

References tCL, tRCD, and tRP.

Referenced by MemCtrl::recvAtomic().

◆ activateBank()

|

private |

Keep track of when row activations happen, in order to enforce the maximum number of activations in the activation window.

The method updates the time that the banks become available based on the current limits.

- Parameters

-

rank_ref Reference to the rank bank_ref Reference to the bank act_tick Time when the activation takes place row Index of the row

Definition at line 284 of file mem_interface.cc.

References DRAMInterface::Rank::activateEvent, activationLimit, DRAMInterface::Rank::actTicks, MemInterface::Bank::bank, MemInterface::Bank::bankgr, bankGroupArch, DRAMInterface::Rank::banks, MemInterface::banksPerRank, MemInterface::Bank::bytesAccessed, DRAMInterface::Rank::cmdList, MemInterface::ctrl, divCeil(), DPRINTF, ArmISA::i, ArmISA::j, MemInterface::maxCommandsPerWindow, MemInterface::Bank::NO_ROW, DRAMInterface::Rank::numBanksActive, MemInterface::Bank::openRow, panic, MemInterface::Bank::preAllowedAt, DRAMInterface::Rank::rank, ranks, MemInterface::Bank::rdAllowedAt, EventManager::reschedule(), MemInterface::Bank::rowAccesses, EventManager::schedule(), Event::scheduled(), tAAD, MemInterface::tCK, timeStampOffset, tRAS, tRCD, tRRD, tRRD_L, twoCycleActivate, tXAW, MemCtrl::verifyMultiCmd(), MemCtrl::verifySingleCmd(), Event::when(), and MemInterface::Bank::wrAllowedAt.

Referenced by doBurstAccess().

◆ addRankToRankDelay()

|

overridevirtual |

Add rank to rank delay to bus timing to all DRAM banks in alli ranks when access to an alternate interface is issued.

param cmd_at Time of current command used as starting point for addition of rank-to-rank delay

Implements MemInterface.

Definition at line 717 of file mem_interface.cc.

References MemInterface::banksPerRank, ArmISA::i, ArmISA::n, ranks, and MemInterface::rankToRankDelay().

Referenced by MemCtrl::doBurstAccess().

◆ allRanksDrained()

|

overridevirtual |

Return true once refresh is complete for all ranks and there are no additional commands enqueued.

(only evaluated when draining) This will ensure that all banks are closed, power state is IDLE, and power stats have been updated

- Returns

- true if all ranks have refreshed, with no commands enqueued

Implements MemInterface.

Definition at line 1014 of file mem_interface.cc.

References MipsISA::r, and ranks.

Referenced by MemCtrl::allIntfDrained().

◆ burstDelay()

|

inlineprivate |

Definition at line 879 of file mem_interface.hh.

References burstInterleave, MemInterface::tBURST, and tBURST_MAX.

◆ burstReady()

|

inlineoverridevirtual |

Check if a burst operation can be issued to the DRAM.

- Parameters

-

Return true if RD/WR can issue This requires the DRAM to be in the REF IDLE state

Implements MemInterface.

Definition at line 971 of file mem_interface.hh.

References MemPacket::rank, and ranks.

Referenced by chooseNextFRFCFS(), and MemCtrl::packetReady().

◆ checkRefreshState()

| void DRAMInterface::checkRefreshState | ( | uint8_t | rank | ) |

Check the refresh state to determine if refresh needs to be kicked back into action after a read response.

- Parameters

-

rank Specifies rank associated with read burst

Definition at line 987 of file mem_interface.cc.

References curTick(), DRAMInterface::Rank::prechargeEvent, ranks, REF_PRE, DRAMInterface::Rank::refreshEvent, DRAMInterface::Rank::refreshState, EventManager::schedule(), and Event::scheduled().

Referenced by MemCtrl::processRespondEvent().

◆ chooseNextFRFCFS()

|

overridevirtual |

For FR-FCFS policy, find first DRAM command that can issue.

- Parameters

-

queue Queued requests to consider min_col_at Minimum tick for 'seamless' issue

- Returns

- an iterator to the selected packet, else queue.end()

- the tick when the packet selected will issue

Implements MemInterface.

Definition at line 169 of file mem_interface.cc.

References MemPacket::bank, bits(), burstReady(), DPRINTF, ArmISA::i, MemPacket::isDram(), MemPacket::isRead(), MaxTick, minBankPrep(), MemInterface::Bank::openRow, MemPacket::rank, ranks, MemInterface::ranksPerChannel, MemInterface::Bank::rdAllowedAt, MemPacket::row, and MemInterface::Bank::wrAllowedAt.

Referenced by MemCtrl::chooseNextFRFCFS().

◆ commandOffset()

|

inlineoverridevirtual |

Implements MemInterface.

Definition at line 927 of file mem_interface.hh.

Referenced by MemCtrl::doBurstAccess(), and MemCtrl::startup().

◆ doBurstAccess()

| pair< Tick, Tick > DRAMInterface::doBurstAccess | ( | MemPacket * | mem_pkt, |

| Tick | next_burst_at, | ||

| const std::vector< MemPacketQueue > & | queue | ||

| ) |

Actually do the burst - figure out the latency it will take to service the req based on bank state, channel state etc and then update those states to account for this request.

Based on this, update the packet's "readyTime" and move it to the response q from where it will eventually go back to the outside world.

- Parameters

-

mem_pkt The packet created from the outside world pkt next_burst_at Minimum bus timing requirement from controller queue Reference to the read or write queue with the packet

- Returns

- pair, tick when current burst is issued and tick when next burst can issue

Definition at line 456 of file mem_interface.cc.

References MemInterface::Bank::actAllowedAt, activateBank(), activeRank, MemPacket::addr, MemPacket::bank, MemInterface::Bank::bankgr, bankGroupArch, MemPacket::bankId, DRAMInterface::Rank::banks, MemInterface::banksPerRank, burstInterleave, MemInterface::burstSize, MemInterface::Bank::bytesAccessed, DRAMInterface::DRAMStats::bytesRead, DRAMInterface::DRAMStats::bytesWritten, clkResyncDelay, DRAMInterface::Rank::cmdList, MemInterface::ctrl, curTick(), dataClockSync, divCeil(), DPRINTF, MemPacket::entryTime, ArmISA::i, DRAMInterface::Rank::inLowPowerState, DRAMInterface::Rank::inRefIdleState(), MemPacket::isRead(), ArmISA::j, DRAMInterface::Rank::lastBurstTick, maxAccessesPerRow, MemInterface::maxCommandsPerWindow, MemInterface::Bank::NO_ROW, QoS::MemCtrl::numPriorities(), MemInterface::Bank::openRow, DRAMInterface::Rank::outstandingEvents, MipsISA::p, pageMgmt, DRAMInterface::DRAMStats::perBankRdBursts, DRAMInterface::DRAMStats::perBankWrBursts, MemInterface::Bank::preAllowedAt, prechargeBank(), PWR_SREF, DRAMInterface::Rank::pwrState, MemPacket::rank, ranks, MemInterface::ranksPerChannel, MemInterface::rankToRankDelay(), RD, MemInterface::Bank::rdAllowedAt, rdToWrDlySameBG, DRAMInterface::DRAMStats::readBursts, DRAMInterface::DRAMStats::readRowHits, MemInterface::readToWriteDelay(), MemPacket::readyTime, EventManager::reschedule(), MemPacket::row, MemInterface::Bank::rowAccesses, EventManager::schedule(), Event::scheduled(), DRAMInterface::Rank::scheduleWakeUpEvent(), stats, MemInterface::tBURST, tBURST_MIN, tCCD_L, tCCD_L_WR, MemInterface::tCK, tCL, timeStampOffset, DRAMInterface::DRAMStats::totBusLat, DRAMInterface::DRAMStats::totMemAccLat, DRAMInterface::DRAMStats::totQLat, tRTP, tWR, tXP, MemCtrl::verifyMultiCmd(), MemCtrl::verifySingleCmd(), Event::when(), MemInterface::Bank::wrAllowedAt, DRAMInterface::DRAMStats::writeBursts, DRAMInterface::Rank::writeDoneEvent, DRAMInterface::Rank::writeEntries, DRAMInterface::DRAMStats::writeRowHits, writeToReadDelay(), and wrToRdDlySameBG.

Referenced by MemCtrl::doBurstAccess().

◆ drainRanks()

| void DRAMInterface::drainRanks | ( | ) |

Iterate through dram ranks to exit self-refresh in order to drain.

Definition at line 1000 of file mem_interface.cc.

References DPRINTF, PWR_SREF, MipsISA::r, ranks, and tXS.

Referenced by MemCtrl::drain().

◆ init()

|

overridevirtual |

Initialize the DRAM interface and verify parameters.

Reimplemented from SimObject.

Definition at line 837 of file mem_interface.cc.

References MemInterface::addrMapping, MemInterface::burstsPerRowBuffer, MemInterface::burstsPerStripe, fatal, AddrRange::granularity(), SimObject::init(), AddrRange::interleaved(), SimObject::name(), AbstractMemory::range, MemInterface::rowBufferSize, and AbstractMemory::system().

◆ isBusy()

| bool DRAMInterface::isBusy | ( | ) |

This function checks if ranks are actively refreshing and therefore busy.

The function also checks if ranks are in the self-refresh state, in which case, a self-refresh exit is initiated.

return boolean if all ranks are in refresh and therefore busy

Definition at line 892 of file mem_interface.cc.

References DPRINTF, PWR_SREF, MipsISA::r, ranks, MemInterface::ranksPerChannel, and tXS.

Referenced by MemCtrl::processNextReqEvent().

◆ minBankPrep()

|

private |

Find which are the earliest banks ready to issue an activate for the enqueued requests.

Assumes maximum of 32 banks per rank Also checks if the bank is already prepped.

- Parameters

-

queue Queued requests to consider min_col_at time of seamless burst command

- Returns

- One-hot encoded mask of bank indices

- boolean indicating burst can issue seamlessly, with no gaps

Definition at line 1037 of file mem_interface.cc.

References MemInterface::banksPerRank, MemInterface::ctrl, curTick(), MipsISA::fill, ArmISA::i, MemCtrl::inReadBusState(), ArmISA::j, MaxTick, MemInterface::Bank::NO_ROW, MipsISA::p, ranks, MemInterface::ranksPerChannel, replaceBits(), tRCD, and tRP.

Referenced by chooseNextFRFCFS().

◆ prechargeBank()

|

private |

Precharge a given bank and also update when the precharge is done.

This will also deal with any stats related to the accesses to the open page.

- Parameters

-

rank_ref The rank to precharge bank_ref The bank to precharge pre_tick Time when the precharge takes place auto_or_preall Is this an auto-precharge or precharge all command trace Is this an auto precharge then do not add to trace

Definition at line 393 of file mem_interface.cc.

References MemInterface::Bank::actAllowedAt, MemInterface::Bank::bank, DRAMInterface::Rank::banks, MemInterface::banksPerRank, MemInterface::Bank::bytesAccessed, DRAMInterface::DRAMStats::bytesPerActivate, DRAMInterface::Rank::cmdList, MemInterface::ctrl, divCeil(), DPRINTF, ArmISA::i, MemInterface::maxCommandsPerWindow, MemInterface::Bank::NO_ROW, DRAMInterface::Rank::numBanksActive, MemInterface::Bank::openRow, DRAMInterface::Rank::outstandingEvents, MemInterface::Bank::preAllowedAt, DRAMInterface::Rank::prechargeEvent, DRAMInterface::Rank::rank, EventManager::reschedule(), Stats::DistBase< Derived, Stor >::sample(), EventManager::schedule(), Event::scheduled(), stats, MemInterface::tCK, timeStampOffset, tPPD, tRP, MemCtrl::verifySingleCmd(), and Event::when().

Referenced by doBurstAccess().

◆ respondEvent()

| void DRAMInterface::respondEvent | ( | uint8_t | rank | ) |

Complete response process for DRAM when read burst is complete This will update the counters and check if a power down state can be entered.

- Parameters

-

rank Specifies rank associated with read burst

Definition at line 940 of file mem_interface.cc.

References DRAMInterface::Rank::activateEvent, curTick(), DPRINTF, enableDRAMPowerdown, DRAMInterface::Rank::inRefIdleState(), DRAMInterface::Rank::isQueueEmpty(), DRAMInterface::Rank::outstandingEvents, DRAMInterface::Rank::powerDownSleep(), DRAMInterface::Rank::prechargeEvent, PWR_ACT_PDN, PWR_IDLE, PWR_PRE_PDN, PWR_SREF, DRAMInterface::Rank::pwrState, ranks, DRAMInterface::Rank::readEntries, and Event::scheduled().

Referenced by MemCtrl::processRespondEvent().

◆ setupRank()

|

overridevirtual |

Setup the rank based on packet received.

- Parameters

-

integer value of rank to be setup. used to index ranks vector are we setting up rank for read or write packet?

Implements MemInterface.

Definition at line 929 of file mem_interface.cc.

References ranks.

Referenced by MemCtrl::addToReadQueue(), and MemCtrl::addToWriteQueue().

◆ sortTime()

|

inlinestaticprivate |

Function for sorting Command structures based on timeStamp.

Definition at line 712 of file mem_interface.hh.

References DRAMInterface::Command::timeStamp.

Referenced by DRAMInterface::Rank::flushCmdList().

◆ startup()

|

overridevirtual |

Iterate through dram ranks and instantiate per rank startup routine.

Reimplemented from SimObject.

Definition at line 879 of file mem_interface.cc.

References curTick(), divCeil(), MipsISA::r, ranks, AbstractMemory::system(), MemInterface::tCK, timeStampOffset, tREFI, and tRP.

Referenced by MemCtrl::drainResume().

◆ suspend()

| void DRAMInterface::suspend | ( | ) |

Iterate through DRAM ranks and suspend them.

Definition at line 1029 of file mem_interface.cc.

References MipsISA::r, and ranks.

Referenced by MemCtrl::drainResume().

◆ writeToReadDelay()

|

inlineoverrideprivatevirtual |

Reimplemented from MemInterface.

Definition at line 860 of file mem_interface.hh.

References MemInterface::tBURST, tCL, and MemInterface::tWTR.

Referenced by doBurstAccess().

Member Data Documentation

◆ activationLimit

|

private |

Definition at line 749 of file mem_interface.hh.

Referenced by activateBank().

◆ activeRank

|

private |

Definition at line 765 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ bankGroupArch

|

private |

Definition at line 721 of file mem_interface.hh.

Referenced by activateBank(), doBurstAccess(), and DRAMInterface().

◆ bankGroupsPerRank

|

private |

DRAM specific device characteristics.

Definition at line 720 of file mem_interface.hh.

Referenced by DRAMInterface().

◆ burstInterleave

|

private |

Definition at line 747 of file mem_interface.hh.

Referenced by burstDelay(), and doBurstAccess().

◆ clkResyncDelay

|

private |

Definition at line 745 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ dataClockSync

|

private |

Definition at line 746 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ enableDRAMPowerdown

|

private |

Enable or disable DRAM powerdown states.

Definition at line 768 of file mem_interface.hh.

Referenced by respondEvent().

◆ lastStatsResetTick

|

private |

The time when stats were last reset used to calculate average power.

Definition at line 771 of file mem_interface.hh.

◆ maxAccessesPerRow

|

private |

Max column accesses (read and write) per row, before forefully closing it.

Definition at line 759 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ pageMgmt

|

private |

Definition at line 754 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ ranks

|

private |

Vector of dram ranks.

Definition at line 855 of file mem_interface.hh.

Referenced by activateBank(), addRankToRankDelay(), allRanksDrained(), burstReady(), checkRefreshState(), chooseNextFRFCFS(), doBurstAccess(), drainRanks(), DRAMInterface(), isBusy(), minBankPrep(), respondEvent(), setupRank(), startup(), and suspend().

◆ rdToWrDlySameBG

|

private |

Definition at line 751 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ stats

|

private |

Definition at line 850 of file mem_interface.hh.

Referenced by DRAMInterface::Rank::computeStats(), doBurstAccess(), prechargeBank(), DRAMInterface::Rank::processPowerEvent(), and DRAMInterface::Rank::updatePowerStats().

◆ tAAD

|

private |

Definition at line 741 of file mem_interface.hh.

Referenced by activateBank().

◆ tBURST_MAX

|

private |

Definition at line 728 of file mem_interface.hh.

Referenced by burstDelay().

◆ tBURST_MIN

|

private |

Definition at line 727 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ tCCD_L

|

private |

Definition at line 730 of file mem_interface.hh.

Referenced by doBurstAccess(), and DRAMInterface().

◆ tCCD_L_WR

|

private |

Definition at line 729 of file mem_interface.hh.

Referenced by doBurstAccess(), and DRAMInterface().

◆ tCL

|

private |

DRAM specific timing requirements.

Definition at line 726 of file mem_interface.hh.

Referenced by accessLatency(), doBurstAccess(), and writeToReadDelay().

◆ timeStampOffset

|

private |

Definition at line 762 of file mem_interface.hh.

Referenced by activateBank(), doBurstAccess(), prechargeBank(), and startup().

◆ tPPD

|

private |

Definition at line 740 of file mem_interface.hh.

Referenced by prechargeBank().

◆ tRAS

|

private |

Definition at line 733 of file mem_interface.hh.

Referenced by activateBank().

◆ tRCD

|

private |

Definition at line 731 of file mem_interface.hh.

Referenced by accessLatency(), activateBank(), commandOffset(), and minBankPrep().

◆ tREFI

|

private |

Definition at line 737 of file mem_interface.hh.

Referenced by DRAMInterface(), and startup().

◆ tRFC

|

private |

Definition at line 736 of file mem_interface.hh.

Referenced by DRAMInterface().

◆ tRP

|

private |

Definition at line 732 of file mem_interface.hh.

Referenced by accessLatency(), commandOffset(), DRAMInterface(), minBankPrep(), prechargeBank(), and startup().

◆ tRRD

|

private |

Definition at line 738 of file mem_interface.hh.

Referenced by activateBank(), and DRAMInterface().

◆ tRRD_L

|

private |

Definition at line 739 of file mem_interface.hh.

Referenced by activateBank(), and DRAMInterface().

◆ tRTP

|

private |

Definition at line 735 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ twoCycleActivate

|

private |

Definition at line 748 of file mem_interface.hh.

Referenced by activateBank().

◆ tWR

|

private |

Definition at line 734 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ tXAW

|

private |

Definition at line 742 of file mem_interface.hh.

Referenced by activateBank().

◆ tXP

|

private |

Definition at line 743 of file mem_interface.hh.

Referenced by doBurstAccess().

◆ tXS

|

private |

Definition at line 744 of file mem_interface.hh.

Referenced by drainRanks(), and isBusy().

◆ wrToRdDlySameBG

|

private |

Definition at line 750 of file mem_interface.hh.

Referenced by doBurstAccess().

The documentation for this class was generated from the following files:

- mem/mem_interface.hh

- mem/mem_interface.cc