#include <dram_rot_gen.hh>

Public Member Functions | |

| DramRotGen (SimObject &obj, RequestorID requestor_id, Tick _duration, Addr start_addr, Addr end_addr, Addr _blocksize, Addr cacheline_size, Tick min_period, Tick max_period, uint8_t read_percent, Addr data_limit, unsigned int num_seq_pkts, unsigned int page_size, unsigned int nbr_of_banks_DRAM, unsigned int nbr_of_banks_util, Enums::AddrMap addr_mapping, unsigned int nbr_of_ranks, unsigned int max_seq_count_per_rank) | |

| Create a DRAM address sequence generator. More... | |

| PacketPtr | getNextPacket () |

| Get the next generated packet. More... | |

Public Member Functions inherited from DramGen Public Member Functions inherited from DramGen | |

| DramGen (SimObject &obj, RequestorID requestor_id, Tick _duration, Addr start_addr, Addr end_addr, Addr _blocksize, Addr cacheline_size, Tick min_period, Tick max_period, uint8_t read_percent, Addr data_limit, unsigned int num_seq_pkts, unsigned int page_size, unsigned int nbr_of_banks_DRAM, unsigned int nbr_of_banks_util, Enums::AddrMap addr_mapping, unsigned int nbr_of_ranks) | |

| Create a DRAM address sequence generator. More... | |

| void | genStartAddr (unsigned int new_bank, unsigned int new_rank) |

| Insert bank, rank, and column bits into packed address to create address for 1st command in a series. More... | |

Public Member Functions inherited from RandomGen Public Member Functions inherited from RandomGen | |

| RandomGen (SimObject &obj, RequestorID requestor_id, Tick _duration, Addr start_addr, Addr end_addr, Addr _blocksize, Addr cacheline_size, Tick min_period, Tick max_period, uint8_t read_percent, Addr data_limit) | |

| Create a random address sequence generator. More... | |

| void | enter () |

| Enter this generator state. More... | |

| PacketPtr | getNextPacket () |

| Get the next generated packet. More... | |

| Tick | nextPacketTick (bool elastic, Tick delay) const |

| Determine the tick when the next packet is available. More... | |

Public Member Functions inherited from StochasticGen Public Member Functions inherited from StochasticGen | |

| StochasticGen (SimObject &obj, RequestorID requestor_id, Tick _duration, Addr start_addr, Addr end_addr, Addr _blocksize, Addr cacheline_size, Tick min_period, Tick max_period, uint8_t read_percent, Addr data_limit) | |

Public Member Functions inherited from BaseGen Public Member Functions inherited from BaseGen | |

| BaseGen (SimObject &obj, RequestorID requestor_id, Tick _duration) | |

| Create a base generator. More... | |

| virtual | ~BaseGen () |

| std::string | name () const |

| Get the name, useful for DPRINTFs. More... | |

| virtual void | exit () |

| Exit this generator state. More... | |

Private Attributes | |

| const unsigned int | maxSeqCountPerRank |

| Number of command series issued before the rank is changed. More... | |

| unsigned int | nextSeqCount |

| Next packet series count used to set rank and bank, and update isRead Incremented at the start of a new packet series More... | |

Additional Inherited Members | |

Public Attributes inherited from BaseGen Public Attributes inherited from BaseGen | |

| const Tick | duration |

| Time to spend in this state. More... | |

Protected Member Functions inherited from BaseGen Protected Member Functions inherited from BaseGen | |

| PacketPtr | getPacket (Addr addr, unsigned size, const MemCmd &cmd, Request::FlagsType flags=0) |

| Generate a new request and associated packet. More... | |

Protected Attributes inherited from DramGen Protected Attributes inherited from DramGen | |

| const unsigned int | numSeqPkts |

| Number of sequential DRAM packets to be generated per cpu request. More... | |

| unsigned int | countNumSeqPkts |

| Track number of sequential packets generated for a request More... | |

| Addr | addr |

| Address of request. More... | |

| bool | isRead |

| Remember type of requests to be generated in series. More... | |

| const unsigned int | pageSize |

| Page size of DRAM. More... | |

| const unsigned int | pageBits |

| Number of page bits in DRAM address. More... | |

| const unsigned int | bankBits |

| Number of bank bits in DRAM address. More... | |

| const unsigned int | blockBits |

| Number of block bits in DRAM address. More... | |

| const unsigned int | nbrOfBanksDRAM |

| Number of banks in DRAM. More... | |

| const unsigned int | nbrOfBanksUtil |

| Number of banks to be utilized for a given configuration. More... | |

| Enums::AddrMap | addrMapping |

| Address mapping to be used. More... | |

| const unsigned int | rankBits |

| Number of rank bits in DRAM address. More... | |

| const unsigned int | nbrOfRanks |

| Number of ranks to be utilized for a given configuration. More... | |

Protected Attributes inherited from RandomGen Protected Attributes inherited from RandomGen | |

| Addr | dataManipulated |

| Counter to determine the amount of data manipulated. More... | |

Protected Attributes inherited from StochasticGen Protected Attributes inherited from StochasticGen | |

| const Addr | startAddr |

| Start of address range. More... | |

| const Addr | endAddr |

| End of address range. More... | |

| const Addr | blocksize |

| Blocksize and address increment. More... | |

| const Addr | cacheLineSize |

| Cache line size in the simulated system. More... | |

| const Tick | minPeriod |

| Request generation period. More... | |

| const Tick | maxPeriod |

| const uint8_t | readPercent |

| Percent of generated transactions that should be reads. More... | |

| const Addr | dataLimit |

| Maximum amount of data to manipulate. More... | |

Protected Attributes inherited from BaseGen Protected Attributes inherited from BaseGen | |

| const std::string | _name |

| Name to use for status and debug printing. More... | |

| const RequestorID | requestorId |

| The RequestorID used for generating requests. More... | |

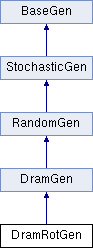

Detailed Description

Definition at line 53 of file dram_rot_gen.hh.

Constructor & Destructor Documentation

◆ DramRotGen()

|

inline |

Create a DRAM address sequence generator.

This sequence generator will rotate through: 1) Banks per rank 2) Command type (if applicable) 3) Ranks per channel

- Parameters

-

obj SimObject owning this sequence generator requestor_id RequestorID related to the memory requests _duration duration of this state before transitioning start_addr Start address end_addr End address _blocksize Size used for transactions injected cacheline_size cache line size in the system min_period Lower limit of random inter-transaction time max_period Upper limit of random inter-transaction time read_percent Percent of transactions that are reads data_limit Upper limit on how much data to read/write num_seq_pkts Number of packets per stride, each of _blocksize page_size Page size (bytes) used in the DRAM nbr_of_banks_DRAM Total number of banks in DRAM nbr_of_banks_util Number of banks to utilized, for N banks, we will use banks: 0->(N-1) nbr_of_ranks Number of ranks utilized, addr_mapping Address mapping to be used, assumes single channel system

Definition at line 85 of file dram_rot_gen.hh.

References BaseGen::_name, fatal, and StochasticGen::readPercent.

Member Function Documentation

◆ getNextPacket()

|

virtual |

Get the next generated packet.

- Returns

- A packet to be sent at the current tick

Reimplemented from DramGen.

Definition at line 48 of file dram_rot_gen.cc.

References DramGen::addr, DramGen::addrMapping, DramGen::bankBits, DramGen::blockBits, StochasticGen::blocksize, DramGen::countNumSeqPkts, RandomGen::dataManipulated, DPRINTF, DramGen::genStartAddr(), BaseGen::getPacket(), DramGen::isRead, maxSeqCountPerRank, DramGen::nbrOfBanksDRAM, DramGen::nbrOfBanksUtil, DramGen::nbrOfRanks, nextSeqCount, DramGen::numSeqPkts, DramGen::pageBits, DramGen::pageSize, DramGen::rankBits, StochasticGen::readPercent, MemCmd::ReadReq, replaceBits(), and MemCmd::WriteReq.

Member Data Documentation

◆ maxSeqCountPerRank

|

private |

Number of command series issued before the rank is changed.

Should rotate to the next rank after rorating throughall the banks for each specified command type

Definition at line 118 of file dram_rot_gen.hh.

Referenced by getNextPacket().

◆ nextSeqCount

|

private |

Next packet series count used to set rank and bank, and update isRead Incremented at the start of a new packet series

Definition at line 123 of file dram_rot_gen.hh.

Referenced by getNextPacket().

The documentation for this class was generated from the following files:

- cpu/testers/traffic_gen/dram_rot_gen.hh

- cpu/testers/traffic_gen/dram_rot_gen.cc