gem5::fastmodel::ResetControllerExample::Registers Class Reference

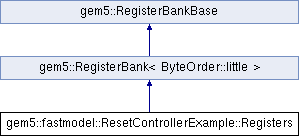

Inheritance diagram for gem5::fastmodel::ResetControllerExample::Registers:

Public Member Functions | |

| Registers (const std::string &, Iris::BaseCPU *, CorePins *) | |

| Public Member Functions inherited from gem5::RegisterBank< ByteOrder::little > | |

| void | setDebugFlag (const ::gem5::debug::SimpleFlag &flag) |

| constexpr | RegisterBank (const std::string &new_name, Addr new_base) |

| virtual | ~RegisterBank () |

| RegisterBank (RegisterBank &&)=default | |

| void | addRegisters (std::initializer_list< RegisterAdder > adders) |

| void | addRegistersAt (std::initializer_list< RegisterAdder > adders) |

| void | addRegister (RegisterAdder reg) |

| Addr | base () const |

| Addr | size () const |

| const std::string & | name () const |

| virtual void | read (Addr addr, void *buf, Addr bytes) |

| virtual void | write (Addr addr, const void *buf, Addr bytes) |

| virtual void | reset () |

Private Attributes | |

| Iris::BaseCPU * | cpu |

| CorePins * | pins |

| Register64 | nsrvbar |

| Register64 | rvbar |

| Register32 | reset |

| Register32 | halt |

Additional Inherited Members | |

| Public Types inherited from gem5::RegisterBank< ByteOrder::little > | |

| using | Register8 |

| using | Register8LE |

| using | Register8BE |

| using | Register16 |

| using | Register16LE |

| using | Register16BE |

| using | Register32 |

| using | Register32LE |

| using | Register32BE |

| using | Register64 |

| using | Register64LE |

| using | Register64BE |

| Static Public Member Functions inherited from gem5::RegisterBank< ByteOrder::little > | |

| static constexpr Data | readWithMask (const Data &value, const Data &bitmask) |

| static constexpr Data | writeWithMask (const Data &old, const Data &value, const Data &bitmask) |

Detailed Description

Definition at line 57 of file example.hh.

Constructor & Destructor Documentation

◆ Registers()

| gem5::fastmodel::ResetControllerExample::Registers::Registers | ( | const std::string & | module_name, |

| Iris::BaseCPU * | c, | ||

| CorePins * | p ) |

Definition at line 44 of file example.cc.

References gem5::RegisterBank< ByteOrder::little >::addRegisters(), gem5::ArmISA::c, cpu, halt, nsrvbar, gem5::MipsISA::p, panic_if, pins, gem5::X86ISA::reg, reset, rvbar, and gem5::X86ISA::val.

Member Data Documentation

◆ cpu

|

private |

Definition at line 60 of file example.hh.

Referenced by Registers().

◆ halt

|

private |

Definition at line 66 of file example.hh.

Referenced by Registers().

◆ nsrvbar

|

private |

Definition at line 63 of file example.hh.

Referenced by Registers().

◆ pins

|

private |

Definition at line 61 of file example.hh.

Referenced by Registers().

◆ reset

|

private |

Definition at line 65 of file example.hh.

Referenced by Registers().

◆ rvbar

|

private |

Definition at line 64 of file example.hh.

Referenced by Registers().

The documentation for this class was generated from the following files:

- arch/arm/fastmodel/reset_controller/example.hh

- arch/arm/fastmodel/reset_controller/example.cc

Generated on Sat Oct 18 2025 08:06:59 for gem5 by doxygen 1.14.0