Base class for predicated integer operations. More...

#include <pred_inst.hh>

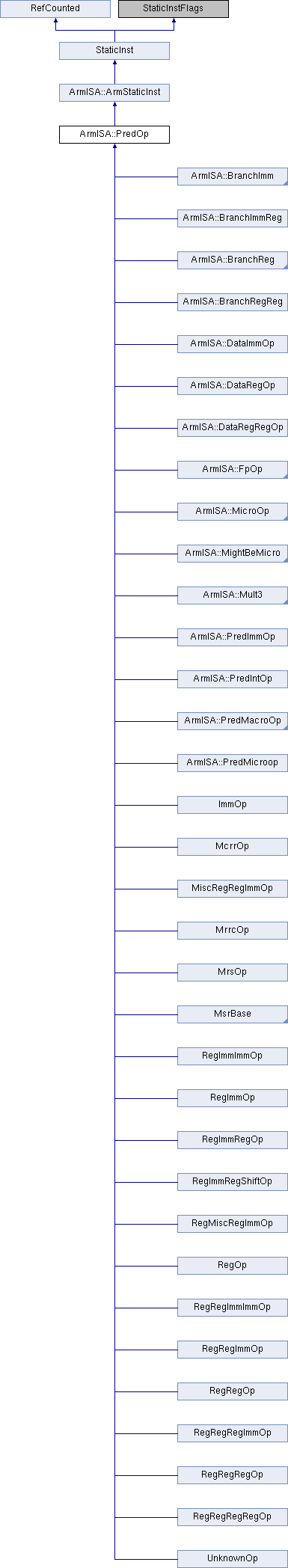

Inheritance diagram for ArmISA::PredOp:

Protected Member Functions | |

| PredOp (const char *mnem, ExtMachInst _machInst, OpClass __opClass) | |

| Constructor. More... | |

Protected Member Functions inherited from ArmISA::ArmStaticInst Protected Member Functions inherited from ArmISA::ArmStaticInst | |

| int32_t | shift_rm_imm (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| int32_t | shift_rm_rs (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| bool | shift_carry_imm (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| bool | shift_carry_rs (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| int64_t | shiftReg64 (uint64_t base, uint64_t shiftAmt, ArmShiftType type, uint8_t width) const |

| int64_t | extendReg64 (uint64_t base, ArmExtendType type, uint64_t shiftAmt, uint8_t width) const |

| ArmStaticInst (const char *mnem, ExtMachInst _machInst, OpClass __opClass) | |

| void | printIntReg (std::ostream &os, RegIndex reg_idx, uint8_t opWidth=0) const |

| Print a register name for disassembly given the unique dependence tag number (FP or int). More... | |

| void | printFloatReg (std::ostream &os, RegIndex reg_idx) const |

| void | printVecReg (std::ostream &os, RegIndex reg_idx, bool isSveVecReg=false) const |

| void | printVecPredReg (std::ostream &os, RegIndex reg_idx) const |

| void | printCCReg (std::ostream &os, RegIndex reg_idx) const |

| void | printMiscReg (std::ostream &os, RegIndex reg_idx) const |

| void | printMnemonic (std::ostream &os, const std::string &suffix="", bool withPred=true, bool withCond64=false, ConditionCode cond64=COND_UC) const |

| void | printTarget (std::ostream &os, Addr target, const Loader::SymbolTable *symtab) const |

| void | printCondition (std::ostream &os, unsigned code, bool noImplicit=false) const |

| void | printMemSymbol (std::ostream &os, const Loader::SymbolTable *symtab, const std::string &prefix, const Addr addr, const std::string &suffix) const |

| void | printShiftOperand (std::ostream &os, IntRegIndex rm, bool immShift, uint32_t shiftAmt, IntRegIndex rs, ArmShiftType type) const |

| void | printExtendOperand (bool firstOperand, std::ostream &os, IntRegIndex rm, ArmExtendType type, int64_t shiftAmt) const |

| void | printPFflags (std::ostream &os, int flag) const |

| void | printDataInst (std::ostream &os, bool withImm) const |

| void | printDataInst (std::ostream &os, bool withImm, bool immShift, bool s, IntRegIndex rd, IntRegIndex rn, IntRegIndex rm, IntRegIndex rs, uint32_t shiftAmt, ArmShiftType type, uint64_t imm) const |

| void | advancePC (PCState &pcState) const override |

| std::string | generateDisassembly (Addr pc, const Loader::SymbolTable *symtab) const override |

| Internal function to generate disassembly string. More... | |

| Fault | disabledFault () const |

| bool | isWFxTrapping (ThreadContext *tc, ExceptionLevel targetEL, bool isWfe) const |

| Fault | softwareBreakpoint32 (ExecContext *xc, uint16_t imm) const |

| Trigger a Software Breakpoint. More... | |

| Fault | advSIMDFPAccessTrap64 (ExceptionLevel el) const |

| Trap an access to Advanced SIMD or FP registers due to access control bits. More... | |

| Fault | checkFPAdvSIMDTrap64 (ThreadContext *tc, CPSR cpsr) const |

| Check an Advaned SIMD access against CPTR_EL2 and CPTR_EL3. More... | |

| Fault | checkFPAdvSIMDEnabled64 (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check an Advaned SIMD access against CPACR_EL1, CPTR_EL2, and CPTR_EL3. More... | |

| Fault | checkAdvSIMDOrFPEnabled32 (ThreadContext *tc, CPSR cpsr, CPACR cpacr, NSACR nsacr, FPEXC fpexc, bool fpexc_check, bool advsimd) const |

| Check if a VFP/SIMD access from aarch32 should be allowed. More... | |

| Fault | checkForWFxTrap32 (ThreadContext *tc, ExceptionLevel tgtEl, bool isWfe) const |

| Check if WFE/WFI instruction execution in aarch32 should be trapped. More... | |

| Fault | checkForWFxTrap64 (ThreadContext *tc, ExceptionLevel tgtEl, bool isWfe) const |

| Check if WFE/WFI instruction execution in aarch64 should be trapped. More... | |

| Fault | trapWFx (ThreadContext *tc, CPSR cpsr, SCR scr, bool isWfe) const |

| WFE/WFI trapping helper function. More... | |

| Fault | checkSETENDEnabled (ThreadContext *tc, CPSR cpsr) const |

| Check if SETEND instruction execution in aarch32 should be trapped. More... | |

| Fault | undefinedFault32 (ThreadContext *tc, ExceptionLevel el) const |

| UNDEFINED behaviour in AArch32. More... | |

| Fault | undefinedFault64 (ThreadContext *tc, ExceptionLevel el) const |

| UNDEFINED behaviour in AArch64. More... | |

| Fault | sveAccessTrap (ExceptionLevel el) const |

| Trap an access to SVE registers due to access control bits. More... | |

| Fault | checkSveEnabled (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check an SVE access against CPACR_EL1, CPTR_EL2, and CPTR_EL3. More... | |

| CPSR | getPSTATEFromPSR (ThreadContext *tc, CPSR cpsr, CPSR spsr) const |

| Get the new PSTATE from a SPSR register in preparation for an exception return. More... | |

| bool | generalExceptionsToAArch64 (ThreadContext *tc, ExceptionLevel pstateEL) const |

| Return true if exceptions normally routed to EL1 are being handled at an Exception level using AArch64, because either EL1 is using AArch64 or TGE is in force and EL2 is using AArch64. More... | |

Protected Member Functions inherited from StaticInst Protected Member Functions inherited from StaticInst | |

| StaticInst (const char *_mnemonic, ExtMachInst _machInst, OpClass __opClass) | |

| Constructor. More... | |

| template<typename T > | |

| size_t | simpleAsBytes (void *buf, size_t max_size, const T &t) |

Protected Attributes | |

| ConditionCode | condCode |

Protected Attributes inherited from ArmISA::ArmStaticInst Protected Attributes inherited from ArmISA::ArmStaticInst | |

| bool | aarch64 |

| uint8_t | intWidth |

Protected Attributes inherited from StaticInst Protected Attributes inherited from StaticInst | |

| std::bitset< Num_Flags > | flags |

| Flag values for this instruction. More... | |

| OpClass | _opClass |

| See opClass(). More... | |

| int8_t | _numSrcRegs |

| See numSrcRegs(). More... | |

| int8_t | _numDestRegs |

| See numDestRegs(). More... | |

| int8_t | _numFPDestRegs |

| The following are used to track physical register usage for machines with separate int & FP reg files. More... | |

| int8_t | _numIntDestRegs |

| int8_t | _numCCDestRegs |

| int8_t | _numVecDestRegs |

| To use in architectures with vector register file. More... | |

| int8_t | _numVecElemDestRegs |

| int8_t | _numVecPredDestRegs |

| RegId | _destRegIdx [MaxInstDestRegs] |

| See destRegIdx(). More... | |

| RegId | _srcRegIdx [MaxInstSrcRegs] |

| See srcRegIdx(). More... | |

| const char * | mnemonic |

| Base mnemonic (e.g., "add"). More... | |

| std::string * | cachedDisassembly |

| String representation of disassembly (lazily evaluated via disassemble()). More... | |

Additional Inherited Members | |

Public Types inherited from StaticInst Public Types inherited from StaticInst | |

| enum | { MaxInstSrcRegs = TheISA::MaxInstSrcRegs, MaxInstDestRegs = TheISA::MaxInstDestRegs } |

| typedef TheISA::ExtMachInst | ExtMachInst |

| Binary extended machine instruction type. More... | |

Public Member Functions inherited from ArmISA::ArmStaticInst Public Member Functions inherited from ArmISA::ArmStaticInst | |

| virtual void | annotateFault (ArmFault *fault) |

| uint8_t | getIntWidth () const |

| ssize_t | instSize () const |

| Returns the byte size of current instruction. More... | |

| MachInst | encoding () const |

| Returns the real encoding of the instruction: the machInst field is in fact always 64 bit wide and contains some instruction metadata, which means it differs from the real opcode. More... | |

| size_t | asBytes (void *buf, size_t max_size) override |

| Instruction classes can override this function to return a a representation of themselves as a blob of bytes, generally assumed to be that instructions ExtMachInst. More... | |

Public Member Functions inherited from StaticInst Public Member Functions inherited from StaticInst | |

| int8_t | numSrcRegs () const |

| Number of source registers. More... | |

| int8_t | numDestRegs () const |

| Number of destination registers. More... | |

| int8_t | numFPDestRegs () const |

| Number of floating-point destination regs. More... | |

| int8_t | numIntDestRegs () const |

| Number of integer destination regs. More... | |

| int8_t | numVecDestRegs () const |

| Number of vector destination regs. More... | |

| int8_t | numVecElemDestRegs () const |

| Number of vector element destination regs. More... | |

| int8_t | numVecPredDestRegs () const |

| Number of predicate destination regs. More... | |

| int8_t | numCCDestRegs () const |

| Number of coprocesor destination regs. More... | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isCC () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isCondDelaySlot () const |

| bool | isThreadSync () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isMemBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isIprAccess () const |

| bool | isUnverifiable () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isMicroBranch () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isHtmCmd () const |

| void | setFirstMicroop () |

| void | setLastMicroop () |

| void | setDelayedCommit () |

| void | setFlag (Flags f) |

| OpClass | opClass () const |

| Operation class. Used to select appropriate function unit in issue. More... | |

| const RegId & | destRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th destination reg. More... | |

| const RegId & | srcRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th source reg. More... | |

| virtual | ~StaticInst () |

| virtual Fault | execute (ExecContext *xc, Trace::InstRecord *traceData) const =0 |

| virtual Fault | initiateAcc (ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual Fault | completeAcc (Packet *pkt, ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual void | advancePC (TheISA::PCState &pcState) const =0 |

| virtual StaticInstPtr | fetchMicroop (MicroPC upc) const |

| Return the microop that goes with a particular micropc. More... | |

| virtual TheISA::PCState | branchTarget (const TheISA::PCState &pc) const |

| Return the target address for a PC-relative branch. More... | |

| virtual TheISA::PCState | branchTarget (ThreadContext *tc) const |

| Return the target address for an indirect branch (jump). More... | |

| bool | hasBranchTarget (const TheISA::PCState &pc, ThreadContext *tc, TheISA::PCState &tgt) const |

| Return true if the instruction is a control transfer, and if so, return the target address as well. More... | |

| virtual const std::string & | disassemble (Addr pc, const Loader::SymbolTable *symtab=nullptr) const |

| Return string representation of disassembled instruction. More... | |

| void | printFlags (std::ostream &outs, const std::string &separator) const |

| Print a separator separated list of this instruction's set flag names on the given stream. More... | |

| std::string | getName () |

| Return name of machine instruction. More... | |

Public Member Functions inherited from RefCounted Public Member Functions inherited from RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. More... | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. More... | |

| void | incref () const |

| Increment the reference count. More... | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. More... | |

Static Public Member Functions inherited from ArmISA::ArmStaticInst Static Public Member Functions inherited from ArmISA::ArmStaticInst | |

| static unsigned | getCurSveVecLenInBits (ThreadContext *tc) |

| static unsigned | getCurSveVecLenInQWords (ThreadContext *tc) |

| template<typename T > | |

| static unsigned | getCurSveVecLen (ThreadContext *tc) |

Public Attributes inherited from StaticInst Public Attributes inherited from StaticInst | |

| const ExtMachInst | machInst |

| The binary machine instruction. More... | |

Static Public Attributes inherited from StaticInst Static Public Attributes inherited from StaticInst | |

| static StaticInstPtr | nullStaticInstPtr |

| Pointer to a statically allocated "null" instruction object. More... | |

| static StaticInstPtr | nopStaticInstPtr = new NopStaticInst |

| Pointer to a statically allocated generic "nop" instruction object. More... | |

Static Protected Member Functions inherited from ArmISA::ArmStaticInst Static Protected Member Functions inherited from ArmISA::ArmStaticInst | |

| template<int width> | |

| static bool | saturateOp (int32_t &res, int64_t op1, int64_t op2, bool sub=false) |

| static bool | satInt (int32_t &res, int64_t op, int width) |

| template<int width> | |

| static bool | uSaturateOp (uint32_t &res, int64_t op1, int64_t op2, bool sub=false) |

| static bool | uSatInt (int32_t &res, int64_t op, int width) |

| static void | activateBreakpoint (ThreadContext *tc) |

| static uint32_t | cpsrWriteByInstr (CPSR cpsr, uint32_t val, SCR scr, NSACR nsacr, uint8_t byteMask, bool affectState, bool nmfi, ThreadContext *tc) |

| static uint32_t | spsrWriteByInstr (uint32_t spsr, uint32_t val, uint8_t byteMask, bool affectState) |

| static Addr | readPC (ExecContext *xc) |

| static void | setNextPC (ExecContext *xc, Addr val) |

| template<class T > | |

| static T | cSwap (T val, bool big) |

| template<class T , class E > | |

| static T | cSwap (T val, bool big) |

| static void | setIWNextPC (ExecContext *xc, Addr val) |

| static void | setAIWNextPC (ExecContext *xc, Addr val) |

Detailed Description

Base class for predicated integer operations.

Definition at line 210 of file pred_inst.hh.

Constructor & Destructor Documentation

◆ PredOp()

|

inlineprotected |

Constructor.

Definition at line 217 of file pred_inst.hh.

References ArmISA::COND_UC, condCode, and StaticInst::machInst.

Member Data Documentation

◆ condCode

|

protected |

Definition at line 214 of file pred_inst.hh.

Referenced by ArmISA::BranchImmCond::BranchImmCond(), ArmISA::BranchRegCond::BranchRegCond(), ArmISA::MacroMemOp::MacroMemOp(), and PredOp().

The documentation for this class was generated from the following file:

- arch/arm/insts/pred_inst.hh