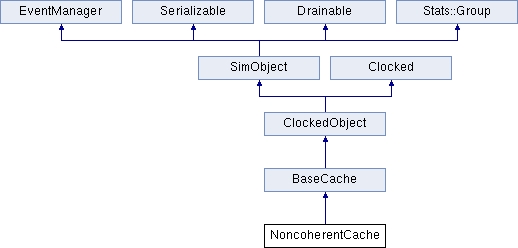

A non-coherent cache. More...

#include <noncoherent_cache.hh>

Public Member Functions | |

| NoncoherentCache (const NoncoherentCacheParams *p) | |

Public Member Functions inherited from BaseCache Public Member Functions inherited from BaseCache | |

| void | regProbePoints () override |

| Registers probes. More... | |

| BaseCache (const BaseCacheParams *p, unsigned blk_size) | |

| ~BaseCache () | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. More... | |

| unsigned | getBlockSize () const |

| Query block size of a cache. More... | |

| const AddrRangeList & | getAddrRanges () const |

| MSHR * | allocateMissBuffer (PacketPtr pkt, Tick time, bool sched_send=true) |

| void | allocateWriteBuffer (PacketPtr pkt, Tick time) |

| bool | isBlocked () const |

| Returns true if the cache is blocked for accesses. More... | |

| void | setBlocked (BlockedCause cause) |

| Marks the access path of the cache as blocked for the given cause. More... | |

| void | clearBlocked (BlockedCause cause) |

| Marks the cache as unblocked for the given cause. More... | |

| void | schedMemSideSendEvent (Tick time) |

| Schedule a send event for the memory-side port. More... | |

| bool | inCache (Addr addr, bool is_secure) const |

| bool | hasBeenPrefetched (Addr addr, bool is_secure) const |

| bool | inMissQueue (Addr addr, bool is_secure) const |

| void | incMissCount (PacketPtr pkt) |

| void | incHitCount (PacketPtr pkt) |

| bool | coalesce () const |

| Checks if the cache is coalescing writes. More... | |

| void | writebackVisitor (CacheBlk &blk) |

| Cache block visitor that writes back dirty cache blocks using functional writes. More... | |

| void | invalidateVisitor (CacheBlk &blk) |

| Cache block visitor that invalidates all blocks in the cache. More... | |

| virtual bool | sendMSHRQueuePacket (MSHR *mshr) |

| Take an MSHR, turn it into a suitable downstream packet, and send it out. More... | |

| bool | sendWriteQueuePacket (WriteQueueEntry *wq_entry) |

| Similar to sendMSHR, but for a write-queue entry instead. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize the state of the caches. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from ClockedObject Public Member Functions inherited from ClockedObject | |

| ClockedObject (const ClockedObjectParams *p) | |

| const Params * | params () const |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from SimObject Public Member Functions inherited from SimObject | |

| const Params * | params () const |

| SimObject (const Params *_params) | |

| virtual | ~SimObject () |

| virtual const std::string | name () const |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from EventManager Public Member Functions inherited from EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. More... | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. More... | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from Drainable Public Member Functions inherited from Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Public Member Functions inherited from Stats::Group Public Member Functions inherited from Stats::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. More... | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. More... | |

| virtual void | resetStats () |

| Callback to reset stats. More... | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. More... | |

| void | addStat (Stats::Info *info) |

| Register a stat with this group. More... | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. More... | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. More... | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. More... | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. More... | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

Public Member Functions inherited from Clocked Public Member Functions inherited from Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| bool | access (PacketPtr pkt, CacheBlk *&blk, Cycles &lat, PacketList &writebacks) override |

| Does all the processing necessary to perform the provided request. More... | |

| void | handleTimingReqMiss (PacketPtr pkt, CacheBlk *blk, Tick forward_time, Tick request_time) override |

| void | recvTimingReq (PacketPtr pkt) override |

| Performs the access specified by the request. More... | |

| void | doWritebacks (PacketList &writebacks, Tick forward_time) override |

| Insert writebacks into the write buffer. More... | |

| void | doWritebacksAtomic (PacketList &writebacks) override |

| Send writebacks down the memory hierarchy in atomic mode. More... | |

| void | serviceMSHRTargets (MSHR *mshr, const PacketPtr pkt, CacheBlk *blk) override |

| Service non-deferred MSHR targets using the received response. More... | |

| void | recvTimingResp (PacketPtr pkt) override |

| Handles a response (cache line fill/write ack) from the bus. More... | |

| void | recvTimingSnoopReq (PacketPtr pkt) override |

| Snoops bus transactions to maintain coherence. More... | |

| void | recvTimingSnoopResp (PacketPtr pkt) override |

| Handle a snoop response. More... | |

| Cycles | handleAtomicReqMiss (PacketPtr pkt, CacheBlk *&blk, PacketList &writebacks) override |

| Handle a request in atomic mode that missed in this cache. More... | |

| Tick | recvAtomic (PacketPtr pkt) override |

| Performs the access specified by the request. More... | |

| Tick | recvAtomicSnoop (PacketPtr pkt) override |

| Snoop for the provided request in the cache and return the estimated time taken. More... | |

| void | functionalAccess (PacketPtr pkt, bool from_cpu_side) override |

| Performs the access specified by the request. More... | |

| void | satisfyRequest (PacketPtr pkt, CacheBlk *blk, bool deferred_response=false, bool pending_downgrade=false) override |

| Perform any necessary updates to the block and perform any data exchange between the packet and the block. More... | |

| PacketPtr | createMissPacket (PacketPtr cpu_pkt, CacheBlk *blk, bool needs_writable, bool is_whole_line_write) const override |

| Create an appropriate downstream bus request packet. More... | |

| M5_NODISCARD PacketPtr | evictBlock (CacheBlk *blk) override |

| Evict a cache block. More... | |

Protected Member Functions inherited from BaseCache Protected Member Functions inherited from BaseCache | |

| void | markInService (MSHR *mshr, bool pending_modified_resp) |

| Mark a request as in service (sent downstream in the memory system), effectively making this MSHR the ordering point. More... | |

| void | markInService (WriteQueueEntry *entry) |

| bool | allocOnFill (MemCmd cmd) const |

| Determine whether we should allocate on a fill or not. More... | |

| Addr | regenerateBlkAddr (CacheBlk *blk) |

| Regenerate block address using tags. More... | |

| Cycles | calculateTagOnlyLatency (const uint32_t delay, const Cycles lookup_lat) const |

| Calculate latency of accesses that only touch the tag array. More... | |

| Cycles | calculateAccessLatency (const CacheBlk *blk, const uint32_t delay, const Cycles lookup_lat) const |

| Calculate access latency in ticks given a tag lookup latency, and whether access was a hit or miss. More... | |

| virtual void | handleTimingReqHit (PacketPtr pkt, CacheBlk *blk, Tick request_time) |

| void | handleTimingReqMiss (PacketPtr pkt, MSHR *mshr, CacheBlk *blk, Tick forward_time, Tick request_time) |

| void | handleUncacheableWriteResp (PacketPtr pkt) |

| Handling the special case of uncacheable write responses to make recvTimingResp less cluttered. More... | |

| void | cmpAndSwap (CacheBlk *blk, PacketPtr pkt) |

| Handle doing the Compare and Swap function for SPARC. More... | |

| QueueEntry * | getNextQueueEntry () |

| Return the next queue entry to service, either a pending miss from the MSHR queue, a buffered write from the write buffer, or something from the prefetcher. More... | |

| void | writebackTempBlockAtomic () |

| Send the outstanding tempBlock writeback. More... | |

| bool | updateCompressionData (CacheBlk *blk, const uint64_t *data, PacketList &writebacks) |

| When a block is overwriten, its compression information must be updated, and it may need to be recompressed. More... | |

| void | maintainClusivity (bool from_cache, CacheBlk *blk) |

| Maintain the clusivity of this cache by potentially invalidating a block. More... | |

| bool | handleEvictions (std::vector< CacheBlk * > &evict_blks, PacketList &writebacks) |

| Try to evict the given blocks. More... | |

| CacheBlk * | handleFill (PacketPtr pkt, CacheBlk *blk, PacketList &writebacks, bool allocate) |

| Handle a fill operation caused by a received packet. More... | |

| CacheBlk * | allocateBlock (const PacketPtr pkt, PacketList &writebacks) |

| Allocate a new block and perform any necessary writebacks. More... | |

| void | evictBlock (CacheBlk *blk, PacketList &writebacks) |

| Evict a cache block. More... | |

| void | invalidateBlock (CacheBlk *blk) |

| Invalidate a cache block. More... | |

| PacketPtr | writebackBlk (CacheBlk *blk) |

| Create a writeback request for the given block. More... | |

| PacketPtr | writecleanBlk (CacheBlk *blk, Request::Flags dest, PacketId id) |

| Create a writeclean request for the given block. More... | |

| virtual void | memWriteback () override |

| Write back dirty blocks in the cache using functional accesses. More... | |

| virtual void | memInvalidate () override |

| Invalidates all blocks in the cache. More... | |

| bool | isDirty () const |

| Determine if there are any dirty blocks in the cache. More... | |

| bool | inRange (Addr addr) const |

| Determine if an address is in the ranges covered by this cache. More... | |

| Tick | nextQueueReadyTime () const |

| Find next request ready time from among possible sources. More... | |

Protected Member Functions inherited from Drainable Protected Member Functions inherited from Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. More... | |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from Clocked Protected Member Functions inherited from Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. More... | |

Additional Inherited Members | |

Public Types inherited from BaseCache Public Types inherited from BaseCache | |

| enum | BlockedCause { Blocked_NoMSHRs = MSHRQueue_MSHRs, Blocked_NoWBBuffers = MSHRQueue_WriteBuffer, Blocked_NoTargets, NUM_BLOCKED_CAUSES } |

| Reasons for caches to be blocked. More... | |

Public Types inherited from ClockedObject Public Types inherited from ClockedObject | |

| typedef ClockedObjectParams | Params |

| Parameters of ClockedObject. More... | |

Public Types inherited from SimObject Public Types inherited from SimObject | |

| typedef SimObjectParams | Params |

Static Public Member Functions inherited from SimObject Static Public Member Functions inherited from SimObject | |

| static void | serializeAll (CheckpointOut &cp) |

| Serialize all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| Serializes all the SimObjects. More... | |

| static void | unserializeGlobals (CheckpointIn &cp) |

Public Attributes inherited from BaseCache Public Attributes inherited from BaseCache | |

| System * | system |

| System we are currently operating in. More... | |

| BaseCache::CacheStats | stats |

Public Attributes inherited from ClockedObject Public Attributes inherited from ClockedObject | |

| PowerState * | powerState |

Protected Types inherited from BaseCache Protected Types inherited from BaseCache | |

| enum | MSHRQueueIndex { MSHRQueue_MSHRs, MSHRQueue_WriteBuffer } |

| Indexes to enumerate the MSHR queues. More... | |

Protected Attributes inherited from BaseCache Protected Attributes inherited from BaseCache | |

| CpuSidePort | cpuSidePort |

| MemSidePort | memSidePort |

| MSHRQueue | mshrQueue |

| Miss status registers. More... | |

| WriteQueue | writeBuffer |

| Write/writeback buffer. More... | |

| BaseTags * | tags |

| Tag and data Storage. More... | |

| Compressor::Base * | compressor |

| Compression method being used. More... | |

| Prefetcher::Base * | prefetcher |

| Prefetcher. More... | |

| ProbePointArg< PacketPtr > * | ppHit |

| To probe when a cache hit occurs. More... | |

| ProbePointArg< PacketPtr > * | ppMiss |

| To probe when a cache miss occurs. More... | |

| ProbePointArg< PacketPtr > * | ppFill |

| To probe when a cache fill occurs. More... | |

| WriteAllocator *const | writeAllocator |

| The writeAllocator drive optimizations for streaming writes. More... | |

| TempCacheBlk * | tempBlock |

| Temporary cache block for occasional transitory use. More... | |

| std::unique_ptr< Packet > | pendingDelete |

| Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call. More... | |

| const bool | writebackClean |

| Determine if clean lines should be written back or not. More... | |

| PacketPtr | tempBlockWriteback |

| Writebacks from the tempBlock, resulting on the response path in atomic mode, must happen after the call to recvAtomic has finished (for the right ordering of the packets). More... | |

| EventFunctionWrapper | writebackTempBlockAtomicEvent |

| An event to writeback the tempBlock after recvAtomic finishes. More... | |

| const unsigned | blkSize |

| Block size of this cache. More... | |

| const Cycles | lookupLatency |

| The latency of tag lookup of a cache. More... | |

| const Cycles | dataLatency |

| The latency of data access of a cache. More... | |

| const Cycles | forwardLatency |

| This is the forward latency of the cache. More... | |

| const Cycles | fillLatency |

| The latency to fill a cache block. More... | |

| const Cycles | responseLatency |

| The latency of sending reponse to its upper level cache/core on a linefill. More... | |

| const bool | sequentialAccess |

| Whether tags and data are accessed sequentially. More... | |

| const int | numTarget |

| The number of targets for each MSHR. More... | |

| bool | forwardSnoops |

| Do we forward snoops from mem side port through to cpu side port? More... | |

| const Enums::Clusivity | clusivity |

| Clusivity with respect to the upstream cache, determining if we fill into both this cache and the cache above on a miss. More... | |

| const bool | isReadOnly |

| Is this cache read only, for example the instruction cache, or table-walker cache. More... | |

| uint8_t | blocked |

| Bit vector of the blocking reasons for the access path. More... | |

| uint64_t | order |

| Increasing order number assigned to each incoming request. More... | |

| Cycles | blockedCycle |

| Stores time the cache blocked for statistics. More... | |

| MSHR * | noTargetMSHR |

| Pointer to the MSHR that has no targets. More... | |

| Counter | missCount |

| The number of misses to trigger an exit event. More... | |

| const AddrRangeList | addrRanges |

| The address range to which the cache responds on the CPU side. More... | |

Protected Attributes inherited from SimObject Protected Attributes inherited from SimObject | |

| const SimObjectParams * | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from EventManager Protected Attributes inherited from EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

Detailed Description

A non-coherent cache.

Definition at line 64 of file noncoherent_cache.hh.

Constructor & Destructor Documentation

◆ NoncoherentCache()

| NoncoherentCache::NoncoherentCache | ( | const NoncoherentCacheParams * | p | ) |

Definition at line 59 of file noncoherent_cache.cc.

Member Function Documentation

◆ access()

|

overrideprotectedvirtual |

Does all the processing necessary to perform the provided request.

- Parameters

-

pkt The memory request to perform. blk The cache block to be updated. lat The latency of the access. writebacks List for any writebacks that need to be performed.

- Returns

- Boolean indicating whether the request was satisfied.

Reimplemented from BaseCache.

Definition at line 75 of file noncoherent_cache.cc.

References BaseCache::access(), BlkWritable, Packet::cmd, CacheBlk::isValid(), Packet::isWriteback(), CacheBlk::status, and MemCmd::WriteClean.

◆ createMissPacket()

|

overrideprotectedvirtual |

Create an appropriate downstream bus request packet.

Creates a new packet with the request to be send to the memory below, or nullptr if the current request in cpu_pkt should just be forwarded on.

- Parameters

-

cpu_pkt The miss packet that needs to be satisfied. blk The referenced block, can be nullptr. needs_writable Indicates that the block must be writable even if the request in cpu_pkt doesn't indicate that. is_whole_line_write True if there are writes for the whole line

- Returns

- A packet send to the memory below

Implements BaseCache.

Definition at line 142 of file noncoherent_cache.cc.

References Packet::allocate(), BaseCache::blkSize, DPRINTF, Packet::getAddr(), Packet::getBlockAddr(), CacheBlk::isValid(), Packet::needsResponse(), Packet::print(), MemCmd::ReadReq, and Packet::req.

Referenced by handleAtomicReqMiss().

◆ doWritebacks()

|

overrideprotectedvirtual |

Insert writebacks into the write buffer.

Implements BaseCache.

Definition at line 93 of file noncoherent_cache.cc.

References BaseCache::allocateWriteBuffer().

◆ doWritebacksAtomic()

|

overrideprotectedvirtual |

Send writebacks down the memory hierarchy in atomic mode.

Implements BaseCache.

Definition at line 103 of file noncoherent_cache.cc.

References BaseCache::memSidePort, and RequestPort::sendAtomic().

◆ evictBlock()

Evict a cache block.

Performs a writeback if necesssary and invalidates the block

- Parameters

-

blk Block to invalidate

- Returns

- A packet with the writeback, can be nullptr

Implements BaseCache.

Definition at line 330 of file noncoherent_cache.cc.

References BaseCache::invalidateBlock(), CacheBlk::isDirty(), BaseCache::writebackBlk(), and BaseCache::writebackClean.

◆ functionalAccess()

|

overrideprotectedvirtual |

Performs the access specified by the request.

- Parameters

-

pkt The request to perform. fromCpuSide from the CPU side port or the memory side port

Reimplemented from BaseCache.

Definition at line 228 of file noncoherent_cache.cc.

References BaseCache::functionalAccess(), and panic_if.

◆ handleAtomicReqMiss()

|

overrideprotectedvirtual |

Handle a request in atomic mode that missed in this cache.

Creates a downstream request, sends it to the memory below and handles the response. As we are in atomic mode all operations are performed immediately.

- Parameters

-

pkt The packet with the requests blk The referenced block writebacks A list with packets for any performed writebacks

- Returns

- Cycles for handling the request

Implements BaseCache.

Definition at line 166 of file noncoherent_cache.cc.

References BaseCache::allocOnFill(), BaseCache::blkSize, Packet::cmd, Packet::copyError(), createMissPacket(), DPRINTF, Packet::getAddr(), BaseCache::handleFill(), Packet::hasSharers(), Packet::isError(), Packet::isInvalidate(), Packet::isRead(), Packet::isResponse(), Packet::isWholeLineWrite(), Packet::isWriteback(), BaseCache::maintainClusivity(), Packet::makeAtomicResponse(), BaseCache::memSidePort, Packet::needsResponse(), Packet::print(), satisfyRequest(), RequestPort::sendAtomic(), Clocked::ticksToCycles(), MemCmd::UpgradeResp, and MemCmd::WriteClean.

◆ handleTimingReqMiss()

|

overrideprotectedvirtual |

Implements BaseCache.

Definition at line 114 of file noncoherent_cache.cc.

References BaseCache::blkSize, Queue< Entry >::findMatch(), Packet::getBlockAddr(), BaseCache::handleTimingReqMiss(), Packet::isSecure(), CacheBlk::isValid(), and BaseCache::mshrQueue.

◆ recvAtomic()

Performs the access specified by the request.

- Parameters

-

pkt The request to perform.

- Returns

- The number of ticks required for the access.

Reimplemented from BaseCache.

Definition at line 215 of file noncoherent_cache.cc.

References Packet::cacheResponding(), Packet::isRead(), Packet::isWrite(), panic_if, and BaseCache::recvAtomic().

◆ recvAtomicSnoop()

Snoop for the provided request in the cache and return the estimated time taken.

- Parameters

-

pkt The memory request to snoop

- Returns

- The number of ticks required for the snoop.

Implements BaseCache.

Definition at line 99 of file noncoherent_cache.hh.

References panic, and Packet::print().

◆ recvTimingReq()

|

overrideprotectedvirtual |

Performs the access specified by the request.

- Parameters

-

pkt The request to perform.

Reimplemented from BaseCache.

Definition at line 130 of file noncoherent_cache.cc.

References Packet::cacheResponding(), Packet::isRead(), Packet::isWrite(), panic_if, and BaseCache::recvTimingReq().

◆ recvTimingResp()

|

overrideprotectedvirtual |

Handles a response (cache line fill/write ack) from the bus.

- Parameters

-

pkt The response packet

Reimplemented from BaseCache.

Definition at line 312 of file noncoherent_cache.cc.

References Packet::cmd, Packet::hasSharers(), Packet::isInvalidate(), Packet::isRead(), Packet::isResponse(), BaseCache::recvTimingResp(), and MemCmd::UpgradeResp.

◆ recvTimingSnoopReq()

|

inlineoverrideprotectedvirtual |

Snoops bus transactions to maintain coherence.

- Parameters

-

pkt The current bus transaction.

Implements BaseCache.

Definition at line 86 of file noncoherent_cache.hh.

References panic, and Packet::print().

◆ recvTimingSnoopResp()

|

inlineoverrideprotectedvirtual |

Handle a snoop response.

- Parameters

-

pkt Snoop response packet

Implements BaseCache.

Definition at line 90 of file noncoherent_cache.hh.

References panic, and Packet::print().

◆ satisfyRequest()

|

overrideprotectedvirtual |

Perform any necessary updates to the block and perform any data exchange between the packet and the block.

The flags of the packet are also set accordingly.

- Parameters

-

pkt Request packet from upstream that hit a block blk Cache block that the packet hit deferred_response Whether this request originally missed pending_downgrade Whether the writable flag is to be removed

Reimplemented from BaseCache.

Definition at line 65 of file noncoherent_cache.cc.

References Packet::isRead(), Packet::isWrite(), and BaseCache::satisfyRequest().

Referenced by handleAtomicReqMiss(), and serviceMSHRTargets().

◆ serviceMSHRTargets()

|

overrideprotectedvirtual |

Service non-deferred MSHR targets using the received response.

Iterates through the list of targets that can be serviced with the current response.

- Parameters

-

mshr The MSHR that corresponds to the reponse pkt The response packet blk The reference block

Implements BaseCache.

Definition at line 237 of file noncoherent_cache.cc.

References BlkHWPrefetched, BaseCache::blkSize, Clocked::clockEdge(), Packet::cmd, BaseCache::CacheStats::cmdStats(), Packet::copyError(), BaseCache::cpuSidePort, MSHR::extractServiceableTargets(), MSHR::Target::FromCPU, MSHR::Target::FromPrefetcher, MSHR::getNumTargets(), Packet::getOffset(), MSHR::getTarget(), MemCmd::HardPFReq, Packet::headerDelay, Packet::isError(), Packet::makeTimingResponse(), System::maxRequestors(), BaseCache::CacheCmdStats::missLatency, panic, Packet::payloadDelay, QueueEntry::Target::pkt, Packet::req, BaseCache::responseLatency, satisfyRequest(), QueuedResponsePort::schedTimingResp(), BaseCache::stats, CacheBlk::status, and BaseCache::system.

The documentation for this class was generated from the following files:

- mem/cache/noncoherent_cache.hh

- mem/cache/noncoherent_cache.cc