#include <dramsim2.hh>

Classes | |

| class | MemoryPort |

| The memory port has to deal with its own flow control to avoid having unbounded storage that is implicitly created in the port itself. More... | |

Public Types | |

| typedef DRAMSim2Params | Params |

Public Types inherited from AbstractMemory Public Types inherited from AbstractMemory | |

| typedef AbstractMemoryParams | Params |

Public Types inherited from ClockedObject Public Types inherited from ClockedObject | |

| typedef ClockedObjectParams | Params |

| Parameters of ClockedObject. More... | |

Public Types inherited from SimObject Public Types inherited from SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| DRAMSim2 (const Params *p) | |

| void | readComplete (unsigned id, uint64_t addr, uint64_t cycle) |

| Read completion callback. More... | |

| void | writeComplete (unsigned id, uint64_t addr, uint64_t cycle) |

| Write completion callback. More... | |

| DrainState | drain () override |

| Notify an object that it needs to drain its state. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. More... | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| void | startup () override |

| startup() is the final initialization call before simulation. More... | |

Public Member Functions inherited from AbstractMemory Public Member Functions inherited from AbstractMemory | |

| AbstractMemory (const Params *p) | |

| virtual | ~AbstractMemory () |

| void | initState () override |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| bool | isNull () const |

| See if this is a null memory that should never store data and always return zero. More... | |

| void | setBackingStore (uint8_t *pmem_addr) |

| Set the host memory backing store to be used by this memory controller. More... | |

| const std::list< LockedAddr > & | getLockedAddrList () const |

| Get the list of locked addresses to allow checkpointing. More... | |

| void | addLockedAddr (LockedAddr addr) |

| Add a locked address to allow for checkpointing. More... | |

| System * | system () const |

| read the system pointer Implemented for completeness with the setter More... | |

| void | system (System *sys) |

| Set the system pointer on this memory This can't be done via a python parameter because the system needs pointers to all the memories and the reverse would create a cycle in the object graph. More... | |

| const Params * | params () const |

| AddrRange | getAddrRange () const |

| Get the address range. More... | |

| uint8_t * | toHostAddr (Addr addr) const |

| Transform a gem5 address space address into its physical counterpart in the host address space. More... | |

| uint64_t | size () const |

| Get the memory size. More... | |

| Addr | start () const |

| Get the start address. More... | |

| bool | isConfReported () const |

| Should this memory be passed to the kernel and part of the OS physical memory layout. More... | |

| bool | isInAddrMap () const |

| Some memories are used as shadow memories or should for other reasons not be part of the global address map. More... | |

| bool | isKvmMap () const |

| When shadow memories are in use, KVM may want to make one or the other, but cannot map both into the guest address space. More... | |

| void | access (PacketPtr pkt) |

| Perform an untimed memory access and update all the state (e.g. More... | |

| void | functionalAccess (PacketPtr pkt) |

| Perform an untimed memory read or write without changing anything but the memory itself. More... | |

Public Member Functions inherited from ClockedObject Public Member Functions inherited from ClockedObject | |

| ClockedObject (const ClockedObjectParams *p) | |

| const Params * | params () const |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from SimObject Public Member Functions inherited from SimObject | |

| virtual | ~SimObject () |

| virtual const std::string | name () const |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | regProbePoints () |

| Register probe points for this object. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. More... | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

| const Params * | params () const |

| SimObject (const Params *_params) | |

Public Member Functions inherited from EventManager Public Member Functions inherited from EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from Drainable Public Member Functions inherited from Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Public Member Functions inherited from Stats::Group Public Member Functions inherited from Stats::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. More... | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. More... | |

| virtual void | resetStats () |

| Callback to reset stats. More... | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. More... | |

| void | addStat (Stats::Info *info) |

| Register a stat with this group. More... | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. More... | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. More... | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. More... | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. More... | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

Public Member Functions inherited from Clocked Public Member Functions inherited from Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| Tick | recvAtomic (PacketPtr pkt) |

| void | recvFunctional (PacketPtr pkt) |

| bool | recvTimingReq (PacketPtr pkt) |

| void | recvRespRetry () |

Protected Member Functions inherited from AbstractMemory Protected Member Functions inherited from AbstractMemory | |

| bool | checkLockedAddrList (PacketPtr pkt) |

| void | trackLoadLocked (PacketPtr pkt) |

| bool | writeOK (PacketPtr pkt) |

Protected Member Functions inherited from Drainable Protected Member Functions inherited from Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. More... | |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from Clocked Protected Member Functions inherited from Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. More... | |

Private Member Functions | |

| unsigned int | nbrOutstanding () const |

| void | accessAndRespond (PacketPtr pkt) |

| When a packet is ready, use the "access()" method in AbstractMemory to actually create the response packet, and send it back to the outside world requestor. More... | |

| void | sendResponse () |

| void | tick () |

| Progress the controller one clock cycle. More... | |

Private Attributes | |

| MemoryPort | port |

| DRAMSim2Wrapper | wrapper |

| The actual DRAMSim2 wrapper. More... | |

| bool | retryReq |

| Is the connected port waiting for a retry from us. More... | |

| bool | retryResp |

| Are we waiting for a retry for sending a response. More... | |

| Tick | startTick |

| Keep track of when the wrapper is started. More... | |

| std::unordered_map< Addr, std::queue< PacketPtr > > | outstandingReads |

| Keep track of what packets are outstanding per address, and do so separately for reads and writes. More... | |

| std::unordered_map< Addr, std::queue< PacketPtr > > | outstandingWrites |

| unsigned int | nbrOutstandingReads |

| Count the number of outstanding transactions so that we can block any further requests until there is space in DRAMSim2 and the sending queue we need to buffer the response packets. More... | |

| unsigned int | nbrOutstandingWrites |

| std::deque< PacketPtr > | responseQueue |

| Queue to hold response packets until we can send them back. More... | |

| EventFunctionWrapper | sendResponseEvent |

| Event to schedule sending of responses. More... | |

| EventFunctionWrapper | tickEvent |

| Event to schedule clock ticks. More... | |

| std::unique_ptr< Packet > | pendingDelete |

| Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call. More... | |

Additional Inherited Members | |

Static Public Member Functions inherited from SimObject Static Public Member Functions inherited from SimObject | |

| static void | serializeAll (CheckpointOut &cp) |

| Serialize all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| static void | unserializeGlobals (CheckpointIn &cp) |

Public Attributes inherited from ClockedObject Public Attributes inherited from ClockedObject | |

| PowerState * | powerState |

Protected Attributes inherited from AbstractMemory Protected Attributes inherited from AbstractMemory | |

| AddrRange | range |

| uint8_t * | pmemAddr |

| MemBackdoor | backdoor |

| const bool | confTableReported |

| const bool | inAddrMap |

| const bool | kvmMap |

| std::list< LockedAddr > | lockedAddrList |

| System * | _system |

| Pointer to the System object. More... | |

| AbstractMemory::MemStats | stats |

Protected Attributes inherited from SimObject Protected Attributes inherited from SimObject | |

| const SimObjectParams * | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from EventManager Protected Attributes inherited from EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

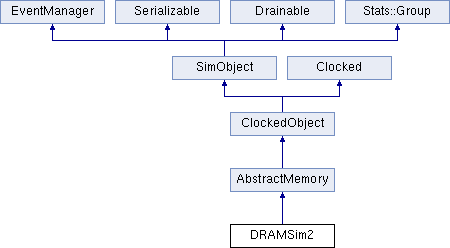

Detailed Description

Definition at line 53 of file dramsim2.hh.

Member Typedef Documentation

◆ Params

| typedef DRAMSim2Params DRAMSim2::Params |

Definition at line 169 of file dramsim2.hh.

Constructor & Destructor Documentation

◆ DRAMSim2()

| DRAMSim2::DRAMSim2 | ( | const Params * | p | ) |

Definition at line 47 of file dramsim2.cc.

References DRAMSim2Wrapper::clockPeriod(), DPRINTF, SimObject::name(), DRAMSim2Wrapper::printStats(), DRAMSim2Wrapper::queueSize(), readComplete(), registerExitCallback(), sendResponse(), DRAMSim2Wrapper::setCallbacks(), tick(), tickEvent, wrapper, and writeComplete().

Referenced by DRAMSim2::MemoryPort::recvRespRetry().

Member Function Documentation

◆ accessAndRespond()

|

private |

When a packet is ready, use the "access()" method in AbstractMemory to actually create the response packet, and send it back to the outside world requestor.

- Parameters

-

pkt The packet from the outside world

Definition at line 249 of file dramsim2.cc.

References AbstractMemory::access(), curTick(), DPRINTF, Packet::getAddr(), Packet::headerDelay, Packet::isResponse(), Packet::needsResponse(), Packet::payloadDelay, pendingDelete, responseQueue, retryResp, EventManager::schedule(), Event::scheduled(), and sendResponseEvent.

Referenced by readComplete(), and recvTimingReq().

◆ drain()

|

overridevirtual |

Notify an object that it needs to drain its state.

If the object does not need further simulation to drain internal buffers, it returns DrainState::Drained and automatically switches to the Drained state. If the object needs more simulation, it returns DrainState::Draining and automatically enters the Draining state. Other return values are invalid.

- Note

- An object that has entered the Drained state can be disturbed by other objects in the system and consequently stop being drained. These perturbations are not visible in the drain state. The simulator therefore repeats the draining process until all objects return DrainState::Drained on the first call to drain().

- Returns

- DrainState::Drained if the object is drained at this point in time, DrainState::Draining if it needs further simulation.

Implements Drainable.

Definition at line 348 of file dramsim2.cc.

References Drained, Draining, and nbrOutstanding().

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from SimObject.

Definition at line 338 of file dramsim2.cc.

References SimObject::getPort(), and port.

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from SimObject.

Definition at line 77 of file dramsim2.cc.

References DRAMSim2Wrapper::burstSize(), System::cacheLineSize(), fatal, SimObject::init(), Port::isConnected(), SimObject::name(), port, SlavePort::sendRangeChange(), AbstractMemory::system(), and wrapper.

◆ nbrOutstanding()

|

private |

Definition at line 132 of file dramsim2.cc.

References nbrOutstandingReads, nbrOutstandingWrites, and responseQueue.

Referenced by drain(), recvTimingReq(), sendResponse(), tick(), and writeComplete().

◆ readComplete()

| void DRAMSim2::readComplete | ( | unsigned | id, |

| uint64_t | addr, | ||

| uint64_t | cycle | ||

| ) |

Read completion callback.

- Parameters

-

id Channel id of the responder addr Address of the request cycle Internal cycle count of DRAMSim2

Definition at line 285 of file dramsim2.cc.

References accessAndRespond(), DRAMSim2Wrapper::clockPeriod(), curTick(), divCeil(), DPRINTF, nbrOutstandingReads, SimClock::Int::ns, outstandingReads, MipsISA::p, startTick, and wrapper.

Referenced by DRAMSim2().

◆ recvAtomic()

Definition at line 153 of file dramsim2.cc.

References AbstractMemory::access(), and Packet::cacheResponding().

◆ recvFunctional()

|

protected |

Definition at line 162 of file dramsim2.cc.

References AbstractMemory::functionalAccess(), ArmISA::i, SimObject::name(), Packet::popLabel(), Packet::pushLabel(), responseQueue, and Packet::trySatisfyFunctional().

◆ recvRespRetry()

|

protected |

Definition at line 239 of file dramsim2.cc.

References DPRINTF, retryResp, and sendResponse().

◆ recvTimingReq()

|

protected |

Definition at line 176 of file dramsim2.cc.

References accessAndRespond(), Packet::cacheResponding(), DRAMSim2Wrapper::canAccept(), DPRINTF, DRAMSim2Wrapper::enqueue(), Packet::getAddr(), Packet::isRead(), Packet::isWrite(), nbrOutstanding(), nbrOutstandingReads, nbrOutstandingWrites, outstandingReads, outstandingWrites, pendingDelete, DRAMSim2Wrapper::queueSize(), retryReq, and wrapper.

◆ sendResponse()

|

private |

Definition at line 102 of file dramsim2.cc.

References curTick(), DPRINTF, nbrOutstanding(), nbrOutstandingReads, nbrOutstandingWrites, port, responseQueue, retryResp, EventManager::schedule(), Event::scheduled(), sendResponseEvent, SlavePort::sendTimingResp(), and Drainable::signalDrainDone().

Referenced by DRAMSim2(), and recvRespRetry().

◆ startup()

|

overridevirtual |

startup() is the final initialization call before simulation.

All state is initialized (including unserialized state, if any, such as the curTick() value), so this is the appropriate place to schedule initial event(s) for objects that need them.

Reimplemented from SimObject.

Definition at line 93 of file dramsim2.cc.

References Clocked::clockEdge(), curTick(), EventManager::schedule(), startTick, and tickEvent.

◆ tick()

|

private |

Progress the controller one clock cycle.

Definition at line 138 of file dramsim2.cc.

References DRAMSim2Wrapper::clockPeriod(), curTick(), nbrOutstanding(), SimClock::Int::ns, port, DRAMSim2Wrapper::queueSize(), retryReq, EventManager::schedule(), SlavePort::sendRetryReq(), DRAMSim2Wrapper::tick(), tickEvent, and wrapper.

Referenced by DRAMSim2().

◆ writeComplete()

| void DRAMSim2::writeComplete | ( | unsigned | id, |

| uint64_t | addr, | ||

| uint64_t | cycle | ||

| ) |

Write completion callback.

- Parameters

-

id Channel id of the responder addr Address of the request cycle Internal cycle count of DRAMSim2

Definition at line 313 of file dramsim2.cc.

References DRAMSim2Wrapper::clockPeriod(), curTick(), divCeil(), DPRINTF, nbrOutstanding(), nbrOutstandingWrites, SimClock::Int::ns, outstandingWrites, MipsISA::p, Drainable::signalDrainDone(), startTick, and wrapper.

Referenced by DRAMSim2().

Member Data Documentation

◆ nbrOutstandingReads

|

private |

Count the number of outstanding transactions so that we can block any further requests until there is space in DRAMSim2 and the sending queue we need to buffer the response packets.

Definition at line 123 of file dramsim2.hh.

Referenced by nbrOutstanding(), readComplete(), recvTimingReq(), and sendResponse().

◆ nbrOutstandingWrites

|

private |

Definition at line 124 of file dramsim2.hh.

Referenced by nbrOutstanding(), recvTimingReq(), sendResponse(), and writeComplete().

◆ outstandingReads

Keep track of what packets are outstanding per address, and do so separately for reads and writes.

This is done so that we can return the right packet on completion from DRAMSim.

Definition at line 115 of file dramsim2.hh.

Referenced by readComplete(), and recvTimingReq().

◆ outstandingWrites

Definition at line 116 of file dramsim2.hh.

Referenced by recvTimingReq(), and writeComplete().

◆ pendingDelete

|

private |

Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call.

Definition at line 165 of file dramsim2.hh.

Referenced by accessAndRespond(), and recvTimingReq().

◆ port

|

private |

Definition at line 87 of file dramsim2.hh.

Referenced by getPort(), init(), sendResponse(), and tick().

◆ responseQueue

|

private |

Queue to hold response packets until we can send them back.

This is needed as DRAMSim2 unconditionally passes responses back without any flow control.

Definition at line 131 of file dramsim2.hh.

Referenced by accessAndRespond(), nbrOutstanding(), recvFunctional(), and sendResponse().

◆ retryReq

|

private |

Is the connected port waiting for a retry from us.

Definition at line 97 of file dramsim2.hh.

Referenced by recvTimingReq(), and tick().

◆ retryResp

|

private |

Are we waiting for a retry for sending a response.

Definition at line 102 of file dramsim2.hh.

Referenced by accessAndRespond(), recvRespRetry(), and sendResponse().

◆ sendResponseEvent

|

private |

Event to schedule sending of responses.

Definition at line 149 of file dramsim2.hh.

Referenced by accessAndRespond(), and sendResponse().

◆ startTick

|

private |

Keep track of when the wrapper is started.

Definition at line 107 of file dramsim2.hh.

Referenced by readComplete(), startup(), and writeComplete().

◆ tickEvent

|

private |

Event to schedule clock ticks.

Definition at line 159 of file dramsim2.hh.

Referenced by DRAMSim2(), startup(), and tick().

◆ wrapper

|

private |

The actual DRAMSim2 wrapper.

Definition at line 92 of file dramsim2.hh.

Referenced by DRAMSim2(), init(), readComplete(), recvTimingReq(), tick(), and writeComplete().

The documentation for this class was generated from the following files:

- mem/dramsim2.hh

- mem/dramsim2.cc