#include <deriv.hh>

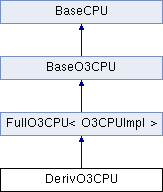

Inheritance diagram for DerivO3CPU:

Public Member Functions | |

| DerivO3CPU (DerivO3CPUParams *p) | |

Public Member Functions inherited from FullO3CPU< O3CPUImpl > Public Member Functions inherited from FullO3CPU< O3CPUImpl > | |

| FullO3CPU (DerivO3CPUParams *params) | |

| Constructs a CPU with the given parameters. More... | |

| ~FullO3CPU () | |

| Destructor. More... | |

| void | regStats () override |

| Registers statistics. More... | |

| void | regProbePoints () override |

| Register probe points. More... | |

| void | demapPage (Addr vaddr, uint64_t asn) |

| void | demapInstPage (Addr vaddr, uint64_t asn) |

| void | demapDataPage (Addr vaddr, uint64_t asn) |

| void | tick () |

| Ticks CPU, calling tick() on each stage, and checking the overall activity to see if the CPU should deschedule itself. More... | |

| void | init () override |

| Initialize the CPU. More... | |

| void | startup () override |

| int | numActiveThreads () |

| Returns the Number of Active Threads in the CPU. More... | |

| void | activateThread (ThreadID tid) |

| Add Thread to Active Threads List. More... | |

| void | deactivateThread (ThreadID tid) |

| Remove Thread from Active Threads List. More... | |

| void | insertThread (ThreadID tid) |

| Setup CPU to insert a thread's context. More... | |

| void | removeThread (ThreadID tid) |

| Remove all of a thread's context from CPU. More... | |

| Counter | totalInsts () const override |

| Count the Total Instructions Committed in the CPU. More... | |

| Counter | totalOps () const override |

| Count the Total Ops (including micro ops) committed in the CPU. More... | |

| void | activateContext (ThreadID tid) override |

| Add Thread to Active Threads List. More... | |

| void | suspendContext (ThreadID tid) override |

| Remove Thread from Active Threads List. More... | |

| void | haltContext (ThreadID tid) override |

| Remove Thread from Active Threads List && Remove Thread Context from CPU. More... | |

| void | updateThreadPriority () |

| Update The Order In Which We Process Threads. More... | |

| bool | isDraining () const |

| Is the CPU draining? More... | |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| Serialize a single thread. More... | |

| void | unserializeThread (CheckpointIn &cp, ThreadID tid) override |

| Unserialize one thread. More... | |

| void | addThreadToExitingList (ThreadID tid) |

| Insert tid to the list of threads trying to exit. More... | |

| bool | isThreadExiting (ThreadID tid) const |

| Is the thread trying to exit? More... | |

| void | scheduleThreadExitEvent (ThreadID tid) |

| If a thread is trying to exit and its corresponding trap event has been completed, schedule an event to terminate the thread. More... | |

| void | exitThreads () |

| Terminate all threads that are ready to exit. More... | |

| void | syscall (ThreadID tid) |

| Executes a syscall. More... | |

| DrainState | drain () override |

| Starts draining the CPU's pipeline of all instructions in order to stop all memory accesses. More... | |

| void | drainResume () override |

| Resumes execution after a drain. More... | |

| void | commitDrained (ThreadID tid) |

| Commit has reached a safe point to drain a thread. More... | |

| void | switchOut () override |

| Switches out this CPU. More... | |

| void | takeOverFrom (BaseCPU *oldCPU) override |

| Takes over from another CPU. More... | |

| void | verifyMemoryMode () const override |

| Verify that the system is in a memory mode supported by the CPU. More... | |

| InstSeqNum | getAndIncrementInstSeq () |

| Get the current instruction sequence number, and increment it. More... | |

| void | trap (const Fault &fault, ThreadID tid, const StaticInstPtr &inst) |

| Traps to handle given fault. More... | |

| void | setVectorsAsReady (ThreadID tid) |

| Mark vector fields in scoreboard as ready right after switching vector mode, since software may read vectors at this time. More... | |

| void | switchRenameMode (ThreadID tid, UnifiedFreeList *freelist) |

| Check if a change in renaming is needed for vector registers. More... | |

| Fault | getInterrupts () |

| Returns the Fault for any valid interrupt. More... | |

| void | processInterrupts (const Fault &interrupt) |

| Processes any an interrupt fault. More... | |

| void | halt () |

| Halts the CPU. More... | |

| RegVal | readMiscRegNoEffect (int misc_reg, ThreadID tid) const |

| Register accessors. More... | |

| RegVal | readMiscReg (int misc_reg, ThreadID tid) |

| Reads a misc. More... | |

| void | setMiscRegNoEffect (int misc_reg, RegVal val, ThreadID tid) |

| Sets a miscellaneous register. More... | |

| void | setMiscReg (int misc_reg, RegVal val, ThreadID tid) |

| Sets a misc. More... | |

| RegVal | readIntReg (PhysRegIdPtr phys_reg) |

| RegVal | readFloatReg (PhysRegIdPtr phys_reg) |

| const VecRegContainer & | readVecReg (PhysRegIdPtr reg_idx) const |

| VecRegContainer & | getWritableVecReg (PhysRegIdPtr reg_idx) |

| Read physical vector register for modification. More... | |

| Enums::VecRegRenameMode | vecRenameMode () const |

| Returns current vector renaming mode. More... | |

| void | vecRenameMode (Enums::VecRegRenameMode vec_mode) |

| Sets the current vector renaming mode. More... | |

| VecLaneT< VecElem, true > | readVecLane (PhysRegIdPtr phys_reg) const |

| Read physical vector register lane. More... | |

| VecLaneT< VecElem, true > | readVecLane (PhysRegIdPtr phys_reg) const |

| Read physical vector register lane. More... | |

| void | setVecLane (PhysRegIdPtr phys_reg, const LD &val) |

| Write a lane of the destination vector register. More... | |

| const VecElem & | readVecElem (PhysRegIdPtr reg_idx) const |

| const VecPredRegContainer & | readVecPredReg (PhysRegIdPtr reg_idx) const |

| VecPredRegContainer & | getWritableVecPredReg (PhysRegIdPtr reg_idx) |

| RegVal | readCCReg (PhysRegIdPtr phys_reg) |

| void | setIntReg (PhysRegIdPtr phys_reg, RegVal val) |

| void | setFloatReg (PhysRegIdPtr phys_reg, RegVal val) |

| void | setVecReg (PhysRegIdPtr reg_idx, const VecRegContainer &val) |

| void | setVecElem (PhysRegIdPtr reg_idx, const VecElem &val) |

| void | setVecPredReg (PhysRegIdPtr reg_idx, const VecPredRegContainer &val) |

| void | setCCReg (PhysRegIdPtr phys_reg, RegVal val) |

| RegVal | readArchIntReg (int reg_idx, ThreadID tid) |

| RegVal | readArchFloatReg (int reg_idx, ThreadID tid) |

| const VecRegContainer & | readArchVecReg (int reg_idx, ThreadID tid) const |

| VecRegContainer & | getWritableArchVecReg (int reg_idx, ThreadID tid) |

| Read architectural vector register for modification. More... | |

| VecLaneT< VecElem, true > | readArchVecLane (int reg_idx, int lId, ThreadID tid) const |

| Read architectural vector register lane. More... | |

| void | setArchVecLane (int reg_idx, int lId, ThreadID tid, const LD &val) |

| Write a lane of the destination vector register. More... | |

| const VecElem & | readArchVecElem (const RegIndex ®_idx, const ElemIndex &ldx, ThreadID tid) const |

| const VecPredRegContainer & | readArchVecPredReg (int reg_idx, ThreadID tid) const |

| VecPredRegContainer & | getWritableArchVecPredReg (int reg_idx, ThreadID tid) |

| RegVal | readArchCCReg (int reg_idx, ThreadID tid) |

| void | setArchIntReg (int reg_idx, RegVal val, ThreadID tid) |

| Architectural register accessors. More... | |

| void | setArchFloatReg (int reg_idx, RegVal val, ThreadID tid) |

| void | setArchVecPredReg (int reg_idx, const VecPredRegContainer &val, ThreadID tid) |

| void | setArchVecReg (int reg_idx, const VecRegContainer &val, ThreadID tid) |

| void | setArchVecElem (const RegIndex ®_idx, const ElemIndex &ldx, const VecElem &val, ThreadID tid) |

| void | setArchCCReg (int reg_idx, RegVal val, ThreadID tid) |

| void | pcState (const TheISA::PCState &newPCState, ThreadID tid) |

| Sets the commit PC state of a specific thread. More... | |

| TheISA::PCState | pcState (ThreadID tid) |

| Reads the commit PC state of a specific thread. More... | |

| Addr | instAddr (ThreadID tid) |

| Reads the commit PC of a specific thread. More... | |

| MicroPC | microPC (ThreadID tid) |

| Reads the commit micro PC of a specific thread. More... | |

| Addr | nextInstAddr (ThreadID tid) |

| Reads the next PC of a specific thread. More... | |

| void | squashFromTC (ThreadID tid) |

| Initiates a squash of all in-flight instructions for a given thread. More... | |

| ListIt | addInst (const DynInstPtr &inst) |

| Function to add instruction onto the head of the list of the instructions. More... | |

| void | instDone (ThreadID tid, const DynInstPtr &inst) |

| Function to tell the CPU that an instruction has completed. More... | |

| void | removeFrontInst (const DynInstPtr &inst) |

| Remove an instruction from the front end of the list. More... | |

| void | removeInstsNotInROB (ThreadID tid) |

| Remove all instructions that are not currently in the ROB. More... | |

| void | removeInstsUntil (const InstSeqNum &seq_num, ThreadID tid) |

| Remove all instructions younger than the given sequence number. More... | |

| void | squashInstIt (const ListIt &instIt, ThreadID tid) |

| Removes the instruction pointed to by the iterator. More... | |

| void | cleanUpRemovedInsts () |

| Cleans up all instructions on the remove list. More... | |

| void | dumpInsts () |

| Debug function to print all instructions on the list. More... | |

| void | activityThisCycle () |

| Records that there was time buffer activity this cycle. More... | |

| void | activateStage (const StageIdx idx) |

| Changes a stage's status to active within the activity recorder. More... | |

| void | deactivateStage (const StageIdx idx) |

| Changes a stage's status to inactive within the activity recorder. More... | |

| void | wakeCPU () |

| Wakes the CPU, rescheduling the CPU if it's not already active. More... | |

| virtual void | wakeup (ThreadID tid) override |

| ThreadID | getFreeTid () |

| Gets a free thread id. More... | |

| ThreadContext * | tcBase (ThreadID tid) |

| Returns a pointer to a thread context. More... | |

| Fault | pushRequest (const DynInstPtr &inst, bool isLoad, uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, AtomicOpFunctorPtr amo_op=nullptr, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| CPU pushRequest function, forwards request to LSQ. More... | |

| Fault | read (LSQRequest *req, int load_idx) |

| CPU read function, forwards read to LSQ. More... | |

| Fault | write (LSQRequest *req, uint8_t *data, int store_idx) |

| CPU write function, forwards write to LSQ. More... | |

| Port & | getInstPort () override |

| Used by the fetch unit to get a hold of the instruction port. More... | |

| Port & | getDataPort () override |

| Get the dcache port (used to find block size for translations). More... | |

| void | htmSendAbortSignal (ThreadID tid, uint64_t htm_uid, HtmFailureFaultCause cause) |

Public Member Functions inherited from BaseO3CPU Public Member Functions inherited from BaseO3CPU | |

| BaseO3CPU (BaseCPUParams *params) | |

| void | regStats () |

Public Member Functions inherited from BaseCPU Public Member Functions inherited from BaseCPU | |

| virtual PortProxy::SendFunctionalFunc | getSendFunctional () |

| Returns a sendFunctional delegate for use with port proxies. More... | |

| int | cpuId () const |

| Reads this CPU's ID. More... | |

| uint32_t | socketId () const |

| Reads this CPU's Socket ID. More... | |

| RequestorID | dataRequestorId () const |

| Reads this CPU's unique data requestor ID. More... | |

| RequestorID | instRequestorId () const |

| Reads this CPU's unique instruction requestor ID. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. More... | |

| uint32_t | taskId () const |

| Get cpu task id. More... | |

| void | taskId (uint32_t id) |

| Set cpu task id. More... | |

| uint32_t | getPid () const |

| void | setPid (uint32_t pid) |

| void | workItemBegin () |

| void | workItemEnd () |

| Tick | instCount () |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupts (ThreadID tid) |

| bool | checkInterrupts (ThreadID tid) const |

| Trace::InstTracer * | getTracer () |

| Provide access to the tracer pointer. More... | |

| int | findContext (ThreadContext *tc) |

| Given a Thread Context pointer return the thread num. More... | |

| virtual ThreadContext * | getContext (int tn) |

| Given a thread num get tho thread context for it. More... | |

| unsigned | numContexts () |

| Get the number of thread contexts available. More... | |

| ThreadID | contextToThread (ContextID cid) |

| Convert ContextID to threadID. More... | |

| const Params * | params () const |

| BaseCPU (Params *params, bool is_checker=false) | |

| virtual | ~BaseCPU () |

| void | init () override |

| void | startup () override |

| void | regStats () override |

| void | regProbePoints () override |

| void | registerThreadContexts () |

| void | deschedulePowerGatingEvent () |

| void | schedulePowerGatingEvent () |

| void | flushTLBs () |

| Flush all TLBs in the CPU. More... | |

| bool | switchedOut () const |

| Determine if the CPU is switched out. More... | |

| virtual void | verifyMemoryMode () const |

| Verify that the system is in a memory mode supported by the CPU. More... | |

| unsigned int | cacheLineSize () const |

| Get the cache line size of the system. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. More... | |

| virtual Counter | totalInsts () const =0 |

| virtual Counter | totalOps () const =0 |

| void | scheduleInstStop (ThreadID tid, Counter insts, const char *cause) |

| Schedule an event that exits the simulation loops after a predefined number of instructions. More... | |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| Get the number of instructions executed by the specified thread on this CPU. More... | |

| void | traceFunctions (Addr pc) |

| void | armMonitor (ThreadID tid, Addr address) |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseTLB *dtb) |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| bool | waitForRemoteGDB () const |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| Helper method to trigger PMU probes for a committed instruction. More... | |

Additional Inherited Members | |

Public Types inherited from FullO3CPU< O3CPUImpl > Public Types inherited from FullO3CPU< O3CPUImpl > | |

| enum | Status |

| enum | StageIdx |

| Enum to give each stage a specific index, so when calling activateStage() or deactivateStage(), they can specify which stage is being activated/deactivated. More... | |

| typedef O3CPUImpl ::CPUPol | CPUPolicy |

| typedef O3CPUImpl ::DynInstPtr | DynInstPtr |

| typedef O3CPUImpl ::O3CPU | O3CPU |

| using | VecElem = TheISA::VecElem |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

| typedef O3ThreadState< O3CPUImpl > | ImplState |

| typedef O3ThreadState< O3CPUImpl > | Thread |

| typedef std::list< DynInstPtr >::iterator | ListIt |

| using | LSQRequest = typename LSQ< O3CPUImpl >::LSQRequest |

| typedef CPUPolicy::TimeStruct | TimeStruct |

| Typedefs from the Impl to get the structs that each of the time buffers should use. More... | |

| typedef CPUPolicy::FetchStruct | FetchStruct |

| typedef CPUPolicy::DecodeStruct | DecodeStruct |

| typedef CPUPolicy::RenameStruct | RenameStruct |

| typedef CPUPolicy::IEWStruct | IEWStruct |

Public Types inherited from BaseCPU Public Types inherited from BaseCPU | |

| typedef BaseCPUParams | Params |

Static Public Member Functions inherited from BaseCPU Static Public Member Functions inherited from BaseCPU | |

| static int | numSimulatedInsts () |

| static int | numSimulatedOps () |

| static void | wakeup (ThreadID tid) |

| static int | numSimulatedCPUs () |

| static Counter | numSimulatedInsts () |

| static Counter | numSimulatedOps () |

Public Attributes inherited from FullO3CPU< O3CPUImpl > Public Attributes inherited from FullO3CPU< O3CPUImpl > | |

| BaseTLB * | itb |

| BaseTLB * | dtb |

| Status | _status |

| Overall CPU status. More... | |

| ProbePointArg< PacketPtr > * | ppInstAccessComplete |

| ProbePointArg< std::pair< DynInstPtr, PacketPtr > > * | ppDataAccessComplete |

| int | instcount |

| Count of total number of dynamic instructions in flight. More... | |

| std::list< DynInstPtr > | instList |

| List of all the instructions in flight. More... | |

| std::queue< ListIt > | removeList |

| List of all the instructions that will be removed at the end of this cycle. More... | |

| bool | removeInstsThisCycle |

| Records if instructions need to be removed this cycle due to being retired or squashed. More... | |

| TimeBuffer< TimeStruct > | timeBuffer |

| The main time buffer to do backwards communication. More... | |

| TimeBuffer< FetchStruct > | fetchQueue |

| The fetch stage's instruction queue. More... | |

| TimeBuffer< DecodeStruct > | decodeQueue |

| The decode stage's instruction queue. More... | |

| TimeBuffer< RenameStruct > | renameQueue |

| The rename stage's instruction queue. More... | |

| TimeBuffer< IEWStruct > | iewQueue |

| The IEW stage's instruction queue. More... | |

| InstSeqNum | globalSeqNum |

| The global sequence number counter. More... | |

| Checker< O3CPUImpl > * | checker |

| Pointer to the checker, which can dynamically verify instruction results at run time. More... | |

| System * | system |

| Pointer to the system. More... | |

| std::vector< Thread * > | thread |

| Pointers to all of the threads in the CPU. More... | |

| std::list< int > | cpuWaitList |

| Threads Scheduled to Enter CPU. More... | |

| Cycles | lastRunningCycle |

| The cycle that the CPU was last running, used for statistics. More... | |

| Tick | lastActivatedCycle |

| The cycle that the CPU was last activated by a new thread. More... | |

| std::map< ThreadID, unsigned > | threadMap |

| Mapping for system thread id to cpu id. More... | |

| std::vector< ThreadID > | tids |

| Available thread ids in the cpu. More... | |

| Stats::Scalar | timesIdled |

| Stat for total number of times the CPU is descheduled. More... | |

| Stats::Scalar | idleCycles |

| Stat for total number of cycles the CPU spends descheduled. More... | |

| Stats::Scalar | quiesceCycles |

| Stat for total number of cycles the CPU spends descheduled due to a quiesce operation or waiting for an interrupt. More... | |

| Stats::Vector | committedInsts |

| Stat for the number of committed instructions per thread. More... | |

| Stats::Vector | committedOps |

| Stat for the number of committed ops (including micro ops) per thread. More... | |

| Stats::Formula | cpi |

| Stat for the CPI per thread. More... | |

| Stats::Formula | totalCpi |

| Stat for the total CPI. More... | |

| Stats::Formula | ipc |

| Stat for the IPC per thread. More... | |

| Stats::Formula | totalIpc |

| Stat for the total IPC. More... | |

| Stats::Scalar | intRegfileReads |

| Stats::Scalar | intRegfileWrites |

| Stats::Scalar | fpRegfileReads |

| Stats::Scalar | fpRegfileWrites |

| Stats::Scalar | vecRegfileReads |

| Stats::Scalar | vecRegfileWrites |

| Stats::Scalar | vecPredRegfileReads |

| Stats::Scalar | vecPredRegfileWrites |

| Stats::Scalar | ccRegfileReads |

| Stats::Scalar | ccRegfileWrites |

| Stats::Scalar | miscRegfileReads |

| Stats::Scalar | miscRegfileWrites |

Public Attributes inherited from BaseCPU Public Attributes inherited from BaseCPU | |

| ThreadID | numThreads |

| Number of threads we're actually simulating (<= SMT_MAX_THREADS). More... | |

| System * | system |

| Stats::Scalar | numCycles |

| Stats::Scalar | numWorkItemsStarted |

| Stats::Scalar | numWorkItemsCompleted |

| Cycles | syscallRetryLatency |

Static Public Attributes inherited from BaseCPU Static Public Attributes inherited from BaseCPU | |

| static const uint32_t | invldPid = std::numeric_limits<uint32_t>::max() |

| Invalid or unknown Pid. More... | |

| static const Addr | PCMask = ~((Addr)sizeof(TheISA::MachInst) - 1) |

Protected Types inherited from BaseCPU Protected Types inherited from BaseCPU | |

| enum | CPUState { CPU_STATE_ON, CPU_STATE_SLEEP, CPU_STATE_WAKEUP } |

Protected Member Functions inherited from BaseCPU Protected Member Functions inherited from BaseCPU | |

| void | updateCycleCounters (CPUState state) |

| base method keeping track of cycle progression More... | |

| void | enterPwrGating () |

| ProbePoints::PMUUPtr | pmuProbePoint (const char *name) |

| Helper method to instantiate probe points belonging to this object. More... | |

Protected Attributes inherited from FullO3CPU< O3CPUImpl > Protected Attributes inherited from FullO3CPU< O3CPUImpl > | |

| CPUPolicy::Fetch | fetch |

| The fetch stage. More... | |

| CPUPolicy::Decode | decode |

| The decode stage. More... | |

| CPUPolicy::Rename | rename |

| The dispatch stage. More... | |

| CPUPolicy::IEW | iew |

| The issue/execute/writeback stages. More... | |

| CPUPolicy::Commit | commit |

| The commit stage. More... | |

| Enums::VecRegRenameMode | vecMode |

| The rename mode of the vector registers. More... | |

| PhysRegFile | regFile |

| The register file. More... | |

| CPUPolicy::FreeList | freeList |

| The free list. More... | |

| CPUPolicy::RenameMap | renameMap [O3CPUImpl ::MaxThreads] |

| The rename map. More... | |

| CPUPolicy::RenameMap | commitRenameMap [O3CPUImpl ::MaxThreads] |

| The commit rename map. More... | |

| CPUPolicy::ROB | rob |

| The re-order buffer. More... | |

| std::list< ThreadID > | activeThreads |

| Active Threads List. More... | |

| std::unordered_map< ThreadID, bool > | exitingThreads |

| This is a list of threads that are trying to exit. More... | |

| Scoreboard | scoreboard |

| Integer Register Scoreboard. More... | |

| std::vector< TheISA::ISA * > | isa |

Protected Attributes inherited from BaseCPU Protected Attributes inherited from BaseCPU | |

| Tick | instCnt |

| Instruction count used for SPARC misc register. More... | |

| int | _cpuId |

| const uint32_t | _socketId |

| Each cpu will have a socket ID that corresponds to its physical location in the system. More... | |

| RequestorID | _instRequestorId |

| instruction side request id that must be placed in all requests More... | |

| RequestorID | _dataRequestorId |

| data side request id that must be placed in all requests More... | |

| uint32_t | _taskId |

| An intrenal representation of a task identifier within gem5. More... | |

| uint32_t | _pid |

| The current OS process ID that is executing on this processor. More... | |

| bool | _switchedOut |

| Is the CPU switched out or active? More... | |

| const unsigned int | _cacheLineSize |

| Cache the cache line size that we get from the system. More... | |

| std::vector< BaseInterrupts * > | interrupts |

| std::vector< ThreadContext * > | threadContexts |

| Trace::InstTracer * | tracer |

| Cycles | previousCycle |

| CPUState | previousState |

| const Cycles | pwrGatingLatency |

| const bool | powerGatingOnIdle |

| EventFunctionWrapper | enterPwrGatingEvent |

| ProbePoints::PMUUPtr | ppRetiredInsts |

| Instruction commit probe point. More... | |

| ProbePoints::PMUUPtr | ppRetiredInstsPC |

| ProbePoints::PMUUPtr | ppRetiredLoads |

| Retired load instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredStores |

| Retired store instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredBranches |

| Retired branches (any type) More... | |

| ProbePoints::PMUUPtr | ppAllCycles |

| CPU cycle counter even if any thread Context is suspended. More... | |

| ProbePoints::PMUUPtr | ppActiveCycles |

| CPU cycle counter, only counts if any thread contexts is active. More... | |

| ProbePointArg< bool > * | ppSleeping |

| ProbePoint that signals transitions of threadContexts sets. More... | |

Detailed Description

Constructor & Destructor Documentation

◆ DerivO3CPU()

The documentation for this class was generated from the following file:

- cpu/o3/deriv.hh