|

| | Checker (Params *p) |

| |

| void | switchOut () |

| | Prepare for another CPU to take over execution. More...

|

| |

| void | takeOverFrom (BaseCPU *oldCPU) |

| | Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in. More...

|

| |

| void | advancePC (const Fault &fault) |

| |

| void | verify (const DynInstPtr &inst) |

| |

| void | validateInst (const DynInstPtr &inst) |

| |

| void | validateExecution (const DynInstPtr &inst) |

| |

| void | validateState () |

| |

| void | copyResult (const DynInstPtr &inst, const InstResult &mismatch_val, int start_idx) |

| |

| void | handlePendingInt () |

| |

| void | init () override |

| |

| | CheckerCPU (Params *p) |

| |

| virtual | ~CheckerCPU () |

| |

| void | setSystem (System *system) |

| |

| void | setIcachePort (RequestPort *icache_port) |

| |

| void | setDcachePort (RequestPort *dcache_port) |

| |

| Port & | getDataPort () override |

| | Purely virtual method that returns a reference to the data port. More...

|

| |

| Port & | getInstPort () override |

| | Purely virtual method that returns a reference to the instruction port. More...

|

| |

| BaseTLB * | getITBPtr () |

| |

| BaseTLB * | getDTBPtr () |

| |

| virtual Counter | totalInsts () const override |

| |

| virtual Counter | totalOps () const override |

| |

| void | serialize (CheckpointOut &cp) const override |

| |

| void | unserialize (CheckpointIn &cp) override |

| |

| RegVal | readIntRegOperand (const StaticInst *si, int idx) override |

| | Reads an integer register. More...

|

| |

| RegVal | readFloatRegOperandBits (const StaticInst *si, int idx) override |

| | Reads a floating point register in its binary format, instead of by value. More...

|

| |

| const VecRegContainer & | readVecRegOperand (const StaticInst *si, int idx) const override |

| | Read source vector register operand. More...

|

| |

| VecRegContainer & | getWritableVecRegOperand (const StaticInst *si, int idx) override |

| | Read destination vector register operand for modification. More...

|

| |

| VecElem | readVecElemOperand (const StaticInst *si, int idx) const override |

| | Vector Elem Interfaces. More...

|

| |

| const VecPredRegContainer & | readVecPredRegOperand (const StaticInst *si, int idx) const override |

| | Predicate registers interface. More...

|

| |

| VecPredRegContainer & | getWritableVecPredRegOperand (const StaticInst *si, int idx) override |

| | Gets destination predicate register operand for modification. More...

|

| |

| RegVal | readCCRegOperand (const StaticInst *si, int idx) override |

| |

| template<typename T > |

| void | setScalarResult (T &&t) |

| |

| template<typename T > |

| void | setVecResult (T &&t) |

| |

| template<typename T > |

| void | setVecElemResult (T &&t) |

| |

| template<typename T > |

| void | setVecPredResult (T &&t) |

| |

| void | setIntRegOperand (const StaticInst *si, int idx, RegVal val) override |

| | Sets an integer register to a value. More...

|

| |

| void | setFloatRegOperandBits (const StaticInst *si, int idx, RegVal val) override |

| | Sets the bits of a floating point register of single width to a binary value. More...

|

| |

| void | setCCRegOperand (const StaticInst *si, int idx, RegVal val) override |

| |

| void | setVecRegOperand (const StaticInst *si, int idx, const VecRegContainer &val) override |

| | Sets a destination vector register operand to a value. More...

|

| |

| void | setVecElemOperand (const StaticInst *si, int idx, const VecElem val) override |

| | Sets a vector register to a value. More...

|

| |

| void | setVecPredRegOperand (const StaticInst *si, int idx, const VecPredRegContainer &val) override |

| | Sets a destination predicate register operand to a value. More...

|

| |

| bool | readPredicate () const override |

| |

| void | setPredicate (bool val) override |

| |

| bool | readMemAccPredicate () const override |

| |

| void | setMemAccPredicate (bool val) override |

| |

| uint64_t | getHtmTransactionUid () const override |

| |

| uint64_t | newHtmTransactionUid () const override |

| |

| Fault | initiateHtmCmd (Request::Flags flags) override |

| | Initiate an HTM command, e.g. More...

|

| |

| bool | inHtmTransactionalState () const override |

| |

| uint64_t | getHtmTransactionalDepth () const override |

| |

| TheISA::PCState | pcState () const override |

| |

| void | pcState (const TheISA::PCState &val) override |

| |

| Addr | instAddr () |

| |

| Addr | nextInstAddr () |

| |

| MicroPC | microPC () |

| |

| RegVal | readMiscRegNoEffect (int misc_reg) const |

| |

| RegVal | readMiscReg (int misc_reg) override |

| | Reads a miscellaneous register, handling any architectural side effects due to reading that register. More...

|

| |

| void | setMiscRegNoEffect (int misc_reg, RegVal val) |

| |

| void | setMiscReg (int misc_reg, RegVal val) override |

| | Sets a miscellaneous register, handling any architectural side effects due to writing that register. More...

|

| |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| |

| void | recordPCChange (const TheISA::PCState &val) |

| |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| | Invalidate a page in the DTLB and ITLB. More...

|

| |

| void | armMonitor (Addr address) override |

| |

| bool | mwait (PacketPtr pkt) override |

| |

| void | mwaitAtomic (ThreadContext *tc) override |

| |

| AddressMonitor * | getAddrMonitor () override |

| |

| void | demapInstPage (Addr vaddr, uint64_t asn) |

| |

| void | demapDataPage (Addr vaddr, uint64_t asn) |

| |

| RequestPtr | genMemFragmentRequest (Addr frag_addr, int size, Request::Flags flags, const std::vector< bool > &byte_enable, int &frag_size, int &size_left) const |

| | Helper function used to generate the request for a single fragment of a memory access. More...

|

| |

| Fault | readMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| |

| Fault | amoMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| |

| unsigned int | readStCondFailures () const override |

| | Returns the number of consecutive store conditional failures. More...

|

| |

| void | setStCondFailures (unsigned int sc_failures) override |

| | Sets the number of consecutive store conditional failures. More...

|

| |

| void | wakeup (ThreadID tid) override |

| |

| void | syscall () override |

| | Executes a syscall. More...

|

| |

| void | handleError () |

| |

| bool | checkFlags (const RequestPtr &unverified_req, Addr vAddr, Addr pAddr, int flags) |

| | Checks if the flags set by the Checker and Checkee match. More...

|

| |

| void | dumpAndExit () |

| |

| ThreadContext * | tcBase () const override |

| | Returns a pointer to the ThreadContext. More...

|

| |

| SimpleThread * | threadBase () |

| |

| virtual ConstVecLane8 | readVec8BitLaneOperand (const StaticInst *si, int idx) const override |

| | Vector Register Lane Interfaces. More...

|

| |

| virtual ConstVecLane16 | readVec16BitLaneOperand (const StaticInst *si, int idx) const override |

| | Reads source vector 16bit operand. More...

|

| |

| virtual ConstVecLane32 | readVec32BitLaneOperand (const StaticInst *si, int idx) const override |

| | Reads source vector 32bit operand. More...

|

| |

| virtual ConstVecLane64 | readVec64BitLaneOperand (const StaticInst *si, int idx) const override |

| | Reads source vector 64bit operand. More...

|

| |

| template<typename LD > |

| void | setVecLaneOperandT (const StaticInst *si, int idx, const LD &val) |

| | Write a lane of the destination vector operand. More...

|

| |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::Byte > &val) override |

| | Write a lane of the destination vector operand. More...

|

| |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::TwoByte > &val) override |

| |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::FourByte > &val) override |

| |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::EightByte > &val) override |

| |

| virtual PortProxy::SendFunctionalFunc | getSendFunctional () |

| | Returns a sendFunctional delegate for use with port proxies. More...

|

| |

| int | cpuId () const |

| | Reads this CPU's ID. More...

|

| |

| uint32_t | socketId () const |

| | Reads this CPU's Socket ID. More...

|

| |

| RequestorID | dataRequestorId () const |

| | Reads this CPU's unique data requestor ID. More...

|

| |

| RequestorID | instRequestorId () const |

| | Reads this CPU's unique instruction requestor ID. More...

|

| |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| | Get a port on this CPU. More...

|

| |

| uint32_t | taskId () const |

| | Get cpu task id. More...

|

| |

| void | taskId (uint32_t id) |

| | Set cpu task id. More...

|

| |

| uint32_t | getPid () const |

| |

| void | setPid (uint32_t pid) |

| |

| void | workItemBegin () |

| |

| void | workItemEnd () |

| |

| Tick | instCount () |

| |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| |

| void | clearInterrupts (ThreadID tid) |

| |

| bool | checkInterrupts (ThreadID tid) const |

| |

| Trace::InstTracer * | getTracer () |

| | Provide access to the tracer pointer. More...

|

| |

| virtual void | activateContext (ThreadID thread_num) |

| | Notify the CPU that the indicated context is now active. More...

|

| |

| virtual void | suspendContext (ThreadID thread_num) |

| | Notify the CPU that the indicated context is now suspended. More...

|

| |

| virtual void | haltContext (ThreadID thread_num) |

| | Notify the CPU that the indicated context is now halted. More...

|

| |

| int | findContext (ThreadContext *tc) |

| | Given a Thread Context pointer return the thread num. More...

|

| |

| virtual ThreadContext * | getContext (int tn) |

| | Given a thread num get tho thread context for it. More...

|

| |

| unsigned | numContexts () |

| | Get the number of thread contexts available. More...

|

| |

| ThreadID | contextToThread (ContextID cid) |

| | Convert ContextID to threadID. More...

|

| |

| const Params * | params () const |

| |

| | BaseCPU (Params *params, bool is_checker=false) |

| |

| virtual | ~BaseCPU () |

| |

| void | init () override |

| |

| void | startup () override |

| |

| void | regStats () override |

| |

| void | regProbePoints () override |

| |

| void | registerThreadContexts () |

| |

| void | deschedulePowerGatingEvent () |

| |

| void | schedulePowerGatingEvent () |

| |

| void | flushTLBs () |

| | Flush all TLBs in the CPU. More...

|

| |

| bool | switchedOut () const |

| | Determine if the CPU is switched out. More...

|

| |

| virtual void | verifyMemoryMode () const |

| | Verify that the system is in a memory mode supported by the CPU. More...

|

| |

| unsigned int | cacheLineSize () const |

| | Get the cache line size of the system. More...

|

| |

| void | serialize (CheckpointOut &cp) const override |

| | Serialize this object to the given output stream. More...

|

| |

| void | unserialize (CheckpointIn &cp) override |

| | Reconstruct the state of this object from a checkpoint. More...

|

| |

| virtual void | serializeThread (CheckpointOut &cp, ThreadID tid) const |

| | Serialize a single thread. More...

|

| |

| virtual void | unserializeThread (CheckpointIn &cp, ThreadID tid) |

| | Unserialize one thread. More...

|

| |

| void | scheduleInstStop (ThreadID tid, Counter insts, const char *cause) |

| | Schedule an event that exits the simulation loops after a predefined number of instructions. More...

|

| |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| | Get the number of instructions executed by the specified thread on this CPU. More...

|

| |

| void | traceFunctions (Addr pc) |

| |

| void | armMonitor (ThreadID tid, Addr address) |

| |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseTLB *dtb) |

| |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| |

| bool | waitForRemoteGDB () const |

| |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| | Helper method to trigger PMU probes for a committed instruction. More...

|

| |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| | Perform an atomic memory read operation. More...

|

| |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| | Initiate a timing memory read operation. More...

|

| |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >())=0 |

| | For atomic-mode contexts, perform an atomic memory write operation. More...

|

| |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| | For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More...

|

| |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| | For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More...

|

| |

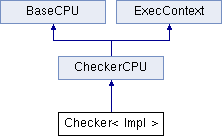

Public Member Functions inherited from CheckerCPU

Public Member Functions inherited from CheckerCPU Public Member Functions inherited from BaseCPU

Public Member Functions inherited from BaseCPU Public Member Functions inherited from ExecContext

Public Member Functions inherited from ExecContext Public Types inherited from CheckerCPU

Public Types inherited from CheckerCPU Public Types inherited from BaseCPU

Public Types inherited from BaseCPU Public Types inherited from ExecContext

Public Types inherited from ExecContext Static Public Member Functions inherited from BaseCPU

Static Public Member Functions inherited from BaseCPU Public Attributes inherited from CheckerCPU

Public Attributes inherited from CheckerCPU Public Attributes inherited from BaseCPU

Public Attributes inherited from BaseCPU Static Public Attributes inherited from BaseCPU

Static Public Attributes inherited from BaseCPU Protected Types inherited from CheckerCPU

Protected Types inherited from CheckerCPU Protected Types inherited from BaseCPU

Protected Types inherited from BaseCPU Protected Member Functions inherited from BaseCPU

Protected Member Functions inherited from BaseCPU Protected Attributes inherited from CheckerCPU

Protected Attributes inherited from CheckerCPU Protected Attributes inherited from BaseCPU

Protected Attributes inherited from BaseCPU