#include <amdgpu_vm.hh>

Public Member Functions | |

| UserTranslationGen (AMDGPUVM *_vm, VegaISA::Walker *_walker, int _vmid, Addr vaddr, Addr size) | |

Public Member Functions inherited from gem5::TranslationGen Public Member Functions inherited from gem5::TranslationGen | |

| TranslationGen (Addr new_start, Addr new_size) | |

| The starting virtual address and the size of the entire region being translated. | |

| virtual | ~TranslationGen () |

| Addr | start () const |

| Addr | size () const |

| const_iterator | begin () const |

| const_iterator | end () const |

Private Member Functions | |

| void | translate (Range &range) const override |

| Subclasses implement this function to complete TranslationGen. | |

Private Attributes | |

| AMDGPUVM * | vm |

| VegaISA::Walker * | walker |

| int | vmid |

Additional Inherited Members | |

Public Types inherited from gem5::TranslationGen Public Types inherited from gem5::TranslationGen | |

| using | const_iterator = TranslationGenConstIterator |

Protected Attributes inherited from gem5::TranslationGen Protected Attributes inherited from gem5::TranslationGen | |

| Addr | _start |

| Addr | _size |

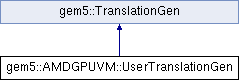

Detailed Description

Definition at line 352 of file amdgpu_vm.hh.

Constructor & Destructor Documentation

◆ UserTranslationGen()

|

inline |

Definition at line 362 of file amdgpu_vm.hh.

Member Function Documentation

◆ translate()

|

overrideprivatevirtual |

Subclasses implement this function to complete TranslationGen.

It should accept a Range reference which will have its "vaddr" field set to the virtual address to translate, and the "size" field set to the remaining size of the entire region being translated.

If there is a fault performing the translation of "vaddr", then this function should set the "fault" field of range and return.

If the translation was successful, this method should set "paddr" to the corresponding physical address, and set "size" to the number of bytes corresponding to the translation. Or more precisely, size should be set to the maximum "N" where vaddr + n maps to paddr + n for all 0 <= n <= N.

Implements gem5::TranslationGen.

Definition at line 383 of file amdgpu_vm.cc.

References AMDGPU_USER_PAGE_SIZE, gem5::X86ISA::base, DPRINTF, fatal, gem5::NoFault, gem5::TranslationGen::Range::paddr, gem5::BaseMMU::Read, gem5::roundUp(), gem5::TranslationGen::Range::size, gem5::TranslationGen::Range::vaddr, and gem5::ArmISA::vm.

Member Data Documentation

◆ vm

|

private |

Definition at line 355 of file amdgpu_vm.hh.

◆ vmid

|

private |

Definition at line 357 of file amdgpu_vm.hh.

◆ walker

|

private |

Definition at line 356 of file amdgpu_vm.hh.

The documentation for this class was generated from the following files:

- dev/amdgpu/amdgpu_vm.hh

- dev/amdgpu/amdgpu_vm.cc