gem5::ArmISA::HypervisorTrap Class Reference

#include <faults.hh>

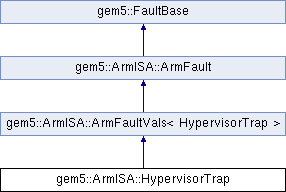

Inheritance diagram for gem5::ArmISA::HypervisorTrap:

Public Member Functions | |

| HypervisorTrap (ExtMachInst mach_inst, uint32_t _iss, ExceptionClass _overrideEc=ExceptionClass::INVALID) | |

| ExceptionClass | ec (ThreadContext *tc) const override |

| Syndrome methods. | |

| Public Member Functions inherited from gem5::ArmISA::ArmFaultVals< HypervisorTrap > | |

| ArmFaultVals (ExtMachInst mach_inst=0, uint32_t _iss=0) | |

| FaultName | name () const override |

| FaultOffset | offset (ThreadContext *tc) override |

| FaultOffset | offset64 (ThreadContext *tc) override |

| OperatingMode | nextMode () override |

| virtual bool | routeToMonitor (ThreadContext *tc) const override |

| uint8_t | armPcOffset (bool is_hyp) override |

| uint8_t | thumbPcOffset (bool is_hyp) override |

| uint8_t | armPcElrOffset () override |

| uint8_t | thumbPcElrOffset () override |

| bool | abortDisable (ThreadContext *tc) override |

| bool | fiqDisable (ThreadContext *tc) override |

| bool | il (ThreadContext *tc) const override |

| uint32_t | iss () const override |

| Public Member Functions inherited from gem5::ArmISA::ArmFault | |

| ArmFault (ExtMachInst mach_inst=0, uint32_t _iss=0) | |

| MiscRegIndex | getSyndromeReg64 () const |

| void | invoke (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) override |

| void | invoke32 (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

| void | invoke64 (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

| virtual void | update (ThreadContext *tc) |

| bool | isResetSPSR () |

| bool | vectorCatch (ThreadContext *tc, const StaticInstPtr &inst) |

| ArmStaticInst * | instrAnnotate (const StaticInstPtr &inst) |

| virtual void | annotate (AnnotationIDs id, uint64_t val) |

| virtual bool | routeToHyp (ThreadContext *tc) const |

| virtual uint32_t | vectorCatchFlag () const |

| virtual bool | isStage2 () const |

| virtual FSR | getFsr (ThreadContext *tc) const |

| virtual void | setSyndrome (ThreadContext *tc, MiscRegIndex syndrome_reg) |

| virtual bool | getFaultVAddr (Addr &va) const |

| OperatingMode | getToMode () const |

| virtual bool | isExternalAbort () const |

| Public Member Functions inherited from gem5::FaultBase | |

| virtual | ~FaultBase () |

Protected Attributes | |

| ExtMachInst | machInst |

| ExceptionClass | overrideEc |

| Protected Attributes inherited from gem5::ArmISA::ArmFault | |

| ExtMachInst | machInst |

| uint32_t | issRaw |

| bool | bStep |

| bool | from64 |

| bool | to64 |

| ExceptionLevel | fromEL |

| ExceptionLevel | toEL |

| OperatingMode | fromMode |

| OperatingMode | toMode |

| bool | faultUpdated |

| bool | hypRouted |

| bool | span |

Detailed Description

Constructor & Destructor Documentation

◆ HypervisorTrap()

|

inline |

Definition at line 450 of file faults.hh.

References gem5::ArmISA::ArmFaultVals< HypervisorTrap >::ArmFaultVals(), HypervisorTrap(), gem5::ArmISA::INVALID, and overrideEc.

Referenced by HypervisorTrap().

Member Function Documentation

◆ ec()

|

overridevirtual |

Syndrome methods.

Reimplemented from gem5::ArmISA::ArmFaultVals< HypervisorTrap >.

Definition at line 916 of file faults.cc.

References gem5::ArmISA::INVALID, overrideEc, and gem5::ArmISA::ArmFaultVals< HypervisorTrap >::vals().

Member Data Documentation

◆ machInst

|

protected |

◆ overrideEc

|

protected |

Definition at line 447 of file faults.hh.

Referenced by ec(), and HypervisorTrap().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:56 for gem5 by doxygen 1.14.0