#include <static_inst.hh>

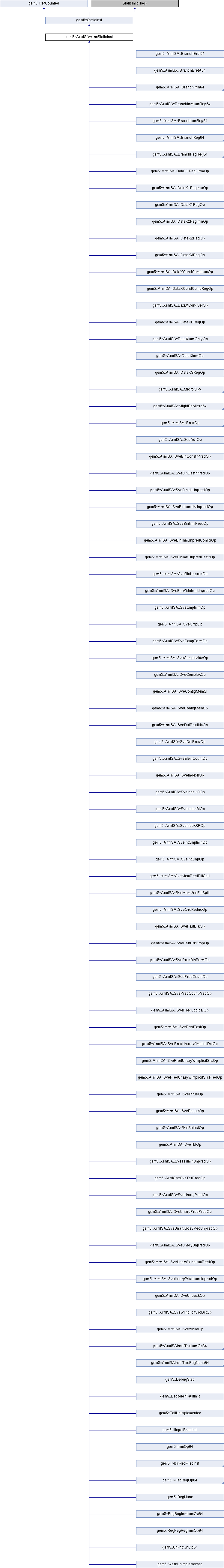

Public Member Functions | |

| virtual void | annotateFault (ArmFault *fault) |

| uint8_t | getIntWidth () const |

| ssize_t | instSize () const |

| Returns the byte size of current instruction. | |

| MachInst | encoding () const |

| Returns the real encoding of the instruction: the machInst field is in fact always 64 bit wide and contains some instruction metadata, which means it differs from the real opcode. | |

| size_t | asBytes (void *buf, size_t max_size) override |

| Instruction classes can override this function to return a a representation of themselves as a blob of bytes, generally assumed to be that instructions ExtMachInst. | |

| Fault | undefined (bool disabled=false) const |

| Fault | generateTrap (ArmISA::ExceptionLevel el, ArmISA::ExceptionClass ec, uint32_t iss) const |

| Public Member Functions inherited from gem5::StaticInst | |

| uint8_t | numSrcRegs () const |

| Number of source registers. | |

| uint8_t | numDestRegs () const |

| Number of destination registers. | |

| uint8_t | numDestRegs (RegClassType type) const |

| Number of destination registers of a particular type. | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isMatrix () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isFullMemBarrier () const |

| bool | isReadBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isUnverifiable () const |

| bool | isPseudo () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isInvalid () const |

| bool | isHtmCmd () const |

| void | setFirstMicroop () |

| void | setLastMicroop () |

| void | setDelayedCommit () |

| void | setFlag (Flags f) |

| OpClass | opClass () const |

| Operation class. Used to select appropriate function unit in issue. | |

| const RegId & | destRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th destination reg. | |

| void | setDestRegIdx (int i, const RegId &val) |

| const RegId & | srcRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th source reg. | |

| void | setSrcRegIdx (int i, const RegId &val) |

| virtual | ~StaticInst () |

| virtual Fault | execute (ExecContext *xc, trace::InstRecord *traceData) const =0 |

| virtual Fault | initiateAcc (ExecContext *xc, trace::InstRecord *traceData) const |

| virtual Fault | completeAcc (Packet *pkt, ExecContext *xc, trace::InstRecord *trace_data) const |

| size_t | size () const |

| virtual void | size (size_t newSize) |

| virtual StaticInstPtr | fetchMicroop (MicroPC upc) const |

| Return the microop that goes with a particular micropc. | |

| virtual std::unique_ptr< PCStateBase > | branchTarget (const PCStateBase &pc) const |

| Return the target address for a PC-relative branch. | |

| virtual std::unique_ptr< PCStateBase > | branchTarget (ThreadContext *tc) const |

| Return the target address for an indirect branch (jump). | |

| virtual const std::string & | disassemble (Addr pc, const loader::SymbolTable *symtab=nullptr) const |

| Return string representation of disassembled instruction. | |

| void | printFlags (std::ostream &outs, const std::string &separator) const |

| Print a separator separated list of this instruction's set flag names on the given stream. | |

| std::string | getName () |

| Return name of machine instruction. | |

| Public Member Functions inherited from gem5::RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. | |

| void | incref () const |

| Increment the reference count. | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. | |

Static Public Member Functions | |

| static unsigned | getCurSveVecLenInBits (ThreadContext *tc) |

| static unsigned | getCurSveVecLenInQWords (ThreadContext *tc) |

| template<typename T> | |

| static unsigned | getCurSveVecLen (ThreadContext *tc) |

| static unsigned | getCurSmeVecLenInBits (ThreadContext *tc) |

| static unsigned | getCurSmeVecLenInQWords (ThreadContext *tc) |

| template<typename T> | |

| static unsigned | getCurSmeVecLen (ThreadContext *tc) |

Protected Member Functions | |

| int32_t | shift_rm_imm (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| int32_t | shift_rm_rs (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| bool | shift_carry_imm (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| bool | shift_carry_rs (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| int64_t | shiftReg64 (uint64_t base, uint64_t shiftAmt, ArmShiftType type, uint8_t width) const |

| int64_t | extendReg64 (uint64_t base, ArmExtendType type, uint64_t shiftAmt, uint8_t width) const |

| ArmStaticInst (const char *mnem, ExtMachInst _machInst, OpClass __opClass) | |

| void | printIntReg (std::ostream &os, RegIndex reg_idx, uint8_t opWidth=0) const |

| Print a register name for disassembly given the unique dependence tag number (FP or int). | |

| void | printFloatReg (std::ostream &os, RegIndex reg_idx) const |

| void | printVecReg (std::ostream &os, RegIndex reg_idx, bool isSveVecReg=false) const |

| void | printVecPredReg (std::ostream &os, RegIndex reg_idx) const |

| void | printCCReg (std::ostream &os, RegIndex reg_idx) const |

| void | printMiscReg (std::ostream &os, RegIndex reg_idx) const |

| void | printMnemonic (std::ostream &os, const std::string &suffix="", bool withPred=true, bool withCond64=false, ConditionCode cond64=COND_UC) const |

| void | printTarget (std::ostream &os, Addr target, const loader::SymbolTable *symtab) const |

| void | printCondition (std::ostream &os, unsigned code, bool noImplicit=false) const |

| void | printMemSymbol (std::ostream &os, const loader::SymbolTable *symtab, const std::string &prefix, const Addr addr, const std::string &suffix) const |

| void | printShiftOperand (std::ostream &os, RegIndex rm, bool immShift, uint32_t shiftAmt, RegIndex rs, ArmShiftType type) const |

| void | printExtendOperand (bool firstOperand, std::ostream &os, RegIndex rm, ArmExtendType type, int64_t shiftAmt) const |

| void | printPFflags (std::ostream &os, int flag) const |

| void | printDataInst (std::ostream &os, bool withImm) const |

| void | printDataInst (std::ostream &os, bool withImm, bool immShift, bool s, RegIndex rd, RegIndex rn, RegIndex rm, RegIndex rs, uint32_t shiftAmt, ArmShiftType type, uint64_t imm) const |

| void | advancePC (PCStateBase &pcState) const override |

| void | advancePC (ThreadContext *tc) const override |

| uint64_t | getEMI () const override |

| std::unique_ptr< PCStateBase > | buildRetPC (const PCStateBase &cur_pc, const PCStateBase &call_pc) const override |

| std::string | generateDisassembly (Addr pc, const loader::SymbolTable *symtab) const override |

| Internal function to generate disassembly string. | |

| Fault | disabledFault () const |

| bool | isWFxTrapping (ThreadContext *tc, ExceptionLevel targetEL, bool isWfe) const |

| Fault | softwareBreakpoint32 (ExecContext *xc, uint16_t imm) const |

| Trigger a Software Breakpoint. | |

| Fault | advSIMDFPAccessTrap64 (ExceptionLevel el) const |

| Trap an access to Advanced SIMD or FP registers due to access control bits. | |

| Fault | checkFPAdvSIMDTrap64 (ThreadContext *tc, CPSR cpsr) const |

| Check an Advaned SIMD access against CPTR_EL2 and CPTR_EL3. | |

| Fault | checkFPAdvSIMDEnabled64 (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check an Advaned SIMD access against CPACR_EL1, CPTR_EL2, and CPTR_EL3. | |

| Fault | checkAdvSIMDOrFPEnabled32 (ThreadContext *tc, CPSR cpsr, CPACR cpacr, NSACR nsacr, FPEXC fpexc, bool fpexc_check, bool advsimd) const |

| Check if a VFP/SIMD access from aarch32 should be allowed. | |

| Fault | checkForWFxTrap32 (ThreadContext *tc, ExceptionLevel tgtEl, bool isWfe) const |

| Check if WFE/WFI instruction execution in aarch32 should be trapped. | |

| Fault | checkForWFxTrap64 (ThreadContext *tc, ExceptionLevel tgtEl, bool isWfe) const |

| Check if WFE/WFI instruction execution in aarch64 should be trapped. | |

| Fault | trapWFx (ThreadContext *tc, CPSR cpsr, SCR scr, bool isWfe) const |

| WFE/WFI trapping helper function. | |

| Fault | checkSETENDEnabled (ThreadContext *tc, CPSR cpsr) const |

| Check if SETEND instruction execution in aarch32 should be trapped. | |

| Fault | undefinedFault32 (ThreadContext *tc, ExceptionLevel el) const |

| UNDEFINED behaviour in AArch32. | |

| Fault | undefinedFault64 (ThreadContext *tc, ExceptionLevel el) const |

| UNDEFINED behaviour in AArch64. | |

| Fault | sveAccessTrap (ExceptionLevel el) const |

| Trap an access to SVE registers due to access control bits. | |

| Fault | checkSveEnabled (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check an SVE access against CPACR_EL1, CPTR_EL2, and CPTR_EL3. | |

| Fault | smeAccessTrap (ExceptionLevel el, uint32_t iss=0) const |

| Trap an access to SME registers due to access control bits. | |

| Fault | checkSmeEnabled (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check if SME is enabled by checking the SME and FP bits of CPACR_EL1, CPTR_EL2, and CPTR_EL3. | |

| Fault | checkSmeAccess (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check an SME access against CPACR_EL1, CPTR_EL2, and CPTR_EL3. | |

| Fault | checkSveSmeEnabled (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check an SVE access against CPACR_EL1, CPTR_EL2, and CPTR_EL3, but choosing the correct set of traps to check based on Streaming Mode. | |

| CPSR | getPSTATEFromPSR (ThreadContext *tc, CPSR cpsr, CPSR spsr) const |

| Get the new PSTATE from a SPSR register in preparation for an exception return. | |

| bool | generalExceptionsToAArch64 (ThreadContext *tc, ExceptionLevel pstateEL) const |

| Return true if exceptions normally routed to EL1 are being handled at an Exception level using AArch64, because either EL1 is using AArch64 or TGE is in force and EL2 is using AArch64. | |

| void | setRegIdxArrays (RegIdArrayPtr src, RegIdArrayPtr dest) |

| Set the pointers which point to the arrays of source and destination register indices. | |

| StaticInst (const char *_mnemonic, OpClass op_class) | |

| Constructor. | |

| template<typename T> | |

| size_t | simpleAsBytes (void *buf, size_t max_size, const T &t) |

Static Protected Member Functions | |

| template<int width> | |

| static bool | saturateOp (int32_t &res, int64_t op1, int64_t op2, bool sub=false) |

| static bool | satInt (int32_t &res, int64_t op, int width) |

| template<int width> | |

| static bool | uSaturateOp (uint32_t &res, int64_t op1, int64_t op2, bool sub=false) |

| static bool | uSatInt (int32_t &res, int64_t op, int width) |

| static void | activateBreakpoint (ThreadContext *tc) |

| static uint32_t | cpsrWriteByInstr (CPSR cpsr, uint32_t val, SCR scr, NSACR nsacr, uint8_t byteMask, bool affectState, bool nmfi, ThreadContext *tc) |

| static uint32_t | spsrWriteByInstr (uint32_t spsr, uint32_t val, uint8_t byteMask, bool affectState) |

| static Addr | readPC (ExecContext *xc) |

| static void | setNextPC (ExecContext *xc, Addr val) |

| template<class T> | |

| static T | cSwap (T val, bool big) |

| template<class T, class E> | |

| static T | cSwap (T val, bool big) |

| static void | setIWNextPC (ExecContext *xc, Addr val) |

| static void | setAIWNextPC (ExecContext *xc, Addr val) |

Protected Attributes | |

| bool | aarch64 |

| uint8_t | intWidth |

| ExtMachInst | machInst |

| Protected Attributes inherited from gem5::StaticInst | |

| std::bitset< Num_Flags > | flags |

| Flag values for this instruction. | |

| OpClass | _opClass |

| See opClass(). | |

| uint8_t | _numSrcRegs = 0 |

| See numSrcRegs(). | |

| uint8_t | _numDestRegs = 0 |

| See numDestRegs(). | |

| std::array< uint8_t, MiscRegClass+1 > | _numTypedDestRegs = {} |

| size_t | _size = 0 |

| Instruction size in bytes. | |

| const char * | mnemonic |

| Base mnemonic (e.g., "add"). | |

| std::unique_ptr< std::string > | cachedDisassembly |

| String representation of disassembly (lazily evaluated via disassemble()). | |

Additional Inherited Members | |

| Public Types inherited from gem5::StaticInst | |

| using | RegIdArrayPtr = RegId (StaticInst:: *)[] |

| static StaticInstPtr | nullStaticInstPtr |

| Pointer to a statically allocated "null" instruction object. | |

Detailed Description

Definition at line 65 of file static_inst.hh.

Constructor & Destructor Documentation

◆ ArmStaticInst()

|

inlineprotected |

Definition at line 154 of file static_inst.hh.

References aarch64, gem5::bits(), intWidth, machInst, and gem5::StaticInst::StaticInst().

Referenced by gem5::ArmISA::BranchEret64::BranchEret64(), gem5::ArmISA::BranchEretA64::BranchEretA64(), gem5::ArmISA::BranchImm64::BranchImm64(), gem5::ArmISA::BranchImmImmReg64::BranchImmImmReg64(), gem5::ArmISA::BranchImmReg64::BranchImmReg64(), gem5::ArmISA::BranchReg64::BranchReg64(), gem5::ArmISA::BranchRegReg64::BranchRegReg64(), gem5::ArmISA::DataX1Reg2ImmOp::DataX1Reg2ImmOp(), gem5::ArmISA::DataX1RegImmOp::DataX1RegImmOp(), gem5::ArmISA::DataX1RegOp::DataX1RegOp(), gem5::ArmISA::DataX2RegImmOp::DataX2RegImmOp(), gem5::ArmISA::DataX2RegOp::DataX2RegOp(), gem5::ArmISA::DataX3RegOp::DataX3RegOp(), gem5::ArmISA::DataXCondCompImmOp::DataXCondCompImmOp(), gem5::ArmISA::DataXCondCompRegOp::DataXCondCompRegOp(), gem5::ArmISA::DataXCondSelOp::DataXCondSelOp(), gem5::ArmISA::DataXERegOp::DataXERegOp(), gem5::ArmISA::DataXImmOnlyOp::DataXImmOnlyOp(), gem5::ArmISA::DataXImmOp::DataXImmOp(), gem5::ArmISA::DataXSRegOp::DataXSRegOp(), gem5::DebugStep::DebugStep(), gem5::DecoderFaultInst::DecoderFaultInst(), gem5::IllegalExecInst::IllegalExecInst(), gem5::ImmOp64::ImmOp64(), gem5::McrMrcMiscInst::McrMrcMiscInst(), gem5::ArmISA::MicroOpX::MicroOpX(), gem5::ArmISA::MightBeMicro64::MightBeMicro64(), gem5::MiscRegOp64::MiscRegOp64(), gem5::ArmISA::PredOp::PredOp(), gem5::RegImmImmOp64::RegImmImmOp64(), gem5::RegNone::RegNone(), gem5::RegOp64::RegOp64(), gem5::RegRegImmImmOp64::RegRegImmImmOp64(), gem5::RegRegRegImmOp64::RegRegRegImmOp64(), gem5::ArmISA::SmeAddOp::SmeAddOp(), gem5::ArmISA::SmeAddVlOp::SmeAddVlOp(), gem5::ArmISA::SmeLd1xSt1xOp::SmeLd1xSt1xOp(), gem5::ArmISA::SmeLdrStrOp::SmeLdrStrOp(), gem5::ArmISA::SmeMovExtractOp::SmeMovExtractOp(), gem5::ArmISA::SmeMovInsertOp::SmeMovInsertOp(), gem5::ArmISA::SmeOPOp::SmeOPOp(), gem5::ArmISA::SmeRdsvlOp::SmeRdsvlOp(), gem5::ArmISA::SmeZeroOp::SmeZeroOp(), gem5::ArmISA::SveAdrOp::SveAdrOp(), gem5::ArmISA::SveBinConstrPredOp::SveBinConstrPredOp(), gem5::ArmISA::SveBinDestrPredOp::SveBinDestrPredOp(), gem5::ArmISA::SveBinIdxUnpredOp::SveBinIdxUnpredOp(), gem5::ArmISA::SveBinImmIdxUnpredOp::SveBinImmIdxUnpredOp(), gem5::ArmISA::SveBinImmPredOp::SveBinImmPredOp(), gem5::ArmISA::SveBinImmUnpredConstrOp::SveBinImmUnpredConstrOp(), gem5::ArmISA::SveBinImmUnpredDestrOp::SveBinImmUnpredDestrOp(), gem5::ArmISA::SveBinUnpredOp::SveBinUnpredOp(), gem5::ArmISA::SveBinWideImmUnpredOp::SveBinWideImmUnpredOp(), gem5::ArmISA::SveClampOp::SveClampOp(), gem5::ArmISA::SveCmpImmOp::SveCmpImmOp(), gem5::ArmISA::SveCmpOp::SveCmpOp(), gem5::ArmISA::SveComplexIdxOp::SveComplexIdxOp(), gem5::ArmISA::SveComplexOp::SveComplexOp(), gem5::ArmISA::SveCompTermOp::SveCompTermOp(), gem5::ArmISA::SveContigMemSI::SveContigMemSI(), gem5::ArmISA::SveContigMemSS::SveContigMemSS(), gem5::ArmISA::SveDotProdIdxOp::SveDotProdIdxOp(), gem5::ArmISA::SveDotProdOp::SveDotProdOp(), gem5::ArmISA::SveElemCountOp::SveElemCountOp(), gem5::ArmISA::SveIndexIIOp::SveIndexIIOp(), gem5::ArmISA::SveIndexIROp::SveIndexIROp(), gem5::ArmISA::SveIndexRIOp::SveIndexRIOp(), gem5::ArmISA::SveIndexRROp::SveIndexRROp(), gem5::ArmISA::SveIntCmpImmOp::SveIntCmpImmOp(), gem5::ArmISA::SveIntCmpOp::SveIntCmpOp(), gem5::ArmISA::SveMemPredFillSpill::SveMemPredFillSpill(), gem5::ArmISA::SveMemVecFillSpill::SveMemVecFillSpill(), gem5::ArmISA::SveOrdReducOp::SveOrdReducOp(), gem5::ArmISA::SvePartBrkOp::SvePartBrkOp(), gem5::ArmISA::SvePartBrkPropOp::SvePartBrkPropOp(), gem5::ArmISA::SvePredBinPermOp::SvePredBinPermOp(), gem5::ArmISA::SvePredCountOp::SvePredCountOp(), gem5::ArmISA::SvePredCountPredOp::SvePredCountPredOp(), gem5::ArmISA::SvePredLogicalOp::SvePredLogicalOp(), gem5::ArmISA::SvePredTestOp::SvePredTestOp(), gem5::ArmISA::SvePredUnaryWImplicitDstOp::SvePredUnaryWImplicitDstOp(), gem5::ArmISA::SvePredUnaryWImplicitSrcOp::SvePredUnaryWImplicitSrcOp(), gem5::ArmISA::SvePredUnaryWImplicitSrcPredOp::SvePredUnaryWImplicitSrcPredOp(), gem5::ArmISA::SvePselOp::SvePselOp(), gem5::ArmISA::SvePtrueOp::SvePtrueOp(), gem5::ArmISA::SveReducOp::SveReducOp(), gem5::ArmISA::SveSelectOp::SveSelectOp(), gem5::ArmISA::SveTblOp::SveTblOp(), gem5::ArmISA::SveTerImmUnpredOp::SveTerImmUnpredOp(), gem5::ArmISA::SveTerPredOp::SveTerPredOp(), gem5::ArmISA::SveTerUnpredOp::SveTerUnpredOp(), gem5::ArmISA::SveUnaryPredOp::SveUnaryPredOp(), gem5::ArmISA::SveUnaryPredPredOp::SveUnaryPredPredOp(), gem5::ArmISA::SveUnarySca2VecUnpredOp::SveUnarySca2VecUnpredOp(), gem5::ArmISA::SveUnaryUnpredOp::SveUnaryUnpredOp(), gem5::ArmISA::SveUnaryWideImmPredOp::SveUnaryWideImmPredOp(), gem5::ArmISA::SveUnaryWideImmUnpredOp::SveUnaryWideImmUnpredOp(), gem5::ArmISA::SveUnpackOp::SveUnpackOp(), gem5::ArmISA::SveWhileOp::SveWhileOp(), gem5::ArmISA::SveWImplicitSrcDstOp::SveWImplicitSrcDstOp(), gem5::ArmISAInst::TmeImmOp64::TmeImmOp64(), gem5::ArmISAInst::TmeRegNone64::TmeRegNone64(), and gem5::UnknownOp64::UnknownOp64().

Member Function Documentation

◆ activateBreakpoint()

|

inlinestaticprotected |

Definition at line 230 of file static_inst.hh.

References gem5::ArmISA::ISA::getSelfDebug(), and gem5::ArmISA::sd.

Referenced by cpsrWriteByInstr().

◆ advancePC() [1/2]

|

inlineoverrideprotectedvirtual |

Implements gem5::StaticInst.

Reimplemented in gem5::ArmISA::FpOp, gem5::ArmISA::MicroOp, gem5::ArmISA::MicroOpX, gem5::ArmISA::MightBeMicro64, gem5::ArmISA::MightBeMicro, and gem5::ArmISA::PredMicroop.

Definition at line 202 of file static_inst.hh.

References gem5::PCStateBase::as().

◆ advancePC() [2/2]

|

inlineoverrideprotectedvirtual |

Reimplemented from gem5::StaticInst.

Reimplemented in gem5::ArmISA::FpOp, gem5::ArmISA::MicroOp, gem5::ArmISA::MicroOpX, gem5::ArmISA::MightBeMicro64, gem5::ArmISA::MightBeMicro, and gem5::ArmISA::PredMicroop.

Definition at line 208 of file static_inst.hh.

References gem5::PCStateBase::as(), gem5::MipsISA::pc, and gem5::ThreadContext::pcState().

◆ advSIMDFPAccessTrap64()

|

protected |

Trap an access to Advanced SIMD or FP registers due to access control bits.

See aarch64/exceptions/traps/AArch64.AdvSIMDFPAccessTrap in the ARM ARM psueodcode library.

- Parameters

-

el Target EL for the trap

Definition at line 655 of file static_inst.cc.

References gem5::ArmISA::el, generateTrap(), and gem5::ArmISA::TRAPPED_SIMD_FP.

Referenced by checkAdvSIMDOrFPEnabled32(), checkFPAdvSIMDEnabled64(), checkFPAdvSIMDTrap64(), checkSmeEnabled(), and checkSveEnabled().

◆ annotateFault()

|

inlinevirtual |

Definition at line 567 of file static_inst.hh.

Referenced by gem5::ArmISA::ArmFault::instrAnnotate().

◆ asBytes()

|

inlineoverridevirtual |

Instruction classes can override this function to return a a representation of themselves as a blob of bytes, generally assumed to be that instructions ExtMachInst.

buf is a buffer to hold the bytes. max_size is the size allocated for that buffer by the caller. The return value is how much data was actually put into the buffer, zero if no data was put in the buffer, or the necessary size of the buffer if there wasn't enough space.

Reimplemented from gem5::StaticInst.

Definition at line 595 of file static_inst.hh.

References machInst, and gem5::StaticInst::simpleAsBytes().

◆ buildRetPC()

|

inlineoverrideprotectedvirtual |

Reimplemented from gem5::StaticInst.

Definition at line 218 of file static_inst.hh.

References gem5::PCStateBase::as(), and gem5::PCStateBase::clone().

◆ checkAdvSIMDOrFPEnabled32()

|

protected |

Check if a VFP/SIMD access from aarch32 should be allowed.

See aarch32/exceptions/traps/AArch32.CheckAdvSIMDOrFPEnabled in the ARM ARM psueodcode library.

Definition at line 713 of file static_inst.cc.

References gem5::ArmISA::advsimd, advSIMDFPAccessTrap64(), checkFPAdvSIMDEnabled64(), checkFPAdvSIMDTrap64(), gem5::ArmISA::currEL(), disabledFault(), gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL3, gem5::ArmISA::ELIs64(), gem5::ArmSystem::haveEL(), gem5::ArmISA::iss, gem5::ArmISA::isSecure(), machInst, gem5::ArmISA::MISCREG_CPTR_EL3, gem5::ArmISA::MISCREG_HCPTR, gem5::StaticInst::mnemonic, gem5::NoFault, gem5::ThreadContext::readMiscReg(), and gem5::ArmISA::TRAPPED_HCPTR.

◆ checkForWFxTrap32()

|

protected |

Check if WFE/WFI instruction execution in aarch32 should be trapped.

See aarch32/exceptions/traps/AArch32.checkForWFxTrap in the ARM ARM psueodcode library.

Definition at line 817 of file static_inst.cc.

References checkForWFxTrap64(), gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL3, gem5::ArmISA::ELIs64(), gem5::ArmSystem::haveEL(), gem5::ArmISA::iss, isWFxTrapping(), machInst, gem5::StaticInst::mnemonic, gem5::NoFault, panic, and gem5::ArmISA::TRAPPED_WFI_WFE.

Referenced by trapWFx().

◆ checkForWFxTrap64()

|

protected |

Check if WFE/WFI instruction execution in aarch64 should be trapped.

See aarch64/exceptions/traps/AArch64.checkForWFxTrap in the ARM ARM psueodcode library.

Definition at line 859 of file static_inst.cc.

References generateTrap(), gem5::ArmSystem::haveEL(), gem5::ArmISA::iss, isWFxTrapping(), gem5::NoFault, and gem5::ArmISA::TRAPPED_WFI_WFE.

Referenced by checkForWFxTrap32().

◆ checkFPAdvSIMDEnabled64()

|

protected |

Check an Advaned SIMD access against CPACR_EL1, CPTR_EL2, and CPTR_EL3.

See aarch64/exceptions/traps/AArch64.CheckFPAdvSIMDEnabled in the ARM ARM psueodcode library.

Definition at line 700 of file static_inst.cc.

References advSIMDFPAccessTrap64(), checkFPAdvSIMDTrap64(), gem5::ArmISA::currEL(), gem5::ArmISA::el, gem5::ArmISA::EL0, gem5::ArmISA::EL1, and gem5::ArmISA::ELIsInHost().

Referenced by checkAdvSIMDOrFPEnabled32().

◆ checkFPAdvSIMDTrap64()

|

protected |

Check an Advaned SIMD access against CPTR_EL2 and CPTR_EL3.

See aarch64/exceptions/traps/AArch64.CheckFPAdvSIMDTrap in the ARM ARM psueodcode library.

Definition at line 661 of file static_inst.cc.

References advSIMDFPAccessTrap64(), gem5::ArmISA::currEL(), gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL2Enabled(), gem5::ArmISA::EL3, gem5::ArmSystem::haveEL(), gem5::ArmISA::HaveExt(), gem5::ArmISA::MISCREG_CPTR_EL2, gem5::ArmISA::MISCREG_CPTR_EL3, gem5::ArmISA::MISCREG_HCR_EL2, gem5::NoFault, and gem5::ThreadContext::readMiscReg().

Referenced by checkAdvSIMDOrFPEnabled32(), and checkFPAdvSIMDEnabled64().

◆ checkSETENDEnabled()

|

protected |

Check if SETEND instruction execution in aarch32 should be trapped.

See aarch32/exceptions/traps/AArch32.CheckSETENDEnabled in the ARM ARM pseudocode library.

Definition at line 903 of file static_inst.cc.

References gem5::ArmISA::currEL(), gem5::ArmISA::EL2, gem5::ArmISA::isSecure(), gem5::ArmISA::MISCREG_HSCTLR, gem5::ArmISA::MISCREG_SCTLR, gem5::NoFault, gem5::ThreadContext::readMiscRegNoEffect(), gem5::ArmISA::snsBankedIndex(), and undefinedFault32().

◆ checkSmeAccess()

|

protected |

Check an SME access against CPACR_EL1, CPTR_EL2, and CPTR_EL3.

This is purely used from the management instructions as it should be possible to call SMSTART/SMSTOP without having the floating point flags correctly set up.

Definition at line 1096 of file static_inst.cc.

References gem5::ArmISA::el, gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL2Enabled(), gem5::ArmISA::EL3, gem5::ArmISA::ELIsInHost(), gem5::ArmSystem::haveEL(), gem5::ArmISA::HaveExt(), gem5::ArmISA::MISCREG_CPTR_EL2, gem5::ArmISA::MISCREG_CPTR_EL3, gem5::ArmISA::MISCREG_HCR_EL2, gem5::NoFault, gem5::ThreadContext::readMiscReg(), and smeAccessTrap().

◆ checkSmeEnabled()

|

protected |

Check if SME is enabled by checking the SME and FP bits of CPACR_EL1, CPTR_EL2, and CPTR_EL3.

Definition at line 1046 of file static_inst.cc.

References advSIMDFPAccessTrap64(), gem5::ArmISA::el, gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL2Enabled(), gem5::ArmISA::EL3, gem5::ArmISA::ELIsInHost(), gem5::ArmSystem::haveEL(), gem5::ArmISA::HaveExt(), gem5::ArmISA::MISCREG_CPTR_EL2, gem5::ArmISA::MISCREG_CPTR_EL3, gem5::ArmISA::MISCREG_HCR_EL2, gem5::NoFault, gem5::ThreadContext::readMiscReg(), and smeAccessTrap().

Referenced by checkSveEnabled(), and checkSveSmeEnabled().

◆ checkSveEnabled()

|

protected |

Check an SVE access against CPACR_EL1, CPTR_EL2, and CPTR_EL3.

Definition at line 983 of file static_inst.cc.

References advSIMDFPAccessTrap64(), checkSmeEnabled(), gem5::ArmISA::el, gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL2Enabled(), gem5::ArmISA::EL3, gem5::ArmISA::ELIsInHost(), gem5::ArmSystem::haveEL(), gem5::ArmISA::HaveExt(), gem5::ArmISA::MISCREG_CPTR_EL2, gem5::ArmISA::MISCREG_CPTR_EL3, gem5::ArmISA::MISCREG_HCR_EL2, gem5::ArmISA::MISCREG_SVCR, gem5::NoFault, gem5::ThreadContext::readMiscReg(), and sveAccessTrap().

Referenced by checkSveSmeEnabled().

◆ checkSveSmeEnabled()

|

protected |

Check an SVE access against CPACR_EL1, CPTR_EL2, and CPTR_EL3, but choosing the correct set of traps to check based on Streaming Mode.

Definition at line 1133 of file static_inst.cc.

References checkSmeEnabled(), checkSveEnabled(), gem5::ArmISA::MISCREG_SVCR, and gem5::ThreadContext::readMiscReg().

◆ cpsrWriteByInstr()

|

inlinestaticprotected |

Definition at line 237 of file static_inst.hh.

References activateBreakpoint(), gem5::ArmISA::badMode(), gem5::bits(), gem5::ArmISA::EL2, gem5::ArmSystem::haveEL(), gem5::ArmISA::isSecure(), gem5::ArmISA::mask, gem5::ArmISA::MODE_FIQ, gem5::ArmISA::MODE_HYP, gem5::ArmISA::MODE_MON, gem5::ArmISA::MODE_USER, gem5::ArmISA::nmfi, gem5::X86ISA::val, and warn_once.

◆ cSwap() [1/2]

|

inlinestaticprotected |

Definition at line 350 of file static_inst.hh.

References gem5::letobe(), and gem5::X86ISA::val.

◆ cSwap() [2/2]

|

inlinestaticprotected |

Definition at line 361 of file static_inst.hh.

References gem5::RefCounted::count, gem5::X86ISA::E, gem5::htole(), gem5::ArmISA::i, gem5::letobe(), gem5::letoh(), and gem5::X86ISA::val.

◆ disabledFault()

|

inlineprotected |

Definition at line 401 of file static_inst.hh.

References undefined().

Referenced by checkAdvSIMDOrFPEnabled32().

◆ encoding()

|

inline |

Returns the real encoding of the instruction: the machInst field is in fact always 64 bit wide and contains some instruction metadata, which means it differs from the real opcode.

Definition at line 589 of file static_inst.hh.

References instSize(), machInst, and gem5::ArmISA::mask.

Referenced by gem5::UnknownOp64::generateDisassembly(), gem5::ArmISA::UndefinedInstruction::invoke(), and gem5::ArmISA::ArmFault::invoke64().

◆ extendReg64()

|

protected |

Definition at line 134 of file static_inst.cc.

References gem5::RiscvISA::base, gem5::bits(), gem5::ArmISA::len, gem5::ArmISA::mask, gem5::ArmISA::SXTB, gem5::ArmISA::SXTH, gem5::ArmISA::SXTW, gem5::ArmISA::SXTX, gem5::ArmISA::UXTB, gem5::ArmISA::UXTH, gem5::ArmISA::UXTW, gem5::ArmISA::UXTX, and gem5::ArmISA::width.

◆ generalExceptionsToAArch64()

|

protected |

Return true if exceptions normally routed to EL1 are being handled at an Exception level using AArch64, because either EL1 is using AArch64 or TGE is in force and EL2 is using AArch64.

See aarch32/exceptions/exceptions/AArch32.GeneralExceptionsToAArch64 in the ARM ARM pseudocode library.

Definition at line 1287 of file static_inst.cc.

References gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::ELIs32(), gem5::ArmSystem::haveEL(), gem5::ArmISA::isSecure(), gem5::ArmISA::MISCREG_HCR_EL2, and gem5::ThreadContext::readMiscReg().

Referenced by undefinedFault32().

◆ generateDisassembly()

|

overrideprotectedvirtual |

Internal function to generate disassembly string.

Implements gem5::StaticInst.

Reimplemented in gem5::ArmISA::BranchEret64, gem5::ArmISA::BranchEretA64, gem5::ArmISA::BranchImm64, gem5::ArmISA::BranchImm, gem5::ArmISA::BranchImmCond64, gem5::ArmISA::BranchImmImmReg64, gem5::ArmISA::BranchImmReg64, gem5::ArmISA::BranchReg64, gem5::ArmISA::BranchReg, gem5::ArmISA::BranchRegReg64, gem5::ArmISA::BranchRegReg, gem5::ArmISA::BranchRet64, gem5::ArmISA::BranchRetA64, gem5::ArmISA::DataImmOp, gem5::ArmISA::DataRegOp, gem5::ArmISA::DataRegRegOp, gem5::ArmISA::DataX1Reg2ImmOp, gem5::ArmISA::DataX1RegImmOp, gem5::ArmISA::DataX1RegOp, gem5::ArmISA::DataX2RegImmOp, gem5::ArmISA::DataX2RegOp, gem5::ArmISA::DataX3RegOp, gem5::ArmISA::DataXCondCompImmOp, gem5::ArmISA::DataXCondCompRegOp, gem5::ArmISA::DataXCondSelOp, gem5::ArmISA::DataXERegOp, gem5::ArmISA::DataXImmOnlyOp, gem5::ArmISA::DataXImmOp, gem5::ArmISA::DataXSRegOp, gem5::ArmISA::FpCondCompRegOp, gem5::ArmISA::FpCondSelOp, gem5::ArmISA::FpRegImmOp, gem5::ArmISA::FpRegRegImmOp, gem5::ArmISA::FpRegRegOp, gem5::ArmISA::FpRegRegRegCondOp, gem5::ArmISA::FpRegRegRegImmOp, gem5::ArmISA::FpRegRegRegOp, gem5::ArmISA::FpRegRegRegRegOp, gem5::ArmISA::MemoryAtomicPair64, gem5::ArmISA::MemoryDImm64, gem5::ArmISA::MemoryDImmEx64, gem5::ArmISA::MemoryEx64, gem5::ArmISA::MemoryImm64, gem5::ArmISA::MemoryLiteral64, gem5::ArmISA::MemoryPostIndex64, gem5::ArmISA::MemoryPreIndex64, gem5::ArmISA::MemoryRaw64, gem5::ArmISA::MemoryReg64, gem5::ArmISA::MicroIntImmOp, gem5::ArmISA::MicroIntImmXOp, gem5::ArmISA::MicroIntMov, gem5::ArmISA::MicroIntOp, gem5::ArmISA::MicroIntRegXOp, gem5::ArmISA::MicroMemOp, gem5::ArmISA::MicroMemPairOp, gem5::ArmISA::MicroSetPCCPSR, gem5::ArmISA::PredImmOp, gem5::ArmISA::PredIntOp, gem5::ArmISA::PredMacroOp, gem5::ArmISA::RfeOp, gem5::ArmISA::SmeAddOp, gem5::ArmISA::SmeAddVlOp, gem5::ArmISA::SmeLd1xSt1xOp, gem5::ArmISA::SmeLdrStrOp, gem5::ArmISA::SmeMovExtractOp, gem5::ArmISA::SmeMovInsertOp, gem5::ArmISA::SmeOPOp, gem5::ArmISA::SmeRdsvlOp, gem5::ArmISA::SmeZeroOp, gem5::ArmISA::SrsOp, gem5::ArmISA::SveAdrOp, gem5::ArmISA::SveBinConstrPredOp, gem5::ArmISA::SveBinDestrPredOp, gem5::ArmISA::SveBinIdxUnpredOp, gem5::ArmISA::SveBinImmIdxUnpredOp, gem5::ArmISA::SveBinImmPredOp, gem5::ArmISA::SveBinImmUnpredConstrOp, gem5::ArmISA::SveBinImmUnpredDestrOp, gem5::ArmISA::SveBinUnpredOp, gem5::ArmISA::SveBinWideImmUnpredOp, gem5::ArmISA::SveClampOp, gem5::ArmISA::SveCmpImmOp, gem5::ArmISA::SveCmpOp, gem5::ArmISA::SveComplexIdxOp, gem5::ArmISA::SveComplexOp, gem5::ArmISA::SveCompTermOp, gem5::ArmISA::SveContigMemSI, gem5::ArmISA::SveContigMemSS, gem5::ArmISA::SveDotProdIdxOp, gem5::ArmISA::SveDotProdOp, gem5::ArmISA::SveElemCountOp, gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >, gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >, gem5::ArmISA::SveIndexIIOp, gem5::ArmISA::SveIndexIROp, gem5::ArmISA::SveIndexRIOp, gem5::ArmISA::SveIndexRROp, gem5::ArmISA::SveIntCmpImmOp, gem5::ArmISA::SveIntCmpOp, gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >, gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >, gem5::ArmISA::SveMemPredFillSpill, gem5::ArmISA::SveMemVecFillSpill, gem5::ArmISA::SveOrdReducOp, gem5::ArmISA::SvePartBrkOp, gem5::ArmISA::SvePartBrkPropOp, gem5::ArmISA::SvePredBinPermOp, gem5::ArmISA::SvePredCountOp, gem5::ArmISA::SvePredCountPredOp, gem5::ArmISA::SvePredLogicalOp, gem5::ArmISA::SvePredTestOp, gem5::ArmISA::SvePredUnaryWImplicitDstOp, gem5::ArmISA::SvePredUnaryWImplicitSrcOp, gem5::ArmISA::SvePredUnaryWImplicitSrcPredOp, gem5::ArmISA::SvePselOp, gem5::ArmISA::SvePtrueOp, gem5::ArmISA::SveReducOp, gem5::ArmISA::SveSelectOp, gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >, gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >, gem5::ArmISA::SveTblOp, gem5::ArmISA::SveTerImmUnpredOp, gem5::ArmISA::SveTerPredOp, gem5::ArmISA::SveTerUnpredOp, gem5::ArmISA::SveUnaryPredOp, gem5::ArmISA::SveUnaryPredPredOp, gem5::ArmISA::SveUnarySca2VecUnpredOp, gem5::ArmISA::SveUnaryUnpredOp, gem5::ArmISA::SveUnaryWideImmPredOp, gem5::ArmISA::SveUnaryWideImmUnpredOp, gem5::ArmISA::SveUnpackOp, gem5::ArmISA::SveWhileOp, gem5::ArmISA::SveWImplicitSrcDstOp, gem5::ArmISA::SysDC64, gem5::ArmISAInst::MicroTmeBasic64, gem5::ArmISAInst::TmeImmOp64, gem5::ArmISAInst::TmeRegNone64, gem5::DecoderFaultInst, gem5::FailUnimplemented, gem5::ImmOp64, gem5::ImmOp, gem5::McrMrcImplDefined, gem5::McrMrcMiscInst, gem5::McrrOp, gem5::MiscRegImmOp64, gem5::MiscRegImplDefined64, gem5::MiscRegRegImmOp64, gem5::MiscRegRegImmOp, gem5::MrrcOp, gem5::MrsOp, gem5::MsrImmOp, gem5::MsrRegOp, gem5::RegImmImmOp64, gem5::RegImmImmOp, gem5::RegImmOp, gem5::RegImmRegOp, gem5::RegImmRegShiftOp, gem5::RegMiscRegImmOp64, gem5::RegMiscRegImmOp, gem5::RegNone, gem5::RegOp64, gem5::RegOp, gem5::RegRegImmImmOp64, gem5::RegRegImmImmOp, gem5::RegRegImmOp, gem5::RegRegOp, gem5::RegRegRegImmOp64, gem5::RegRegRegImmOp, gem5::RegRegRegOp, gem5::RegRegRegRegOp, gem5::UnknownOp64, gem5::UnknownOp, and gem5::WarnUnimplemented.

Definition at line 626 of file static_inst.cc.

References gem5::MipsISA::pc, printMnemonic(), and gem5::ArmISA::ss.

◆ generateTrap()

| Fault gem5::ArmISA::ArmStaticInst::generateTrap | ( | ArmISA::ExceptionLevel | el, |

| ArmISA::ExceptionClass | ec, | ||

| uint32_t | iss ) const |

Definition at line 1314 of file static_inst.cc.

References gem5::ArmISA::ec, gem5::ArmISA::el, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL3, getEMI(), gem5::ArmISA::iss, and panic.

Referenced by advSIMDFPAccessTrap64(), checkForWFxTrap64(), smeAccessTrap(), and sveAccessTrap().

◆ getCurSmeVecLen()

|

inlinestatic |

Definition at line 625 of file static_inst.hh.

References getCurSmeVecLenInBits().

◆ getCurSmeVecLenInBits()

|

static |

Definition at line 1307 of file static_inst.cc.

References gem5::ArmISA::ISA::getCurSmeVecLenInBits(), and gem5::ThreadContext::getIsaPtr().

Referenced by getCurSmeVecLen(), and getCurSmeVecLenInQWords().

◆ getCurSmeVecLenInQWords()

|

inlinestatic |

Definition at line 618 of file static_inst.hh.

References getCurSmeVecLenInBits().

◆ getCurSveVecLen()

|

inlinestatic |

Definition at line 610 of file static_inst.hh.

References getCurSveVecLenInBits().

Referenced by gem5::trace::TarmacParserRecord::TarmacParserRecord().

◆ getCurSveVecLenInBits()

|

static |

Definition at line 1300 of file static_inst.cc.

References gem5::ArmISA::ISA::getCurSveVecLenInBits(), and gem5::ThreadContext::getIsaPtr().

Referenced by getCurSveVecLen(), getCurSveVecLenInQWords(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updatePred(), and gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updateVec().

◆ getCurSveVecLenInQWords()

|

inlinestatic |

Definition at line 603 of file static_inst.hh.

References getCurSveVecLenInBits().

◆ getEMI()

|

inlineoverrideprotectedvirtual |

Reimplemented from gem5::StaticInst.

Definition at line 215 of file static_inst.hh.

References machInst.

Referenced by generateTrap().

◆ getIntWidth()

|

inline |

Definition at line 570 of file static_inst.hh.

References intWidth.

◆ getPSTATEFromPSR()

|

protected |

Get the new PSTATE from a SPSR register in preparation for an exception return.

See shared/functions/system/SetPSTATEFromPSR in the ARM ARM pseudocode library.

Definition at line 1228 of file static_inst.cc.

References gem5::ArmISA::currEL(), gem5::ArmISA::getRestoredITBits(), gem5::ArmISA::ISA::getSelfDebug(), gem5::ArmISA::illegalExceptionReturn(), gem5::ArmISA::sd, gem5::ArmISA::ss, and gem5::ArmISA::unknownMode32().

◆ instSize()

|

inline |

Returns the byte size of current instruction.

Definition at line 577 of file static_inst.hh.

References machInst.

Referenced by encoding().

◆ isWFxTrapping()

|

inlineprotected |

Definition at line 790 of file static_inst.cc.

References gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL3, gem5::ArmISA::MISCREG_HCR_EL2, gem5::ArmISA::MISCREG_SCR_EL3, gem5::ArmISA::MISCREG_SCTLR_EL1, and gem5::ThreadContext::readMiscReg().

Referenced by checkForWFxTrap32(), and checkForWFxTrap64().

◆ printCCReg()

|

protected |

Definition at line 364 of file static_inst.cc.

References gem5::ccprintf(), gem5::X86ISA::os, and gem5::ArmISA::cc_reg::RegName.

◆ printCondition()

|

protected |

Definition at line 417 of file static_inst.cc.

References gem5::ArmISA::COND_AL, gem5::ArmISA::COND_CC, gem5::ArmISA::COND_CS, gem5::ArmISA::COND_EQ, gem5::ArmISA::COND_GE, gem5::ArmISA::COND_GT, gem5::ArmISA::COND_HI, gem5::ArmISA::COND_LE, gem5::ArmISA::COND_LS, gem5::ArmISA::COND_LT, gem5::ArmISA::COND_MI, gem5::ArmISA::COND_NE, gem5::ArmISA::COND_PL, gem5::ArmISA::COND_UC, gem5::ArmISA::COND_VC, gem5::ArmISA::COND_VS, gem5::X86ISA::os, and panic.

Referenced by gem5::ArmISA::DataXCondCompImmOp::generateDisassembly(), gem5::ArmISA::DataXCondCompRegOp::generateDisassembly(), gem5::ArmISA::DataXCondSelOp::generateDisassembly(), gem5::ArmISA::FpCondCompRegOp::generateDisassembly(), gem5::ArmISA::FpCondSelOp::generateDisassembly(), and printMnemonic().

◆ printDataInst() [1/2]

|

protected |

References gem5::ArmISA::imm, gem5::X86ISA::os, gem5::ArmISA::rd, gem5::ArmISA::rm, gem5::ArmISA::rn, gem5::ArmISA::rs, and gem5::ArmISA::s.

Referenced by gem5::ArmISA::DataImmOp::generateDisassembly(), gem5::ArmISA::DataRegOp::generateDisassembly(), gem5::ArmISA::DataRegRegOp::generateDisassembly(), gem5::ArmISA::DataXERegOp::generateDisassembly(), gem5::ArmISA::DataXImmOp::generateDisassembly(), gem5::ArmISA::DataXSRegOp::generateDisassembly(), gem5::ArmISA::PredImmOp::generateDisassembly(), and gem5::ArmISA::PredIntOp::generateDisassembly().

◆ printDataInst() [2/2]

|

protected |

Definition at line 594 of file static_inst.cc.

References gem5::ccprintf(), gem5::ArmISA::imm, gem5::X86ISA::os, printIntReg(), printMnemonic(), printShiftOperand(), gem5::ArmISA::rd, gem5::ArmISA::rm, gem5::ArmISA::rn, gem5::ArmISA::rs, gem5::ArmISA::s, and gem5::ArmISA::int_reg::Zero.

◆ printExtendOperand()

|

protected |

Definition at line 562 of file static_inst.cc.

References gem5::ccprintf(), gem5::X86ISA::os, printIntReg(), gem5::ArmISA::rm, gem5::ArmISA::SXTB, gem5::ArmISA::SXTH, gem5::ArmISA::SXTW, gem5::ArmISA::SXTX, gem5::ArmISA::UXTB, gem5::ArmISA::UXTH, gem5::ArmISA::UXTW, and gem5::ArmISA::UXTX.

Referenced by gem5::ArmISA::MemoryReg64::generateDisassembly(), and gem5::ArmISA::MicroIntRegXOp::generateDisassembly().

◆ printFloatReg()

|

protected |

Definition at line 345 of file static_inst.cc.

References gem5::ccprintf(), and gem5::X86ISA::os.

Referenced by gem5::ArmISA::FpRegImmOp::generateDisassembly(), gem5::ArmISA::FpRegRegImmOp::generateDisassembly(), gem5::ArmISA::FpRegRegOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegCondOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegImmOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegRegOp::generateDisassembly(), gem5::ArmISA::MicroMemOp::generateDisassembly(), gem5::ArmISA::SveOrdReducOp::generateDisassembly(), gem5::ArmISA::SveReducOp::generateDisassembly(), gem5::ArmISA::SveSelectOp::generateDisassembly(), and gem5::ArmISA::SveUnarySca2VecUnpredOp::generateDisassembly().

◆ printIntReg()

|

protected |

Print a register name for disassembly given the unique dependence tag number (FP or int).

Definition at line 299 of file static_inst.cc.

References aarch64, gem5::ccprintf(), gem5::ArmISA::FramePointerReg, intWidth, gem5::X86ISA::os, gem5::ArmISA::int_reg::Pc, gem5::ArmISA::ReturnAddressReg, gem5::ArmISA::int_reg::Spx, gem5::ArmISA::StackPointerReg, gem5::ArmISA::int_reg::Ureg0, and gem5::ArmISA::int_reg::X31.

Referenced by gem5::ArmISA::BranchImmImmReg64::generateDisassembly(), gem5::ArmISA::BranchImmReg64::generateDisassembly(), gem5::ArmISA::BranchReg64::generateDisassembly(), gem5::ArmISA::BranchReg::generateDisassembly(), gem5::ArmISA::BranchRegReg64::generateDisassembly(), gem5::ArmISA::BranchRegReg::generateDisassembly(), gem5::ArmISA::BranchRet64::generateDisassembly(), gem5::ArmISA::BranchRetA64::generateDisassembly(), gem5::ArmISA::DataX1Reg2ImmOp::generateDisassembly(), gem5::ArmISA::DataX1RegImmOp::generateDisassembly(), gem5::ArmISA::DataX1RegOp::generateDisassembly(), gem5::ArmISA::DataX2RegImmOp::generateDisassembly(), gem5::ArmISA::DataX2RegOp::generateDisassembly(), gem5::ArmISA::DataX3RegOp::generateDisassembly(), gem5::ArmISA::DataXCondCompImmOp::generateDisassembly(), gem5::ArmISA::DataXCondCompRegOp::generateDisassembly(), gem5::ArmISA::DataXCondSelOp::generateDisassembly(), gem5::ArmISA::DataXImmOnlyOp::generateDisassembly(), gem5::ArmISA::FpCondCompRegOp::generateDisassembly(), gem5::ArmISA::FpCondSelOp::generateDisassembly(), gem5::ArmISA::MemoryAtomicPair64::generateDisassembly(), gem5::ArmISA::MemoryDImm64::generateDisassembly(), gem5::ArmISA::MemoryDImmEx64::generateDisassembly(), gem5::ArmISA::MemoryEx64::generateDisassembly(), gem5::ArmISA::MemoryLiteral64::generateDisassembly(), gem5::ArmISA::MicroIntImmOp::generateDisassembly(), gem5::ArmISA::MicroIntImmXOp::generateDisassembly(), gem5::ArmISA::MicroIntMov::generateDisassembly(), gem5::ArmISA::MicroIntOp::generateDisassembly(), gem5::ArmISA::MicroIntRegXOp::generateDisassembly(), gem5::ArmISA::MicroMemOp::generateDisassembly(), gem5::ArmISA::MicroMemPairOp::generateDisassembly(), gem5::ArmISA::RfeOp::generateDisassembly(), gem5::ArmISA::SmeLd1xSt1xOp::generateDisassembly(), gem5::ArmISA::SmeLdrStrOp::generateDisassembly(), gem5::ArmISA::SmeMovExtractOp::generateDisassembly(), gem5::ArmISA::SmeMovInsertOp::generateDisassembly(), gem5::ArmISA::SrsOp::generateDisassembly(), gem5::ArmISA::SveCompTermOp::generateDisassembly(), gem5::ArmISA::SveContigMemSI::generateDisassembly(), gem5::ArmISA::SveContigMemSS::generateDisassembly(), gem5::ArmISA::SveElemCountOp::generateDisassembly(), gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::generateDisassembly(), gem5::ArmISA::SveIndexIROp::generateDisassembly(), gem5::ArmISA::SveIndexRIOp::generateDisassembly(), gem5::ArmISA::SveIndexRROp::generateDisassembly(), gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveMemPredFillSpill::generateDisassembly(), gem5::ArmISA::SveMemVecFillSpill::generateDisassembly(), gem5::ArmISA::SvePredCountOp::generateDisassembly(), gem5::ArmISA::SvePredCountPredOp::generateDisassembly(), gem5::ArmISA::SvePselOp::generateDisassembly(), gem5::ArmISA::SveSelectOp::generateDisassembly(), gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveUnarySca2VecUnpredOp::generateDisassembly(), gem5::ArmISA::SveWhileOp::generateDisassembly(), gem5::ArmISA::SysDC64::generateDisassembly(), gem5::ArmISAInst::TmeRegNone64::generateDisassembly(), gem5::McrrOp::generateDisassembly(), gem5::MiscRegRegImmOp64::generateDisassembly(), gem5::MiscRegRegImmOp::generateDisassembly(), gem5::MrrcOp::generateDisassembly(), gem5::MrsOp::generateDisassembly(), gem5::MsrRegOp::generateDisassembly(), gem5::RegImmImmOp64::generateDisassembly(), gem5::RegImmImmOp::generateDisassembly(), gem5::RegImmOp::generateDisassembly(), gem5::RegImmRegOp::generateDisassembly(), gem5::RegImmRegShiftOp::generateDisassembly(), gem5::RegMiscRegImmOp64::generateDisassembly(), gem5::RegMiscRegImmOp::generateDisassembly(), gem5::RegNone::generateDisassembly(), gem5::RegOp64::generateDisassembly(), gem5::RegOp::generateDisassembly(), gem5::RegRegImmImmOp64::generateDisassembly(), gem5::RegRegImmImmOp::generateDisassembly(), gem5::RegRegImmOp::generateDisassembly(), gem5::RegRegOp::generateDisassembly(), gem5::RegRegRegImmOp64::generateDisassembly(), gem5::RegRegRegImmOp::generateDisassembly(), gem5::RegRegRegOp::generateDisassembly(), gem5::RegRegRegRegOp::generateDisassembly(), printDataInst(), gem5::ArmISA::Memory::printDest(), gem5::ArmISA::MemoryDImm::printDest(), gem5::ArmISA::MemoryDReg::printDest(), gem5::ArmISA::MemoryExDImm::printDest(), gem5::ArmISA::MemoryExImm::printDest(), printExtendOperand(), gem5::ArmISA::Memory::printInst(), gem5::ArmISA::MemoryReg::printOffset(), printShiftOperand(), and gem5::ArmISA::Memory64::startDisassembly().

◆ printMemSymbol()

|

protected |

Definition at line 480 of file static_inst.cc.

References gem5::X86ISA::addr, gem5::ccprintf(), gem5::loader::SymbolTable::end(), gem5::loader::SymbolTable::findNearest(), and gem5::X86ISA::os.

◆ printMiscReg()

|

protected |

Definition at line 370 of file static_inst.cc.

References gem5::ccprintf(), gem5::ArmISA::miscRegName, gem5::ArmISA::NUM_MISCREGS, and gem5::X86ISA::os.

Referenced by gem5::McrrOp::generateDisassembly(), gem5::MiscRegImmOp64::generateDisassembly(), gem5::MiscRegRegImmOp64::generateDisassembly(), gem5::MiscRegRegImmOp::generateDisassembly(), gem5::MrrcOp::generateDisassembly(), gem5::RegMiscRegImmOp64::generateDisassembly(), and gem5::RegMiscRegImmOp::generateDisassembly().

◆ printMnemonic()

|

protected |

Definition at line 377 of file static_inst.cc.

References aarch64, machInst, gem5::StaticInst::mnemonic, gem5::X86ISA::os, and printCondition().

Referenced by generateDisassembly(), gem5::ArmISA::BranchEret64::generateDisassembly(), gem5::ArmISA::BranchEretA64::generateDisassembly(), gem5::ArmISA::BranchImm64::generateDisassembly(), gem5::ArmISA::BranchImm::generateDisassembly(), gem5::ArmISA::BranchImmCond64::generateDisassembly(), gem5::ArmISA::BranchImmImmReg64::generateDisassembly(), gem5::ArmISA::BranchImmReg64::generateDisassembly(), gem5::ArmISA::BranchReg64::generateDisassembly(), gem5::ArmISA::BranchReg::generateDisassembly(), gem5::ArmISA::BranchRegReg64::generateDisassembly(), gem5::ArmISA::BranchRegReg::generateDisassembly(), gem5::ArmISA::BranchRet64::generateDisassembly(), gem5::ArmISA::BranchRetA64::generateDisassembly(), gem5::ArmISA::DataX1Reg2ImmOp::generateDisassembly(), gem5::ArmISA::DataX1RegImmOp::generateDisassembly(), gem5::ArmISA::DataX1RegOp::generateDisassembly(), gem5::ArmISA::DataX2RegImmOp::generateDisassembly(), gem5::ArmISA::DataX2RegOp::generateDisassembly(), gem5::ArmISA::DataX3RegOp::generateDisassembly(), gem5::ArmISA::DataXCondCompImmOp::generateDisassembly(), gem5::ArmISA::DataXCondCompRegOp::generateDisassembly(), gem5::ArmISA::DataXCondSelOp::generateDisassembly(), gem5::ArmISA::DataXImmOnlyOp::generateDisassembly(), gem5::ArmISA::FpCondCompRegOp::generateDisassembly(), gem5::ArmISA::FpCondSelOp::generateDisassembly(), gem5::ArmISA::FpRegImmOp::generateDisassembly(), gem5::ArmISA::FpRegRegImmOp::generateDisassembly(), gem5::ArmISA::FpRegRegOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegCondOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegImmOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegOp::generateDisassembly(), gem5::ArmISA::FpRegRegRegRegOp::generateDisassembly(), gem5::ArmISA::MemoryAtomicPair64::generateDisassembly(), gem5::ArmISA::MemoryDImm64::generateDisassembly(), gem5::ArmISA::MemoryDImmEx64::generateDisassembly(), gem5::ArmISA::MemoryEx64::generateDisassembly(), gem5::ArmISA::MemoryLiteral64::generateDisassembly(), gem5::ArmISA::MicroIntImmOp::generateDisassembly(), gem5::ArmISA::MicroIntImmXOp::generateDisassembly(), gem5::ArmISA::MicroIntMov::generateDisassembly(), gem5::ArmISA::MicroIntOp::generateDisassembly(), gem5::ArmISA::MicroIntRegXOp::generateDisassembly(), gem5::ArmISA::MicroMemOp::generateDisassembly(), gem5::ArmISA::MicroMemPairOp::generateDisassembly(), gem5::ArmISA::MicroSetPCCPSR::generateDisassembly(), gem5::ArmISA::RfeOp::generateDisassembly(), gem5::ArmISA::SmeAddOp::generateDisassembly(), gem5::ArmISA::SmeAddVlOp::generateDisassembly(), gem5::ArmISA::SmeLd1xSt1xOp::generateDisassembly(), gem5::ArmISA::SmeLdrStrOp::generateDisassembly(), gem5::ArmISA::SmeMovExtractOp::generateDisassembly(), gem5::ArmISA::SmeMovInsertOp::generateDisassembly(), gem5::ArmISA::SmeOPOp::generateDisassembly(), gem5::ArmISA::SmeRdsvlOp::generateDisassembly(), gem5::ArmISA::SmeZeroOp::generateDisassembly(), gem5::ArmISA::SrsOp::generateDisassembly(), gem5::ArmISA::SveAdrOp::generateDisassembly(), gem5::ArmISA::SveBinConstrPredOp::generateDisassembly(), gem5::ArmISA::SveBinDestrPredOp::generateDisassembly(), gem5::ArmISA::SveBinIdxUnpredOp::generateDisassembly(), gem5::ArmISA::SveBinImmIdxUnpredOp::generateDisassembly(), gem5::ArmISA::SveBinImmPredOp::generateDisassembly(), gem5::ArmISA::SveBinImmUnpredConstrOp::generateDisassembly(), gem5::ArmISA::SveBinImmUnpredDestrOp::generateDisassembly(), gem5::ArmISA::SveBinUnpredOp::generateDisassembly(), gem5::ArmISA::SveBinWideImmUnpredOp::generateDisassembly(), gem5::ArmISA::SveClampOp::generateDisassembly(), gem5::ArmISA::SveCmpImmOp::generateDisassembly(), gem5::ArmISA::SveCmpOp::generateDisassembly(), gem5::ArmISA::SveComplexIdxOp::generateDisassembly(), gem5::ArmISA::SveComplexOp::generateDisassembly(), gem5::ArmISA::SveCompTermOp::generateDisassembly(), gem5::ArmISA::SveContigMemSI::generateDisassembly(), gem5::ArmISA::SveContigMemSS::generateDisassembly(), gem5::ArmISA::SveDotProdIdxOp::generateDisassembly(), gem5::ArmISA::SveDotProdOp::generateDisassembly(), gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::generateDisassembly(), gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::generateDisassembly(), gem5::ArmISA::SveIndexIIOp::generateDisassembly(), gem5::ArmISA::SveIndexIROp::generateDisassembly(), gem5::ArmISA::SveIndexRIOp::generateDisassembly(), gem5::ArmISA::SveIndexRROp::generateDisassembly(), gem5::ArmISA::SveIntCmpImmOp::generateDisassembly(), gem5::ArmISA::SveIntCmpOp::generateDisassembly(), gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveMemPredFillSpill::generateDisassembly(), gem5::ArmISA::SveMemVecFillSpill::generateDisassembly(), gem5::ArmISA::SveOrdReducOp::generateDisassembly(), gem5::ArmISA::SvePartBrkOp::generateDisassembly(), gem5::ArmISA::SvePartBrkPropOp::generateDisassembly(), gem5::ArmISA::SvePredBinPermOp::generateDisassembly(), gem5::ArmISA::SvePredCountOp::generateDisassembly(), gem5::ArmISA::SvePredCountPredOp::generateDisassembly(), gem5::ArmISA::SvePredLogicalOp::generateDisassembly(), gem5::ArmISA::SvePredTestOp::generateDisassembly(), gem5::ArmISA::SvePredUnaryWImplicitDstOp::generateDisassembly(), gem5::ArmISA::SvePredUnaryWImplicitSrcOp::generateDisassembly(), gem5::ArmISA::SvePredUnaryWImplicitSrcPredOp::generateDisassembly(), gem5::ArmISA::SvePselOp::generateDisassembly(), gem5::ArmISA::SvePtrueOp::generateDisassembly(), gem5::ArmISA::SveReducOp::generateDisassembly(), gem5::ArmISA::SveSelectOp::generateDisassembly(), gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveTblOp::generateDisassembly(), gem5::ArmISA::SveTerImmUnpredOp::generateDisassembly(), gem5::ArmISA::SveTerPredOp::generateDisassembly(), gem5::ArmISA::SveTerUnpredOp::generateDisassembly(), gem5::ArmISA::SveUnaryPredOp::generateDisassembly(), gem5::ArmISA::SveUnaryPredPredOp::generateDisassembly(), gem5::ArmISA::SveUnarySca2VecUnpredOp::generateDisassembly(), gem5::ArmISA::SveUnaryUnpredOp::generateDisassembly(), gem5::ArmISA::SveUnaryWideImmPredOp::generateDisassembly(), gem5::ArmISA::SveUnaryWideImmUnpredOp::generateDisassembly(), gem5::ArmISA::SveUnpackOp::generateDisassembly(), gem5::ArmISA::SveWhileOp::generateDisassembly(), gem5::ArmISA::SveWImplicitSrcDstOp::generateDisassembly(), gem5::ArmISA::SysDC64::generateDisassembly(), gem5::ArmISAInst::MicroTmeBasic64::generateDisassembly(), gem5::ArmISAInst::TmeImmOp64::generateDisassembly(), gem5::ArmISAInst::TmeRegNone64::generateDisassembly(), gem5::ImmOp64::generateDisassembly(), gem5::ImmOp::generateDisassembly(), gem5::McrrOp::generateDisassembly(), gem5::MiscRegImmOp64::generateDisassembly(), gem5::MiscRegRegImmOp64::generateDisassembly(), gem5::MiscRegRegImmOp::generateDisassembly(), gem5::MrrcOp::generateDisassembly(), gem5::MrsOp::generateDisassembly(), gem5::RegImmImmOp64::generateDisassembly(), gem5::RegImmImmOp::generateDisassembly(), gem5::RegImmOp::generateDisassembly(), gem5::RegImmRegOp::generateDisassembly(), gem5::RegImmRegShiftOp::generateDisassembly(), gem5::RegMiscRegImmOp64::generateDisassembly(), gem5::RegMiscRegImmOp::generateDisassembly(), gem5::RegNone::generateDisassembly(), gem5::RegOp64::generateDisassembly(), gem5::RegOp::generateDisassembly(), gem5::RegRegImmImmOp64::generateDisassembly(), gem5::RegRegImmImmOp::generateDisassembly(), gem5::RegRegImmOp::generateDisassembly(), gem5::RegRegOp::generateDisassembly(), gem5::RegRegRegImmOp64::generateDisassembly(), gem5::RegRegRegImmOp::generateDisassembly(), gem5::RegRegRegOp::generateDisassembly(), gem5::RegRegRegRegOp::generateDisassembly(), printDataInst(), gem5::ArmISA::Memory::printInst(), gem5::MsrBase::printMsrBase(), and gem5::ArmISA::Memory64::startDisassembly().

◆ printPFflags()

|

protected |

Definition at line 334 of file static_inst.cc.

References gem5::ccprintf(), and gem5::X86ISA::os.

Referenced by gem5::ArmISA::Memory64::startDisassembly().

◆ printShiftOperand()

|

protected |

Definition at line 498 of file static_inst.cc.

References gem5::X86ISA::os, panic, printIntReg(), gem5::ArmISA::rm, gem5::ArmISA::rs, and gem5::ArmISA::int_reg::Zero.

Referenced by gem5::RegImmRegShiftOp::generateDisassembly(), and printDataInst().

◆ printTarget()

|

protected |

Definition at line 398 of file static_inst.cc.

References gem5::ccprintf(), gem5::loader::SymbolTable::end(), gem5::loader::SymbolTable::findNearest(), and gem5::X86ISA::os.

Referenced by gem5::ArmISA::BranchImm64::generateDisassembly(), gem5::ArmISA::BranchImm::generateDisassembly(), gem5::ArmISA::BranchImmCond64::generateDisassembly(), gem5::ArmISA::BranchImmImmReg64::generateDisassembly(), and gem5::ArmISA::BranchImmReg64::generateDisassembly().

◆ printVecPredReg()

|

protected |

Definition at line 358 of file static_inst.cc.

References gem5::ccprintf(), and gem5::X86ISA::os.

Referenced by gem5::ArmISA::SmeAddOp::generateDisassembly(), gem5::ArmISA::SmeLd1xSt1xOp::generateDisassembly(), gem5::ArmISA::SmeMovExtractOp::generateDisassembly(), gem5::ArmISA::SmeMovInsertOp::generateDisassembly(), gem5::ArmISA::SmeOPOp::generateDisassembly(), gem5::ArmISA::SveBinConstrPredOp::generateDisassembly(), gem5::ArmISA::SveBinDestrPredOp::generateDisassembly(), gem5::ArmISA::SveBinImmPredOp::generateDisassembly(), gem5::ArmISA::SveBinImmUnpredConstrOp::generateDisassembly(), gem5::ArmISA::SveCmpImmOp::generateDisassembly(), gem5::ArmISA::SveCmpOp::generateDisassembly(), gem5::ArmISA::SveComplexIdxOp::generateDisassembly(), gem5::ArmISA::SveComplexOp::generateDisassembly(), gem5::ArmISA::SveContigMemSI::generateDisassembly(), gem5::ArmISA::SveContigMemSS::generateDisassembly(), gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::generateDisassembly(), gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::generateDisassembly(), gem5::ArmISA::SveIntCmpImmOp::generateDisassembly(), gem5::ArmISA::SveIntCmpOp::generateDisassembly(), gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveMemPredFillSpill::generateDisassembly(), gem5::ArmISA::SveOrdReducOp::generateDisassembly(), gem5::ArmISA::SvePartBrkOp::generateDisassembly(), gem5::ArmISA::SvePartBrkPropOp::generateDisassembly(), gem5::ArmISA::SvePredBinPermOp::generateDisassembly(), gem5::ArmISA::SvePredCountOp::generateDisassembly(), gem5::ArmISA::SvePredCountPredOp::generateDisassembly(), gem5::ArmISA::SvePredLogicalOp::generateDisassembly(), gem5::ArmISA::SvePredTestOp::generateDisassembly(), gem5::ArmISA::SvePredUnaryWImplicitDstOp::generateDisassembly(), gem5::ArmISA::SvePredUnaryWImplicitSrcOp::generateDisassembly(), gem5::ArmISA::SvePredUnaryWImplicitSrcPredOp::generateDisassembly(), gem5::ArmISA::SvePselOp::generateDisassembly(), gem5::ArmISA::SvePtrueOp::generateDisassembly(), gem5::ArmISA::SveReducOp::generateDisassembly(), gem5::ArmISA::SveSelectOp::generateDisassembly(), gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveTerPredOp::generateDisassembly(), gem5::ArmISA::SveUnaryPredOp::generateDisassembly(), gem5::ArmISA::SveUnaryPredPredOp::generateDisassembly(), gem5::ArmISA::SveUnaryWideImmPredOp::generateDisassembly(), gem5::ArmISA::SveUnpackOp::generateDisassembly(), and gem5::ArmISA::SveWhileOp::generateDisassembly().

◆ printVecReg()

|

protected |

Definition at line 351 of file static_inst.cc.

References gem5::ccprintf(), and gem5::X86ISA::os.

Referenced by gem5::ArmISA::SmeAddOp::generateDisassembly(), gem5::ArmISA::SmeAddVlOp::generateDisassembly(), gem5::ArmISA::SmeMovExtractOp::generateDisassembly(), gem5::ArmISA::SmeMovInsertOp::generateDisassembly(), gem5::ArmISA::SmeOPOp::generateDisassembly(), gem5::ArmISA::SmeRdsvlOp::generateDisassembly(), gem5::ArmISA::SveAdrOp::generateDisassembly(), gem5::ArmISA::SveBinConstrPredOp::generateDisassembly(), gem5::ArmISA::SveBinDestrPredOp::generateDisassembly(), gem5::ArmISA::SveBinIdxUnpredOp::generateDisassembly(), gem5::ArmISA::SveBinImmIdxUnpredOp::generateDisassembly(), gem5::ArmISA::SveBinImmPredOp::generateDisassembly(), gem5::ArmISA::SveBinImmUnpredConstrOp::generateDisassembly(), gem5::ArmISA::SveBinImmUnpredDestrOp::generateDisassembly(), gem5::ArmISA::SveBinUnpredOp::generateDisassembly(), gem5::ArmISA::SveBinWideImmUnpredOp::generateDisassembly(), gem5::ArmISA::SveClampOp::generateDisassembly(), gem5::ArmISA::SveCmpImmOp::generateDisassembly(), gem5::ArmISA::SveCmpOp::generateDisassembly(), gem5::ArmISA::SveContigMemSI::generateDisassembly(), gem5::ArmISA::SveContigMemSS::generateDisassembly(), gem5::ArmISA::SveDotProdIdxOp::generateDisassembly(), gem5::ArmISA::SveDotProdOp::generateDisassembly(), gem5::ArmISA::SveElemCountOp::generateDisassembly(), gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::generateDisassembly(), gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::generateDisassembly(), gem5::ArmISA::SveIndexIIOp::generateDisassembly(), gem5::ArmISA::SveIndexIROp::generateDisassembly(), gem5::ArmISA::SveIndexRIOp::generateDisassembly(), gem5::ArmISA::SveIndexRROp::generateDisassembly(), gem5::ArmISA::SveIntCmpImmOp::generateDisassembly(), gem5::ArmISA::SveIntCmpOp::generateDisassembly(), gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >::generateDisassembly(), gem5::ArmISA::SveMemVecFillSpill::generateDisassembly(), gem5::ArmISA::SveOrdReducOp::generateDisassembly(), gem5::ArmISA::SvePredCountOp::generateDisassembly(), gem5::ArmISA::SvePredLogicalOp::generateDisassembly(), gem5::ArmISA::SveReducOp::generateDisassembly(), gem5::ArmISA::SveSelectOp::generateDisassembly(), gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >::generateDisassembly(), gem5::ArmISA::SveTblOp::generateDisassembly(), gem5::ArmISA::SveTerImmUnpredOp::generateDisassembly(), gem5::ArmISA::SveTerPredOp::generateDisassembly(), gem5::ArmISA::SveTerUnpredOp::generateDisassembly(), gem5::ArmISA::SveUnaryPredOp::generateDisassembly(), gem5::ArmISA::SveUnarySca2VecUnpredOp::generateDisassembly(), gem5::ArmISA::SveUnaryUnpredOp::generateDisassembly(), gem5::ArmISA::SveUnaryWideImmPredOp::generateDisassembly(), and gem5::ArmISA::SveUnaryWideImmUnpredOp::generateDisassembly().

◆ readPC()

|

inlinestaticprotected |

Definition at line 335 of file static_inst.hh.

References gem5::PCStateBase::as(), and gem5::ExecContext::pcState().

◆ satInt()

|

inlinestaticprotected |

Definition at line 104 of file static_inst.hh.

References gem5::X86ISA::op, and gem5::ArmISA::width.

◆ saturateOp()

|

inlinestaticprotected |

Definition at line 88 of file static_inst.hh.

References gem5::bits(), and gem5::ArmISA::width.

◆ setAIWNextPC()

|

inlinestaticprotected |

Definition at line 394 of file static_inst.hh.

References gem5::PCStateBase::as(), gem5::MipsISA::pc, gem5::ExecContext::pcState(), and gem5::X86ISA::val.

◆ setIWNextPC()

|

inlinestaticprotected |

Definition at line 384 of file static_inst.hh.

References gem5::PCStateBase::as(), gem5::MipsISA::pc, gem5::ExecContext::pcState(), and gem5::X86ISA::val.

◆ setNextPC()

|

inlinestaticprotected |

Definition at line 341 of file static_inst.hh.

References gem5::PCStateBase::as(), gem5::MipsISA::pc, gem5::ExecContext::pcState(), and gem5::X86ISA::val.

◆ shift_carry_imm()

|

protected |

Definition at line 220 of file static_inst.cc.

References gem5::RiscvISA::base, gem5::ccprintf(), and gem5::X86ISA::exit.

◆ shift_carry_rs()

|

protected |

Definition at line 260 of file static_inst.cc.

References gem5::RiscvISA::base, gem5::ccprintf(), and gem5::X86ISA::exit.

◆ shift_rm_imm()

|

protected |

Definition at line 60 of file static_inst.cc.

References gem5::RiscvISA::base, gem5::ccprintf(), and gem5::X86ISA::exit.

◆ shift_rm_rs()

|

protected |

Definition at line 180 of file static_inst.cc.

References gem5::RiscvISA::base, gem5::ccprintf(), and gem5::X86ISA::exit.

◆ shiftReg64()

|

protected |

Definition at line 95 of file static_inst.cc.

References gem5::RiscvISA::base, gem5::bits(), gem5::ccprintf(), gem5::X86ISA::exit, intWidth, gem5::ArmISA::mask, and gem5::ArmISA::width.

◆ smeAccessTrap()

|

protected |

Trap an access to SME registers due to access control bits.

- Parameters

-

el Target EL for the trap. iss ISS to be used for the trap.

Definition at line 1040 of file static_inst.cc.

References gem5::ArmISA::el, generateTrap(), gem5::ArmISA::iss, and gem5::ArmISA::TRAPPED_SME.

Referenced by checkSmeAccess(), and checkSmeEnabled().

◆ softwareBreakpoint32()

|

protected |

Trigger a Software Breakpoint.

See aarch32/exceptions/debug/AArch32.SoftwareBreakpoint in the ARM ARM psueodcode library.

Definition at line 635 of file static_inst.cc.

References gem5::ArmISA::imm, and gem5::ExecContext::tcBase().

◆ spsrWriteByInstr()

|

inlinestaticprotected |

Definition at line 317 of file static_inst.hh.

References gem5::bits(), gem5::ArmISA::mask, and gem5::X86ISA::val.

◆ sveAccessTrap()

|

protected |

Trap an access to SVE registers due to access control bits.

- Parameters

-

el Target EL for the trap.

Definition at line 977 of file static_inst.cc.

References gem5::ArmISA::el, generateTrap(), and gem5::ArmISA::TRAPPED_SVE.

Referenced by checkSveEnabled().

◆ trapWFx()

|

protected |

WFE/WFI trapping helper function.

Definition at line 877 of file static_inst.cc.

References checkForWFxTrap32(), gem5::ArmISA::currEL(), gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL2Enabled(), gem5::ArmISA::EL3, gem5::ArmSystem::haveEL(), and gem5::NoFault.

◆ undefined()

|

inline |

Definition at line 631 of file static_inst.hh.

References machInst, and gem5::StaticInst::mnemonic.

Referenced by gem5::ArmISA::MiscRegLUTEntry::defaultFault(), gem5::ArmISA::defaultFaultE2H_EL2(), gem5::ArmISA::defaultFaultE2H_EL3(), and disabledFault().

◆ undefinedFault32()

|

protected |

UNDEFINED behaviour in AArch32.

See aarch32/exceptions/traps/AArch32.UndefinedFault in the ARM ARM pseudocode library.

Definition at line 935 of file static_inst.cc.

References generalExceptionsToAArch64(), machInst, gem5::StaticInst::mnemonic, undefinedFault64(), and gem5::ArmISA::UNKNOWN.

Referenced by checkSETENDEnabled().

◆ undefinedFault64()

|

protected |

UNDEFINED behaviour in AArch64.

See aarch64/exceptions/traps/AArch64.UndefinedFault in the ARM ARM pseudocode library.

Definition at line 954 of file static_inst.cc.

References gem5::ArmISA::EL0, gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL3, machInst, gem5::NoFault, panic, and gem5::ArmISA::UNKNOWN.

Referenced by undefinedFault32().

◆ uSatInt()

|

inlinestaticprotected |

Definition at line 137 of file static_inst.hh.

References gem5::X86ISA::op, and gem5::ArmISA::width.

◆ uSaturateOp()

|

inlinestaticprotected |

Definition at line 121 of file static_inst.hh.

References gem5::ArmISA::width.

Member Data Documentation

◆ aarch64

|

protected |

Definition at line 68 of file static_inst.hh.

Referenced by ArmStaticInst(), printIntReg(), and printMnemonic().

◆ intWidth

|

protected |

Definition at line 69 of file static_inst.hh.

Referenced by ArmStaticInst(), getIntWidth(), printIntReg(), and shiftReg64().

◆ machInst

|

protected |

Definition at line 151 of file static_inst.hh.

Referenced by ArmStaticInst(), asBytes(), gem5::ArmISA::BigFpMemImmOp::BigFpMemImmOp(), gem5::ArmISA::BigFpMemLitOp::BigFpMemLitOp(), gem5::ArmISA::BigFpMemPostOp::BigFpMemPostOp(), gem5::ArmISA::BigFpMemPreOp::BigFpMemPreOp(), gem5::ArmISA::BigFpMemRegOp::BigFpMemRegOp(), gem5::ArmISA::BranchImmCond::BranchImmCond(), gem5::ArmISA::BranchRegCond::BranchRegCond(), checkAdvSIMDOrFPEnabled32(), checkForWFxTrap32(), gem5::ArmISAInst::MicroTcommit64::completeAcc(), gem5::ArmISAInst::Tcancel64::completeAcc(), gem5::ArmISAInst::Tstart64::completeAcc(), encoding(), gem5::ArmISAInst::Ttest64::execute(), gem5::DebugStep::execute(), gem5::DecoderFaultInst::execute(), gem5::FailUnimplemented::execute(), gem5::McrMrcImplDefined::execute(), gem5::McrMrcMiscInst::execute(), gem5::ArmISA::PredImmOp::generateDisassembly(), gem5::ArmISA::PredIntOp::generateDisassembly(), gem5::MiscRegOp64::generateTrap(), getEMI(), gem5::ArmISAInst::MicroTcommit64::initiateAcc(), gem5::ArmISAInst::Tcancel64::initiateAcc(), gem5::ArmISAInst::Tstart64::initiateAcc(), instSize(), gem5::ArmISA::MacroMemOp::MacroMemOp(), gem5::ArmISAInst::MacroTmeOp::MacroTmeOp(), gem5::ArmISA::MacroVFPMemOp::MacroVFPMemOp(), gem5::ArmISA::MicroIntImmOp::MicroIntImmOp(), gem5::ArmISA::MicroIntImmXOp::MicroIntImmXOp(), gem5::ArmISA::MicroIntMov::MicroIntMov(), gem5::ArmISA::MicroIntOp::MicroIntOp(), gem5::ArmISA::MicroIntRegOp::MicroIntRegOp(), gem5::ArmISA::MicroIntRegXOp::MicroIntRegXOp(), gem5::ArmISA::MicroMemOp::MicroMemOp(), gem5::ArmISA::MicroMemPairOp::MicroMemPairOp(), gem5::ArmISA::MicroNeonMemOp::MicroNeonMemOp(), gem5::ArmISA::MicroNeonMixLaneOp::MicroNeonMixLaneOp(), gem5::ArmISA::MicroNeonMixLaneOp64::MicroNeonMixLaneOp64(), gem5::ArmISA::MicroNeonMixOp::MicroNeonMixOp(), gem5::ArmISA::MicroNeonMixOp64::MicroNeonMixOp64(), gem5::ArmISA::MicroOp::MicroOp(), gem5::ArmISA::MicroOpX::MicroOpX(), gem5::ArmISA::MicroSetPCCPSR::MicroSetPCCPSR(), gem5::ArmISAInst::MicroTcommit64::MicroTcommit64(), gem5::ArmISAInst::MicroTfence64::MicroTfence64(), gem5::ArmISAInst::MicroTmeBasic64::MicroTmeBasic64(), gem5::ArmISAInst::MicroTmeOp::MicroTmeOp(), gem5::ArmISA::VfpMacroOp::nextIdxs(), gem5::ArmISA::VfpMacroOp::nextIdxs(), gem5::ArmISA::VfpMacroOp::nextIdxs(), gem5::ArmISA::PairMemOp::PairMemOp(), gem5::ArmISA::PredImmOp::PredImmOp(), gem5::ArmISA::PredIntOp::PredIntOp(), gem5::ArmISA::PredOp::PredOp(), printMnemonic(), gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::SveIndexedMemSV(), gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::SveIndexedMemVI(), gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >::SveLdStructSI(), gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >::SveLdStructSS(), gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >::SveStStructSI(), gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >::SveStStructSS(), gem5::ArmISAInst::Tcancel64::Tcancel64(), gem5::ArmISAInst::Tcommit64::Tcommit64(), gem5::ArmISAInst::TmeImmOp64::TmeImmOp64(), gem5::ArmISAInst::TmeRegNone64::TmeRegNone64(), gem5::ArmISAInst::Tstart64::Tstart64(), gem5::ArmISAInst::Ttest64::Ttest64(), undefined(), undefinedFault32(), undefinedFault64(), gem5::ArmISA::VldMultOp::VldMultOp(), gem5::ArmISA::VldMultOp64::VldMultOp64(), gem5::ArmISA::VldSingleOp::VldSingleOp(), gem5::ArmISA::VldSingleOp64::VldSingleOp64(), gem5::ArmISA::VstMultOp::VstMultOp(), gem5::ArmISA::VstMultOp64::VstMultOp64(), gem5::ArmISA::VstSingleOp::VstSingleOp(), and gem5::ArmISA::VstSingleOp64::VstSingleOp64().

The documentation for this class was generated from the following files:

- arch/arm/insts/static_inst.hh

- arch/arm/insts/static_inst.cc

Generated on Sat Oct 18 2025 08:06:56 for gem5 by doxygen 1.14.0