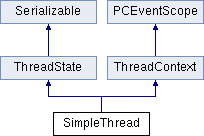

The SimpleThread object provides a combination of the ThreadState object and the ThreadContext interface. More...

#include <simple_thread.hh>

Public Types | |

| typedef ThreadContext::Status | Status |

Public Types inherited from ThreadState Public Types inherited from ThreadState | |

| typedef ThreadContext::Status | Status |

Public Types inherited from ThreadContext Public Types inherited from ThreadContext | |

| enum | Status { Active, Suspended, Halting, Halted } |

Public Member Functions | |

| std::string | name () const |

| SimpleThread (BaseCPU *_cpu, int _thread_num, System *_system, BaseTLB *_itb, BaseTLB *_dtb, BaseISA *_isa) | |

| SimpleThread (BaseCPU *_cpu, int _thread_num, System *_system, Process *_process, BaseTLB *_itb, BaseTLB *_dtb, BaseISA *_isa) | |

| virtual | ~SimpleThread () |

| void | takeOverFrom (ThreadContext *oldContext) override |

| void | copyState (ThreadContext *oldContext) |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

| ThreadContext * | getTC () |

| Returns the pointer to this SimpleThread's ThreadContext. More... | |

| void | demapPage (Addr vaddr, uint64_t asn) |

| void | demapInstPage (Addr vaddr, uint64_t asn) |

| void | demapDataPage (Addr vaddr, uint64_t asn) |

| bool | schedule (PCEvent *e) override |

| bool | remove (PCEvent *e) override |

| void | scheduleInstCountEvent (Event *event, Tick count) override |

| void | descheduleInstCountEvent (Event *event) override |

| Tick | getCurrentInstCount () override |

| BaseCPU * | getCpuPtr () override |

| int | cpuId () const override |

| uint32_t | socketId () const override |

| int | threadId () const override |

| void | setThreadId (int id) override |

| ContextID | contextId () const override |

| void | setContextId (ContextID id) override |

| BaseTLB * | getITBPtr () override |

| BaseTLB * | getDTBPtr () override |

| CheckerCPU * | getCheckerCpuPtr () override |

| BaseISA * | getIsaPtr () override |

| TheISA::Decoder * | getDecoderPtr () override |

| System * | getSystemPtr () override |

| PortProxy & | getPhysProxy () override |

| PortProxy & | getVirtProxy () override |

| void | initMemProxies (ThreadContext *tc) override |

| Initialise the physical and virtual port proxies and tie them to the data port of the CPU. More... | |

| Process * | getProcessPtr () override |

| void | setProcessPtr (Process *p) override |

| Status | status () const override |

| void | setStatus (Status newStatus) override |

| void | activate () override |

| Set the status to Active. More... | |

| void | suspend () override |

| Set the status to Suspended. More... | |

| void | halt () override |

| Set the status to Halted. More... | |

| Tick | readLastActivate () override |

| Tick | readLastSuspend () override |

| void | copyArchRegs (ThreadContext *tc) override |

| void | clearArchRegs () override |

| RegVal | readIntReg (RegIndex reg_idx) const override |

| RegVal | readFloatReg (RegIndex reg_idx) const override |

| const VecRegContainer & | readVecReg (const RegId ®) const override |

| VecRegContainer & | getWritableVecReg (const RegId ®) override |

| const VecElem & | readVecElem (const RegId ®) const override |

| const VecPredRegContainer & | readVecPredReg (const RegId ®) const override |

| VecPredRegContainer & | getWritableVecPredReg (const RegId ®) override |

| RegVal | readCCReg (RegIndex reg_idx) const override |

| void | setIntReg (RegIndex reg_idx, RegVal val) override |

| void | setFloatReg (RegIndex reg_idx, RegVal val) override |

| void | setVecReg (const RegId ®, const VecRegContainer &val) override |

| void | setVecElem (const RegId ®, const VecElem &val) override |

| void | setVecPredReg (const RegId ®, const VecPredRegContainer &val) override |

| void | setCCReg (RegIndex reg_idx, RegVal val) override |

| TheISA::PCState | pcState () const override |

| void | pcState (const TheISA::PCState &val) override |

| void | pcStateNoRecord (const TheISA::PCState &val) override |

| Addr | instAddr () const override |

| Addr | nextInstAddr () const override |

| MicroPC | microPC () const override |

| bool | readPredicate () const |

| void | setPredicate (bool val) |

| RegVal | readMiscRegNoEffect (RegIndex misc_reg) const override |

| RegVal | readMiscReg (RegIndex misc_reg) override |

| void | setMiscRegNoEffect (RegIndex misc_reg, RegVal val) override |

| void | setMiscReg (RegIndex misc_reg, RegVal val) override |

| RegId | flattenRegId (const RegId ®Id) const override |

| unsigned | readStCondFailures () const override |

| bool | readMemAccPredicate () |

| void | setMemAccPredicate (bool val) |

| void | setStCondFailures (unsigned sc_failures) override |

| Counter | readFuncExeInst () const override |

| void | syscall () override |

| RegVal | readIntRegFlat (RegIndex idx) const override |

| Flat register interfaces. More... | |

| void | setIntRegFlat (RegIndex idx, RegVal val) override |

| RegVal | readFloatRegFlat (RegIndex idx) const override |

| void | setFloatRegFlat (RegIndex idx, RegVal val) override |

| const VecRegContainer & | readVecRegFlat (RegIndex reg) const override |

| VecRegContainer & | getWritableVecRegFlat (RegIndex reg) override |

| void | setVecRegFlat (RegIndex reg, const VecRegContainer &val) override |

| template<typename T > | |

| VecLaneT< T, true > | readVecLaneFlat (RegIndex reg, int lId) const |

| template<typename LD > | |

| void | setVecLaneFlat (RegIndex reg, int lId, const LD &val) |

| const VecElem & | readVecElemFlat (RegIndex reg, const ElemIndex &elemIndex) const override |

| void | setVecElemFlat (RegIndex reg, const ElemIndex &elemIndex, const VecElem &val) override |

| const VecPredRegContainer & | readVecPredRegFlat (RegIndex reg) const override |

| VecPredRegContainer & | getWritableVecPredRegFlat (RegIndex reg) override |

| void | setVecPredRegFlat (RegIndex reg, const VecPredRegContainer &val) override |

| RegVal | readCCRegFlat (RegIndex idx) const override |

| void | setCCRegFlat (RegIndex idx, RegVal val) override |

| void | htmAbortTransaction (uint64_t htm_uid, HtmFailureFaultCause cause) override |

| BaseHTMCheckpointPtr & | getHtmCheckpointPtr () override |

| void | setHtmCheckpointPtr (BaseHTMCheckpointPtr new_cpt) override |

| template<typename T > | |

| VecLaneT< T, true > | readVecLane (const RegId ®) const |

| Vector Register Lane Interfaces. More... | |

| virtual ConstVecLane8 | readVec8BitLaneReg (const RegId ®) const override |

| Reads source vector 8bit operand. More... | |

| virtual ConstVecLane16 | readVec16BitLaneReg (const RegId ®) const override |

| Reads source vector 16bit operand. More... | |

| virtual ConstVecLane32 | readVec32BitLaneReg (const RegId ®) const override |

| Reads source vector 32bit operand. More... | |

| virtual ConstVecLane64 | readVec64BitLaneReg (const RegId ®) const override |

| Reads source vector 64bit operand. More... | |

| template<typename LD > | |

| void | setVecLaneT (const RegId ®, const LD &val) |

| Write a lane of the destination vector register. More... | |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::Byte > &val) override |

| Write a lane of the destination vector register. More... | |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::TwoByte > &val) override |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::FourByte > &val) override |

| virtual void | setVecLane (const RegId ®, const LaneData< LaneSize::EightByte > &val) override |

Public Member Functions inherited from ThreadState Public Member Functions inherited from ThreadState | |

| ThreadState (BaseCPU *cpu, ThreadID _tid, Process *_process) | |

| virtual | ~ThreadState () |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

| int | cpuId () const |

| uint32_t | socketId () const |

| ContextID | contextId () const |

| void | setContextId (ContextID id) |

| void | setThreadId (ThreadID id) |

| ThreadID | threadId () const |

| Tick | readLastActivate () const |

| Tick | readLastSuspend () const |

| void | initMemProxies (ThreadContext *tc) |

| Initialise the physical and virtual port proxies and tie them to the data port of the CPU. More... | |

| PortProxy & | getPhysProxy () |

| PortProxy & | getVirtProxy () |

| Process * | getProcessPtr () |

| void | setProcessPtr (Process *p) |

| Counter | readFuncExeInst () const |

| Reads the number of instructions functionally executed and committed. More... | |

| void | setFuncExeInst (Counter new_val) |

| Sets the total number of instructions functionally executed and committed. More... | |

| Status | status () const |

| Returns the status of this thread. More... | |

| void | setStatus (Status new_status) |

| Sets the status of this thread. More... | |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from ThreadContext Public Member Functions inherited from ThreadContext | |

| virtual | ~ThreadContext () |

| void | quiesce () |

| Quiesce thread context. More... | |

| void | quiesceTick (Tick resume) |

| Quiesce, suspend, and schedule activate at resume. More... | |

| virtual void | regStats (const std::string &name) |

| void | setNPC (Addr val) |

| virtual int | exit () |

Public Attributes | |

| PCEventQueue | pcEventQueue |

| EventQueue | comInstEventQueue |

| An instruction-based event queue. More... | |

| System * | system |

| BaseTLB * | itb |

| BaseTLB * | dtb |

| TheISA::Decoder | decoder |

| int64_t | htmTransactionStarts |

| int64_t | htmTransactionStops |

Public Attributes inherited from ThreadState Public Attributes inherited from ThreadState | |

| Counter | numInst |

| Number of instructions committed. More... | |

| Counter | numOp |

| Number of ops (including micro ops) committed. More... | |

| ThreadState::ThreadStateStats | threadStats |

| Counter | numLoad |

| Number of simulated loads, used for tracking events based on the number of loads committed. More... | |

| Counter | startNumLoad |

| The number of simulated loads committed prior to this run. More... | |

| Tick | lastActivate |

| Last time activate was called on this thread. More... | |

| Tick | lastSuspend |

| Last time suspend was called on this thread. More... | |

| Counter | funcExeInst |

| unsigned | storeCondFailures |

Public Attributes inherited from ThreadContext Public Attributes inherited from ThreadContext | |

| int | intResult = DefaultIntResult |

| double | floatResult = DefaultFloatResult |

| int | intOffset = 0 |

Protected Types | |

| typedef TheISA::MachInst | MachInst |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | VecElem = TheISA::VecElem |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

Protected Types inherited from ThreadContext Protected Types inherited from ThreadContext | |

| typedef TheISA::MachInst | MachInst |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | VecElem = TheISA::VecElem |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

Protected Attributes | |

| std::array< RegVal, TheISA::NumFloatRegs > | floatRegs |

| std::array< RegVal, TheISA::NumIntRegs > | intRegs |

| std::array< VecRegContainer, TheISA::NumVecRegs > | vecRegs |

| std::array< VecPredRegContainer, TheISA::NumVecPredRegs > | vecPredRegs |

| std::array< RegVal, TheISA::NumCCRegs > | ccRegs |

| TheISA::ISA *const | isa |

| TheISA::PCState | _pcState |

| std::unique_ptr< BaseHTMCheckpoint > | _htmCheckpoint |

| bool | predicate |

| Did this instruction execute or is it predicated false. More... | |

| bool | memAccPredicate |

| True if the memory access should be skipped for this instruction. More... | |

Protected Attributes inherited from ThreadState Protected Attributes inherited from ThreadState | |

| ThreadContext::Status | _status |

| BaseCPU * | baseCpu |

| ContextID | _contextId |

| ThreadID | _threadId |

| Process * | process |

| PortProxy * | physProxy |

| A port proxy outgoing only for functional accesses to physical addresses. More... | |

| PortProxy * | virtProxy |

| A translating port proxy, outgoing only, for functional accesse to virtual addresses. More... | |

Additional Inherited Members | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| Serializes all the SimObjects. More... | |

| static void | unserializeGlobals (CheckpointIn &cp) |

Static Public Member Functions inherited from ThreadContext Static Public Member Functions inherited from ThreadContext | |

| static void | compare (ThreadContext *one, ThreadContext *two) |

| function to compare two thread contexts (for debugging) More... | |

Static Public Attributes inherited from ThreadContext Static Public Attributes inherited from ThreadContext | |

| static const int | ints [] |

| static const double | floats [] |

| static const int | DefaultIntResult = 0 |

| static const double | DefaultFloatResult = 0.0 |

Detailed Description

The SimpleThread object provides a combination of the ThreadState object and the ThreadContext interface.

It implements the ThreadContext interface and adds to the ThreadState object by adding all the objects needed for simple functional execution, including a simple architectural register file, and pointers to the ITB and DTB in full system mode. For CPU models that do not need more advanced ways to hold state (i.e. a separate physical register file, or separate fetch and commit PC's), this SimpleThread class provides all the necessary state for full architecture-level functional simulation. See the AtomicSimpleCPU or TimingSimpleCPU for examples.

Definition at line 89 of file simple_thread.hh.

Member Typedef Documentation

◆ MachInst

|

protected |

Definition at line 92 of file simple_thread.hh.

◆ Status

Definition at line 97 of file simple_thread.hh.

◆ VecElem

|

protected |

Definition at line 94 of file simple_thread.hh.

◆ VecPredRegContainer

|

protected |

Definition at line 95 of file simple_thread.hh.

◆ VecRegContainer

|

protected |

Definition at line 93 of file simple_thread.hh.

Constructor & Destructor Documentation

◆ SimpleThread() [1/2]

| SimpleThread::SimpleThread | ( | BaseCPU * | _cpu, |

| int | _thread_num, | ||

| System * | _system, | ||

| BaseTLB * | _itb, | ||

| BaseTLB * | _dtb, | ||

| BaseISA * | _isa | ||

| ) |

Definition at line 82 of file simple_thread.cc.

References clearArchRegs(), and isa.

◆ SimpleThread() [2/2]

| SimpleThread::SimpleThread | ( | BaseCPU * | _cpu, |

| int | _thread_num, | ||

| System * | _system, | ||

| Process * | _process, | ||

| BaseTLB * | _itb, | ||

| BaseTLB * | _dtb, | ||

| BaseISA * | _isa | ||

| ) |

Definition at line 68 of file simple_thread.cc.

References clearArchRegs(), and isa.

◆ ~SimpleThread()

|

inlinevirtual |

Definition at line 151 of file simple_thread.hh.

Member Function Documentation

◆ activate()

|

overridevirtual |

Set the status to Active.

Implements ThreadContext.

Definition at line 137 of file simple_thread.cc.

References ThreadState::_status, ThreadState::_threadId, BaseCPU::activateContext(), ThreadContext::Active, ThreadState::baseCpu, curTick(), ThreadState::lastActivate, and status().

Referenced by BaseKvmCPU::wakeup().

◆ clearArchRegs()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 269 of file simple_thread.hh.

References _pcState, ccRegs, floatRegs, intRegs, isa, vecPredRegs, and vecRegs.

Referenced by CheckerThreadContext< TC >::clearArchRegs(), and SimpleThread().

◆ contextId()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 216 of file simple_thread.hh.

References ThreadState::contextId().

Referenced by Minor::ExecContext::contextId(), TimingSimpleCPU::fetch(), TimingSimpleCPU::htmSendAbortSignal(), TimingSimpleCPU::initiateHtmCmd(), TimingSimpleCPU::initiateMemAMO(), TimingSimpleCPU::initiateMemRead(), and TimingSimpleCPU::writeMem().

◆ copyArchRegs()

|

overridevirtual |

Implements ThreadContext.

Definition at line 171 of file simple_thread.cc.

References ArmISA::copyRegs().

Referenced by CheckerThreadContext< TC >::copyArchRegs(), and copyState().

◆ copyState()

| void SimpleThread::copyState | ( | ThreadContext * | oldContext | ) |

Definition at line 109 of file simple_thread.cc.

References ThreadState::_contextId, ThreadState::_status, ThreadState::_threadId, ThreadContext::contextId(), copyArchRegs(), FullSystem, ThreadState::funcExeInst, ThreadContext::readFuncExeInst(), ThreadContext::status(), and ThreadContext::threadId().

Referenced by CheckerThreadContext< TC >::takeOverFrom().

◆ cpuId()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 212 of file simple_thread.hh.

References ThreadState::cpuId().

◆ demapDataPage()

|

inline |

Definition at line 182 of file simple_thread.hh.

References BaseTLB::demapPage(), dtb, and MipsISA::vaddr.

◆ demapInstPage()

|

inline |

Definition at line 177 of file simple_thread.hh.

References BaseTLB::demapPage(), itb, and MipsISA::vaddr.

◆ demapPage()

|

inline |

Definition at line 171 of file simple_thread.hh.

References BaseTLB::demapPage(), dtb, itb, and MipsISA::vaddr.

Referenced by SimpleExecContext::demapPage().

◆ descheduleInstCountEvent()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 200 of file simple_thread.hh.

References comInstEventQueue, EventQueue::deschedule(), and MipsISA::event.

◆ flattenRegId()

◆ getCheckerCpuPtr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 223 of file simple_thread.hh.

◆ getCpuPtr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 210 of file simple_thread.hh.

References ThreadState::baseCpu.

◆ getCurrentInstCount()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 205 of file simple_thread.hh.

References comInstEventQueue, and EventQueue::getCurTick().

◆ getDecoderPtr()

|

inlineoverridevirtual |

◆ getDTBPtr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 221 of file simple_thread.hh.

References dtb.

Referenced by Minor::ExecContext::demapDataPage(), and Minor::ExecContext::demapPage().

◆ getHtmCheckpointPtr()

|

overridevirtual |

Implements ThreadContext.

Definition at line 191 of file simple_thread.cc.

References _htmCheckpoint.

◆ getIsaPtr()

|

inlineoverridevirtual |

◆ getITBPtr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 219 of file simple_thread.hh.

References itb.

Referenced by Minor::ExecContext::demapInstPage(), and Minor::ExecContext::demapPage().

◆ getPhysProxy()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 231 of file simple_thread.hh.

References ThreadState::getPhysProxy().

◆ getProcessPtr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 239 of file simple_thread.hh.

References ThreadState::getProcessPtr().

◆ getSystemPtr()

|

inlineoverridevirtual |

◆ getTC()

|

inline |

Returns the pointer to this SimpleThread's ThreadContext.

Used when a ThreadContext must be passed to objects outside of the CPU.

Definition at line 169 of file simple_thread.hh.

Referenced by AtomicSimpleCPU::amoMem(), BaseSimpleCPU::BaseSimpleCPU(), BaseSimpleCPU::checkForInterrupts(), BaseKvmCPU::doMMIOAccess(), TimingSimpleCPU::fetch(), TimingSimpleCPU::handleReadPacket(), TimingSimpleCPU::handleWritePacket(), TimingSimpleCPU::initiateMemAMO(), TimingSimpleCPU::initiateMemRead(), MinorCPU::MinorCPU(), BaseSimpleCPU::preExecute(), AtomicSimpleCPU::readMem(), CheckerCPU::setSystem(), Minor::ExecContext::tcBase(), SimpleExecContext::tcBase(), AtomicSimpleCPU::tick(), AtomicSimpleCPU::writeMem(), and TimingSimpleCPU::writeMem().

◆ getVirtProxy()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 232 of file simple_thread.hh.

References ThreadState::getVirtProxy().

◆ getWritableVecPredReg()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 431 of file simple_thread.hh.

References DPRINTF, getWritableVecPredRegFlat(), isa, ArmISA::NumVecPredRegs, VecPredRegContainer< NumBits, Packed >::print(), and X86ISA::reg.

Referenced by Minor::ExecContext::getWritableVecPredRegOperand(), CheckerCPU::getWritableVecPredRegOperand(), and SimpleExecContext::getWritableVecPredRegOperand().

◆ getWritableVecPredRegFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 660 of file simple_thread.hh.

References X86ISA::reg, and vecPredRegs.

Referenced by getWritableVecPredReg().

◆ getWritableVecReg()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 319 of file simple_thread.hh.

References DPRINTF, getWritableVecRegFlat(), isa, ArmISA::NumVecRegs, VecRegContainer< SIZE >::print(), and X86ISA::reg.

Referenced by Minor::ExecContext::getWritableVecRegOperand(), CheckerCPU::getWritableVecRegOperand(), and SimpleExecContext::getWritableVecRegOperand().

◆ getWritableVecRegFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 615 of file simple_thread.hh.

References X86ISA::reg, and vecRegs.

Referenced by getWritableVecReg().

◆ halt()

|

overridevirtual |

Set the status to Halted.

Implements ThreadContext.

Definition at line 161 of file simple_thread.cc.

References ThreadState::_status, ThreadState::_threadId, ThreadState::baseCpu, BaseCPU::haltContext(), ThreadContext::Halted, and status().

◆ htmAbortTransaction()

|

overridevirtual |

Implements ThreadContext.

Definition at line 178 of file simple_thread.cc.

References ThreadState::baseCpu, BaseSimpleCPU::htmSendAbortSignal(), htmTransactionStarts, and htmTransactionStops.

◆ initMemProxies()

|

inlineoverridevirtual |

Initialise the physical and virtual port proxies and tie them to the data port of the CPU.

tc ThreadContext for the virtual-to-physical translation

Implements ThreadContext.

Definition at line 234 of file simple_thread.hh.

References ThreadState::initMemProxies().

◆ instAddr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 526 of file simple_thread.hh.

References _pcState.

Referenced by TimingSimpleCPU::htmSendAbortSignal(), TimingSimpleCPU::initiateHtmCmd(), TimingSimpleCPU::initiateMemAMO(), TimingSimpleCPU::initiateMemRead(), CheckerCPU::instAddr(), BaseSimpleCPU::setupFetchRequest(), and TimingSimpleCPU::writeMem().

◆ microPC()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 528 of file simple_thread.hh.

References _pcState.

Referenced by AtomicSimpleCPU::isCpuDrained(), TimingSimpleCPU::isCpuDrained(), and CheckerCPU::microPC().

◆ name()

|

inline |

Definition at line 119 of file simple_thread.hh.

References ThreadState::baseCpu, csprintf(), and threadId().

◆ nextInstAddr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 527 of file simple_thread.hh.

References _pcState.

Referenced by CheckerCPU::nextInstAddr().

◆ pcState() [1/2]

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 517 of file simple_thread.hh.

References _pcState.

Referenced by BaseSimpleCPU::advancePC(), AtomicSimpleCPU::amoMem(), Minor::LSQ::LSQRequest::completeDisabledMemAccess(), CheckerCPU::dumpAndExit(), TimingSimpleCPU::fetch(), CheckerCPU::genMemFragmentRequest(), Minor::ExecContext::pcState(), CheckerThreadContext< TC >::pcState(), SimpleExecContext::pcState(), CheckerCPU::pcState(), BaseSimpleCPU::preExecute(), SimPoint::profile(), AtomicSimpleCPU::tick(), Minor::LSQ::tryToSendToTransfers(), and Minor::LSQ::LSQRequest::tryToSuppressFault().

◆ pcState() [2/2]

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 518 of file simple_thread.hh.

References _pcState, and X86ISA::val.

◆ pcStateNoRecord()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 521 of file simple_thread.hh.

References _pcState, and X86ISA::val.

◆ readCCReg()

Implements ThreadContext.

Definition at line 443 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumCCRegs, and readCCRegFlat().

Referenced by CheckerCPU::readCCRegOperand(), SimpleExecContext::readCCRegOperand(), and Minor::ExecContext::readCCRegOperand().

◆ readCCRegFlat()

Implements ThreadContext.

Definition at line 671 of file simple_thread.hh.

References ccRegs.

Referenced by readCCReg().

◆ readFloatReg()

Implements ThreadContext.

Definition at line 297 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumFloatRegs, and readFloatRegFlat().

Referenced by Minor::ExecContext::readFloatRegOperandBits(), SimpleExecContext::readFloatRegOperandBits(), and CheckerCPU::readFloatRegOperandBits().

◆ readFloatRegFlat()

Implements ThreadContext.

Definition at line 598 of file simple_thread.hh.

References floatRegs.

Referenced by readFloatReg().

◆ readFuncExeInst()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 583 of file simple_thread.hh.

References ThreadState::readFuncExeInst().

◆ readIntReg()

Implements ThreadContext.

Definition at line 286 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumIntRegs, and readIntRegFlat().

Referenced by Minor::ExecContext::readIntRegOperand(), SimpleExecContext::readIntRegOperand(), and CheckerCPU::readIntRegOperand().

◆ readIntRegFlat()

Flat register interfaces.

Some architectures have different registers visible in different modes. Such architectures "flatten" a register (see flattenRegId()) to map it into the gem5 register file. This interface provides a flat interface to the underlying register file, which allows for example serialization code to access all registers.

Implements ThreadContext.

Definition at line 590 of file simple_thread.hh.

References intRegs.

Referenced by readIntReg().

◆ readLastActivate()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 256 of file simple_thread.hh.

References ThreadState::readLastActivate().

◆ readLastSuspend()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 261 of file simple_thread.hh.

References ThreadState::readLastSuspend().

◆ readMemAccPredicate()

|

inline |

Definition at line 565 of file simple_thread.hh.

References memAccPredicate.

Referenced by Minor::ExecContext::readMemAccPredicate(), CheckerCPU::readMemAccPredicate(), and SimpleExecContext::readMemAccPredicate().

◆ readMiscReg()

Implements ThreadContext.

Definition at line 539 of file simple_thread.hh.

References isa.

Referenced by Minor::ExecContext::readMiscReg(), SimpleExecContext::readMiscReg(), CheckerCPU::readMiscReg(), SimpleExecContext::readMiscRegOperand(), Minor::ExecContext::readMiscRegOperand(), and CheckerCPU::readMiscRegOperand().

◆ readMiscRegNoEffect()

Implements ThreadContext.

Definition at line 533 of file simple_thread.hh.

References isa.

Referenced by Minor::ExecContext::readMiscRegNoEffect(), and CheckerCPU::readMiscRegNoEffect().

◆ readPredicate()

|

inline |

Definition at line 529 of file simple_thread.hh.

References predicate.

Referenced by Minor::ExecContext::readPredicate(), CheckerCPU::readPredicate(), and SimpleExecContext::readPredicate().

◆ readStCondFailures()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 562 of file simple_thread.hh.

References ThreadState::storeCondFailures.

Referenced by SimpleExecContext::readStCondFailures(), and CheckerCPU::readStCondFailures().

◆ readVec16BitLaneReg()

|

inlineoverridevirtual |

Reads source vector 16bit operand.

Implements ThreadContext.

Definition at line 353 of file simple_thread.hh.

References X86ISA::reg.

Referenced by CheckerCPU::readVec16BitLaneOperand(), and Minor::ExecContext::readVec16BitLaneOperand().

◆ readVec32BitLaneReg()

|

inlineoverridevirtual |

Reads source vector 32bit operand.

Implements ThreadContext.

Definition at line 360 of file simple_thread.hh.

References X86ISA::reg.

Referenced by CheckerCPU::readVec32BitLaneOperand(), and Minor::ExecContext::readVec32BitLaneOperand().

◆ readVec64BitLaneReg()

|

inlineoverridevirtual |

Reads source vector 64bit operand.

Implements ThreadContext.

Definition at line 367 of file simple_thread.hh.

References X86ISA::reg.

Referenced by CheckerCPU::readVec64BitLaneOperand(), and Minor::ExecContext::readVec64BitLaneOperand().

◆ readVec8BitLaneReg()

|

inlineoverridevirtual |

Reads source vector 8bit operand.

Implements ThreadContext.

Definition at line 346 of file simple_thread.hh.

References X86ISA::reg.

Referenced by CheckerCPU::readVec8BitLaneOperand(), and Minor::ExecContext::readVec8BitLaneOperand().

◆ readVecElem()

Implements ThreadContext.

Definition at line 409 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecRegs, readVecElemFlat(), and X86ISA::reg.

Referenced by Minor::ExecContext::readVecElemOperand(), CheckerCPU::readVecElemOperand(), and SimpleExecContext::readVecElemOperand().

◆ readVecElemFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 641 of file simple_thread.hh.

References X86ISA::reg, and vecRegs.

Referenced by readVecElem().

◆ readVecLane()

Vector Register Lane Interfaces.

Reads source vector <T> operand.

Definition at line 334 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecRegs, and X86ISA::reg.

Referenced by SimpleExecContext::readVecLaneOperand().

◆ readVecLaneFlat()

|

inline |

Definition at line 628 of file simple_thread.hh.

References X86ISA::reg, and vecRegs.

◆ readVecPredReg()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 420 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecPredRegs, VecPredRegContainer< NumBits, Packed >::print(), readVecPredRegFlat(), and X86ISA::reg.

Referenced by Minor::ExecContext::readVecPredRegOperand(), CheckerCPU::readVecPredRegOperand(), and SimpleExecContext::readVecPredRegOperand().

◆ readVecPredRegFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 654 of file simple_thread.hh.

References X86ISA::reg, and vecPredRegs.

Referenced by readVecPredReg().

◆ readVecReg()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 308 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecRegs, VecRegContainer< SIZE >::print(), readVecRegFlat(), and X86ISA::reg.

Referenced by Minor::ExecContext::readVecRegOperand(), CheckerCPU::readVecRegOperand(), and SimpleExecContext::readVecRegOperand().

◆ readVecRegFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 609 of file simple_thread.hh.

References X86ISA::reg, and vecRegs.

Referenced by readVecReg().

◆ remove()

|

inlineoverridevirtual |

Implements PCEventScope.

Definition at line 192 of file simple_thread.hh.

References ArmISA::e, pcEventQueue, and PCEventQueue::remove().

◆ schedule()

|

inlineoverridevirtual |

Implements PCEventScope.

Definition at line 191 of file simple_thread.hh.

References ArmISA::e, pcEventQueue, and PCEventQueue::schedule().

◆ scheduleInstCountEvent()

Implements ThreadContext.

Definition at line 195 of file simple_thread.hh.

References comInstEventQueue, X86ISA::count, MipsISA::event, and EventQueue::schedule().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements Serializable.

Definition at line 122 of file simple_thread.cc.

References ThreadState::serialize().

Referenced by BaseKvmCPU::serializeThread().

◆ setCCReg()

Implements ThreadContext.

Definition at line 508 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumCCRegs, setCCRegFlat(), and X86ISA::val.

Referenced by CheckerThreadContext< TC >::setCCReg(), SimpleExecContext::setCCRegOperand(), CheckerCPU::setCCRegOperand(), and Minor::ExecContext::setCCRegOperand().

◆ setCCRegFlat()

Implements ThreadContext.

Definition at line 672 of file simple_thread.hh.

References ccRegs, and X86ISA::val.

Referenced by setCCReg().

◆ setContextId()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 217 of file simple_thread.hh.

References ThreadState::setContextId().

Referenced by CheckerThreadContext< TC >::setContextId().

◆ setFloatReg()

Implements ThreadContext.

Definition at line 465 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumFloatRegs, setFloatRegFlat(), and X86ISA::val.

Referenced by CheckerThreadContext< TC >::setFloatReg(), SimpleExecContext::setFloatRegOperandBits(), Minor::ExecContext::setFloatRegOperandBits(), and CheckerCPU::setFloatRegOperandBits().

◆ setFloatRegFlat()

Implements ThreadContext.

Definition at line 603 of file simple_thread.hh.

References floatRegs, and X86ISA::val.

Referenced by setFloatReg().

◆ setHtmCheckpointPtr()

|

overridevirtual |

Implements ThreadContext.

Definition at line 197 of file simple_thread.cc.

References _htmCheckpoint.

◆ setIntReg()

Implements ThreadContext.

Definition at line 455 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumIntRegs, setIntRegFlat(), and X86ISA::val.

Referenced by Minor::ExecContext::ExecContext(), BaseSimpleCPU::preExecute(), CheckerThreadContext< TC >::setIntReg(), SimpleExecContext::setIntRegOperand(), Minor::ExecContext::setIntRegOperand(), and CheckerCPU::setIntRegOperand().

◆ setIntRegFlat()

Implements ThreadContext.

Definition at line 592 of file simple_thread.hh.

References intRegs, and X86ISA::val.

Referenced by setIntReg().

◆ setMemAccPredicate()

|

inline |

Definition at line 571 of file simple_thread.hh.

References memAccPredicate, and X86ISA::val.

Referenced by Minor::ExecContext::setMemAccPredicate(), CheckerCPU::setMemAccPredicate(), and SimpleExecContext::setMemAccPredicate().

◆ setMiscReg()

Implements ThreadContext.

Definition at line 551 of file simple_thread.hh.

References isa, and X86ISA::val.

Referenced by Minor::ExecContext::setMiscReg(), SimpleExecContext::setMiscReg(), CheckerThreadContext< TC >::setMiscReg(), CheckerCPU::setMiscReg(), SimpleExecContext::setMiscRegOperand(), and Minor::ExecContext::setMiscRegOperand().

◆ setMiscRegNoEffect()

Implements ThreadContext.

Definition at line 545 of file simple_thread.hh.

References isa, and X86ISA::val.

Referenced by CheckerThreadContext< TC >::setMiscRegNoEffect(), and CheckerCPU::setMiscRegNoEffect().

◆ setPredicate()

|

inline |

Definition at line 530 of file simple_thread.hh.

References predicate, and X86ISA::val.

Referenced by Minor::ExecContext::setPredicate(), CheckerCPU::setPredicate(), and SimpleExecContext::setPredicate().

◆ setProcessPtr()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 240 of file simple_thread.hh.

References MipsISA::p, and ThreadState::setProcessPtr().

◆ setStatus()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 244 of file simple_thread.hh.

References ThreadState::_status.

Referenced by MinorCPU::MinorCPU(), and CheckerThreadContext< TC >::setStatus().

◆ setStCondFailures()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 577 of file simple_thread.hh.

References ThreadState::storeCondFailures.

Referenced by SimpleExecContext::setStCondFailures().

◆ setThreadId()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 215 of file simple_thread.hh.

References ThreadState::setThreadId().

Referenced by CheckerThreadContext< TC >::setThreadId().

◆ setVecElem()

Implements ThreadContext.

Definition at line 488 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecRegs, X86ISA::reg, setVecElemFlat(), and X86ISA::val.

Referenced by CheckerThreadContext< TC >::setVecElem(), Minor::ExecContext::setVecElemOperand(), SimpleExecContext::setVecElemOperand(), and CheckerCPU::setVecElemOperand().

◆ setVecElemFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 647 of file simple_thread.hh.

References X86ISA::reg, X86ISA::val, and vecRegs.

Referenced by setVecElem().

◆ setVecLane() [1/4]

|

inlineoverridevirtual |

Write a lane of the destination vector register.

Implements ThreadContext.

Definition at line 384 of file simple_thread.hh.

References X86ISA::reg, setVecLaneT(), and X86ISA::val.

Referenced by CheckerCPU::setVecLaneOperandT(), Minor::ExecContext::setVecLaneOperandT(), and SimpleExecContext::setVecLaneOperandT().

◆ setVecLane() [2/4]

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 401 of file simple_thread.hh.

References X86ISA::reg, setVecLaneT(), and X86ISA::val.

◆ setVecLane() [3/4]

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 395 of file simple_thread.hh.

References X86ISA::reg, setVecLaneT(), and X86ISA::val.

◆ setVecLane() [4/4]

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 389 of file simple_thread.hh.

References X86ISA::reg, setVecLaneT(), and X86ISA::val.

◆ setVecLaneFlat()

|

inline |

Definition at line 635 of file simple_thread.hh.

References X86ISA::reg, X86ISA::val, and vecRegs.

Referenced by setVecLaneT().

◆ setVecLaneT()

|

inline |

Write a lane of the destination vector register.

Definition at line 375 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecRegs, X86ISA::reg, setVecLaneFlat(), and X86ISA::val.

Referenced by setVecLane().

◆ setVecPredReg()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 498 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecPredRegs, X86ISA::reg, setVecPredRegFlat(), and X86ISA::val.

Referenced by CheckerThreadContext< TC >::setVecPredReg(), Minor::ExecContext::setVecPredRegOperand(), SimpleExecContext::setVecPredRegOperand(), and CheckerCPU::setVecPredRegOperand().

◆ setVecPredRegFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 666 of file simple_thread.hh.

References X86ISA::reg, X86ISA::val, and vecPredRegs.

Referenced by setVecPredReg().

◆ setVecReg()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 478 of file simple_thread.hh.

References DPRINTF, isa, ArmISA::NumVecRegs, X86ISA::reg, setVecRegFlat(), and X86ISA::val.

Referenced by CheckerThreadContext< TC >::setVecReg(), Minor::ExecContext::setVecRegOperand(), SimpleExecContext::setVecRegOperand(), and CheckerCPU::setVecRegOperand().

◆ setVecRegFlat()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 621 of file simple_thread.hh.

References X86ISA::reg, X86ISA::val, and vecRegs.

Referenced by setVecReg().

◆ socketId()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 213 of file simple_thread.hh.

References ThreadState::socketId().

◆ status()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 242 of file simple_thread.hh.

References ThreadState::_status.

Referenced by activate(), halt(), suspend(), and BaseKvmCPU::wakeup().

◆ suspend()

|

overridevirtual |

Set the status to Suspended.

Implements ThreadContext.

Definition at line 148 of file simple_thread.cc.

References ThreadState::_status, ThreadState::_threadId, ThreadState::baseCpu, curTick(), ThreadState::lastActivate, ThreadState::lastSuspend, status(), BaseCPU::suspendContext(), and ThreadContext::Suspended.

Referenced by X86KvmCPU::deliverInterrupts(), and BaseKvmCPU::handleKvmExit().

◆ syscall()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 588 of file simple_thread.hh.

References ThreadState::process, and Process::syscall().

Referenced by Minor::ExecContext::syscall(), and SimpleExecContext::syscall().

◆ takeOverFrom()

|

overridevirtual |

Implements ThreadContext.

Definition at line 97 of file simple_thread.cc.

References decoder, ThreadState::funcExeInst, ThreadContext::getDecoderPtr(), isa, ThreadContext::readFuncExeInst(), and ThreadState::storeCondFailures.

◆ threadId()

|

inlineoverridevirtual |

Implements ThreadContext.

Definition at line 214 of file simple_thread.hh.

References ThreadState::threadId().

Referenced by SimpleExecContext::armMonitor(), SimpleExecContext::getAddrMonitor(), SimpleExecContext::mwait(), SimpleExecContext::mwaitAtomic(), and name().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements Serializable.

Definition at line 130 of file simple_thread.cc.

References ThreadState::unserialize().

Referenced by BaseKvmCPU::unserializeThread().

Member Data Documentation

◆ _htmCheckpoint

|

protected |

Definition at line 110 of file simple_thread.hh.

Referenced by getHtmCheckpointPtr(), and setHtmCheckpointPtr().

◆ _pcState

|

protected |

Definition at line 107 of file simple_thread.hh.

Referenced by clearArchRegs(), instAddr(), microPC(), nextInstAddr(), pcState(), and pcStateNoRecord().

◆ ccRegs

|

protected |

Definition at line 104 of file simple_thread.hh.

Referenced by clearArchRegs(), readCCRegFlat(), and setCCRegFlat().

◆ comInstEventQueue

| EventQueue SimpleThread::comInstEventQueue |

An instruction-based event queue.

Used for scheduling events based on number of instructions committed.

Definition at line 129 of file simple_thread.hh.

Referenced by descheduleInstCountEvent(), Minor::Execute::doInstCommitAccounting(), getCurrentInstCount(), BaseSimpleCPU::preExecute(), scheduleInstCountEvent(), BaseKvmCPU::setupInstStop(), and BaseKvmCPU::tick().

◆ decoder

| TheISA::Decoder SimpleThread::decoder |

Definition at line 136 of file simple_thread.hh.

Referenced by BaseSimpleCPU::advancePC(), BaseSimpleCPU::checkForInterrupts(), getDecoderPtr(), BaseSimpleCPU::preExecute(), and takeOverFrom().

◆ dtb

| BaseTLB* SimpleThread::dtb |

Definition at line 134 of file simple_thread.hh.

Referenced by AtomicSimpleCPU::amoMem(), demapDataPage(), demapPage(), getDTBPtr(), TimingSimpleCPU::initiateMemAMO(), TimingSimpleCPU::initiateMemRead(), Minor::ExecContext::mwaitAtomic(), CheckerCPU::mwaitAtomic(), SimpleExecContext::mwaitAtomic(), AtomicSimpleCPU::readMem(), AtomicSimpleCPU::writeMem(), and TimingSimpleCPU::writeMem().

◆ floatRegs

|

protected |

Definition at line 100 of file simple_thread.hh.

Referenced by clearArchRegs(), readFloatRegFlat(), and setFloatRegFlat().

◆ htmTransactionStarts

| int64_t SimpleThread::htmTransactionStarts |

Definition at line 139 of file simple_thread.hh.

Referenced by TimingSimpleCPU::completeIfetch(), SimpleExecContext::getHtmTransactionalDepth(), and htmAbortTransaction().

◆ htmTransactionStops

| int64_t SimpleThread::htmTransactionStops |

Definition at line 140 of file simple_thread.hh.

Referenced by TimingSimpleCPU::completeDataAccess(), SimpleExecContext::getHtmTransactionalDepth(), and htmAbortTransaction().

◆ intRegs

|

protected |

Definition at line 101 of file simple_thread.hh.

Referenced by clearArchRegs(), readIntRegFlat(), and setIntRegFlat().

◆ isa

|

protected |

Definition at line 105 of file simple_thread.hh.

Referenced by clearArchRegs(), flattenRegId(), getIsaPtr(), getWritableVecPredReg(), getWritableVecReg(), readCCReg(), readFloatReg(), readIntReg(), readMiscReg(), readMiscRegNoEffect(), readVecElem(), readVecLane(), readVecPredReg(), readVecReg(), setCCReg(), setFloatReg(), setIntReg(), setMiscReg(), setMiscRegNoEffect(), setVecElem(), setVecLaneT(), setVecPredReg(), setVecReg(), SimpleThread(), and takeOverFrom().

◆ itb

| BaseTLB* SimpleThread::itb |

Definition at line 133 of file simple_thread.hh.

Referenced by demapInstPage(), demapPage(), TimingSimpleCPU::fetch(), getITBPtr(), and AtomicSimpleCPU::tick().

◆ memAccPredicate

|

protected |

True if the memory access should be skipped for this instruction.

Definition at line 116 of file simple_thread.hh.

Referenced by readMemAccPredicate(), and setMemAccPredicate().

◆ pcEventQueue

| PCEventQueue SimpleThread::pcEventQueue |

Definition at line 124 of file simple_thread.hh.

Referenced by remove(), and schedule().

◆ predicate

|

protected |

Did this instruction execute or is it predicated false.

Definition at line 113 of file simple_thread.hh.

Referenced by readPredicate(), and setPredicate().

◆ system

| System* SimpleThread::system |

Definition at line 131 of file simple_thread.hh.

Referenced by getSystemPtr().

◆ vecPredRegs

|

protected |

Definition at line 103 of file simple_thread.hh.

Referenced by clearArchRegs(), getWritableVecPredRegFlat(), readVecPredRegFlat(), and setVecPredRegFlat().

◆ vecRegs

|

protected |

Definition at line 102 of file simple_thread.hh.

Referenced by clearArchRegs(), getWritableVecRegFlat(), readVecElemFlat(), readVecLaneFlat(), readVecRegFlat(), setVecElemFlat(), setVecLaneFlat(), and setVecRegFlat().

The documentation for this class was generated from the following files:

- cpu/simple_thread.hh

- cpu/simple_thread.cc