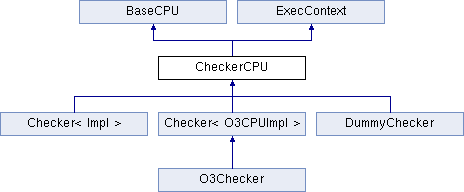

CheckerCPU class. More...

#include <cpu.hh>

Public Types | |

| typedef CheckerCPUParams | Params |

Public Types inherited from BaseCPU Public Types inherited from BaseCPU | |

| typedef BaseCPUParams | Params |

Public Types inherited from ExecContext Public Types inherited from ExecContext | |

| typedef TheISA::PCState | PCState |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | VecElem = TheISA::VecElem |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

Public Member Functions | |

| void | init () override |

| CheckerCPU (Params *p) | |

| virtual | ~CheckerCPU () |

| void | setSystem (System *system) |

| void | setIcachePort (RequestPort *icache_port) |

| void | setDcachePort (RequestPort *dcache_port) |

| Port & | getDataPort () override |

| Purely virtual method that returns a reference to the data port. More... | |

| Port & | getInstPort () override |

| Purely virtual method that returns a reference to the instruction port. More... | |

| BaseTLB * | getITBPtr () |

| BaseTLB * | getDTBPtr () |

| virtual Counter | totalInsts () const override |

| virtual Counter | totalOps () const override |

| void | serialize (CheckpointOut &cp) const override |

| void | unserialize (CheckpointIn &cp) override |

| RegVal | readIntRegOperand (const StaticInst *si, int idx) override |

| Reads an integer register. More... | |

| RegVal | readFloatRegOperandBits (const StaticInst *si, int idx) override |

| Reads a floating point register in its binary format, instead of by value. More... | |

| const VecRegContainer & | readVecRegOperand (const StaticInst *si, int idx) const override |

| Read source vector register operand. More... | |

| VecRegContainer & | getWritableVecRegOperand (const StaticInst *si, int idx) override |

| Read destination vector register operand for modification. More... | |

| VecElem | readVecElemOperand (const StaticInst *si, int idx) const override |

| Vector Elem Interfaces. More... | |

| const VecPredRegContainer & | readVecPredRegOperand (const StaticInst *si, int idx) const override |

| Predicate registers interface. More... | |

| VecPredRegContainer & | getWritableVecPredRegOperand (const StaticInst *si, int idx) override |

| Gets destination predicate register operand for modification. More... | |

| RegVal | readCCRegOperand (const StaticInst *si, int idx) override |

| template<typename T > | |

| void | setScalarResult (T &&t) |

| template<typename T > | |

| void | setVecResult (T &&t) |

| template<typename T > | |

| void | setVecElemResult (T &&t) |

| template<typename T > | |

| void | setVecPredResult (T &&t) |

| void | setIntRegOperand (const StaticInst *si, int idx, RegVal val) override |

| Sets an integer register to a value. More... | |

| void | setFloatRegOperandBits (const StaticInst *si, int idx, RegVal val) override |

| Sets the bits of a floating point register of single width to a binary value. More... | |

| void | setCCRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setVecRegOperand (const StaticInst *si, int idx, const VecRegContainer &val) override |

| Sets a destination vector register operand to a value. More... | |

| void | setVecElemOperand (const StaticInst *si, int idx, const VecElem val) override |

| Sets a vector register to a value. More... | |

| void | setVecPredRegOperand (const StaticInst *si, int idx, const VecPredRegContainer &val) override |

| Sets a destination predicate register operand to a value. More... | |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| Fault | initiateHtmCmd (Request::Flags flags) override |

| Initiate an HTM command, e.g. More... | |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| TheISA::PCState | pcState () const override |

| void | pcState (const TheISA::PCState &val) override |

| Addr | instAddr () |

| Addr | nextInstAddr () |

| MicroPC | microPC () |

| RegVal | readMiscRegNoEffect (int misc_reg) const |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a miscellaneous register, handling any architectural side effects due to reading that register. More... | |

| void | setMiscRegNoEffect (int misc_reg, RegVal val) |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a miscellaneous register, handling any architectural side effects due to writing that register. More... | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | recordPCChange (const TheISA::PCState &val) |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. More... | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| void | demapInstPage (Addr vaddr, uint64_t asn) |

| void | demapDataPage (Addr vaddr, uint64_t asn) |

| RequestPtr | genMemFragmentRequest (Addr frag_addr, int size, Request::Flags flags, const std::vector< bool > &byte_enable, int &frag_size, int &size_left) const |

| Helper function used to generate the request for a single fragment of a memory access. More... | |

| Fault | readMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | amoMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. More... | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. More... | |

| void | wakeup (ThreadID tid) override |

| void | syscall () override |

| Executes a syscall. More... | |

| void | handleError () |

| bool | checkFlags (const RequestPtr &unverified_req, Addr vAddr, Addr pAddr, int flags) |

| Checks if the flags set by the Checker and Checkee match. More... | |

| void | dumpAndExit () |

| ThreadContext * | tcBase () const override |

| Returns a pointer to the ThreadContext. More... | |

| SimpleThread * | threadBase () |

| virtual ConstVecLane8 | readVec8BitLaneOperand (const StaticInst *si, int idx) const override |

| Vector Register Lane Interfaces. More... | |

| virtual ConstVecLane16 | readVec16BitLaneOperand (const StaticInst *si, int idx) const override |

| Reads source vector 16bit operand. More... | |

| virtual ConstVecLane32 | readVec32BitLaneOperand (const StaticInst *si, int idx) const override |

| Reads source vector 32bit operand. More... | |

| virtual ConstVecLane64 | readVec64BitLaneOperand (const StaticInst *si, int idx) const override |

| Reads source vector 64bit operand. More... | |

| template<typename LD > | |

| void | setVecLaneOperandT (const StaticInst *si, int idx, const LD &val) |

| Write a lane of the destination vector operand. More... | |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::Byte > &val) override |

| Write a lane of the destination vector operand. More... | |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::TwoByte > &val) override |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::FourByte > &val) override |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::EightByte > &val) override |

Public Member Functions inherited from BaseCPU Public Member Functions inherited from BaseCPU | |

| virtual PortProxy::SendFunctionalFunc | getSendFunctional () |

| Returns a sendFunctional delegate for use with port proxies. More... | |

| int | cpuId () const |

| Reads this CPU's ID. More... | |

| uint32_t | socketId () const |

| Reads this CPU's Socket ID. More... | |

| RequestorID | dataRequestorId () const |

| Reads this CPU's unique data requestor ID. More... | |

| RequestorID | instRequestorId () const |

| Reads this CPU's unique instruction requestor ID. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. More... | |

| uint32_t | taskId () const |

| Get cpu task id. More... | |

| void | taskId (uint32_t id) |

| Set cpu task id. More... | |

| uint32_t | getPid () const |

| void | setPid (uint32_t pid) |

| void | workItemBegin () |

| void | workItemEnd () |

| Tick | instCount () |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupts (ThreadID tid) |

| bool | checkInterrupts (ThreadID tid) const |

| Trace::InstTracer * | getTracer () |

| Provide access to the tracer pointer. More... | |

| virtual void | activateContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now active. More... | |

| virtual void | suspendContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now suspended. More... | |

| virtual void | haltContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now halted. More... | |

| int | findContext (ThreadContext *tc) |

| Given a Thread Context pointer return the thread num. More... | |

| virtual ThreadContext * | getContext (int tn) |

| Given a thread num get tho thread context for it. More... | |

| unsigned | numContexts () |

| Get the number of thread contexts available. More... | |

| ThreadID | contextToThread (ContextID cid) |

| Convert ContextID to threadID. More... | |

| const Params * | params () const |

| BaseCPU (Params *params, bool is_checker=false) | |

| virtual | ~BaseCPU () |

| void | init () override |

| void | startup () override |

| void | regStats () override |

| void | regProbePoints () override |

| void | registerThreadContexts () |

| void | deschedulePowerGatingEvent () |

| void | schedulePowerGatingEvent () |

| virtual void | switchOut () |

| Prepare for another CPU to take over execution. More... | |

| virtual void | takeOverFrom (BaseCPU *cpu) |

| Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in. More... | |

| void | flushTLBs () |

| Flush all TLBs in the CPU. More... | |

| bool | switchedOut () const |

| Determine if the CPU is switched out. More... | |

| virtual void | verifyMemoryMode () const |

| Verify that the system is in a memory mode supported by the CPU. More... | |

| unsigned int | cacheLineSize () const |

| Get the cache line size of the system. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. More... | |

| virtual void | serializeThread (CheckpointOut &cp, ThreadID tid) const |

| Serialize a single thread. More... | |

| virtual void | unserializeThread (CheckpointIn &cp, ThreadID tid) |

| Unserialize one thread. More... | |

| void | scheduleInstStop (ThreadID tid, Counter insts, const char *cause) |

| Schedule an event that exits the simulation loops after a predefined number of instructions. More... | |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| Get the number of instructions executed by the specified thread on this CPU. More... | |

| void | traceFunctions (Addr pc) |

| void | armMonitor (ThreadID tid, Addr address) |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseTLB *dtb) |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| bool | waitForRemoteGDB () const |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| Helper method to trigger PMU probes for a committed instruction. More... | |

Public Member Functions inherited from ExecContext Public Member Functions inherited from ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| Perform an atomic memory read operation. More... | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| Initiate a timing memory read operation. More... | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >())=0 |

| For atomic-mode contexts, perform an atomic memory write operation. More... | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More... | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More... | |

Public Attributes | |

| SimpleThread * | thread |

| Counter | numLoad |

| Counter | startNumLoad |

| InstResult | unverifiedResult |

| RequestPtr | unverifiedReq |

| uint8_t * | unverifiedMemData |

| bool | changedPC |

| bool | willChangePC |

| TheISA::PCState | newPCState |

| bool | exitOnError |

| bool | updateOnError |

| bool | warnOnlyOnLoadError |

| InstSeqNum | youngestSN |

Public Attributes inherited from BaseCPU Public Attributes inherited from BaseCPU | |

| ThreadID | numThreads |

| Number of threads we're actually simulating (<= SMT_MAX_THREADS). More... | |

| System * | system |

| Stats::Scalar | numCycles |

| Stats::Scalar | numWorkItemsStarted |

| Stats::Scalar | numWorkItemsCompleted |

| Cycles | syscallRetryLatency |

Protected Types | |

| typedef TheISA::MachInst | MachInst |

| using | VecRegContainer = TheISA::VecRegContainer |

Protected Types inherited from BaseCPU Protected Types inherited from BaseCPU | |

| enum | CPUState { CPU_STATE_ON, CPU_STATE_SLEEP, CPU_STATE_WAKEUP } |

Protected Attributes | |

| RequestorID | requestorId |

| id attached to all issued requests More... | |

| std::vector< Process * > | workload |

| System * | systemPtr |

| RequestPort * | icachePort |

| RequestPort * | dcachePort |

| ThreadContext * | tc |

| BaseTLB * | itb |

| BaseTLB * | dtb |

| std::queue< InstResult > | result |

| StaticInstPtr | curStaticInst |

| StaticInstPtr | curMacroStaticInst |

| Counter | numInst |

| Counter | startNumInst |

| std::queue< int > | miscRegIdxs |

Protected Attributes inherited from BaseCPU Protected Attributes inherited from BaseCPU | |

| Tick | instCnt |

| Instruction count used for SPARC misc register. More... | |

| int | _cpuId |

| const uint32_t | _socketId |

| Each cpu will have a socket ID that corresponds to its physical location in the system. More... | |

| RequestorID | _instRequestorId |

| instruction side request id that must be placed in all requests More... | |

| RequestorID | _dataRequestorId |

| data side request id that must be placed in all requests More... | |

| uint32_t | _taskId |

| An intrenal representation of a task identifier within gem5. More... | |

| uint32_t | _pid |

| The current OS process ID that is executing on this processor. More... | |

| bool | _switchedOut |

| Is the CPU switched out or active? More... | |

| const unsigned int | _cacheLineSize |

| Cache the cache line size that we get from the system. More... | |

| std::vector< BaseInterrupts * > | interrupts |

| std::vector< ThreadContext * > | threadContexts |

| Trace::InstTracer * | tracer |

| Cycles | previousCycle |

| CPUState | previousState |

| const Cycles | pwrGatingLatency |

| const bool | powerGatingOnIdle |

| EventFunctionWrapper | enterPwrGatingEvent |

| ProbePoints::PMUUPtr | ppRetiredInsts |

| Instruction commit probe point. More... | |

| ProbePoints::PMUUPtr | ppRetiredInstsPC |

| ProbePoints::PMUUPtr | ppRetiredLoads |

| Retired load instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredStores |

| Retired store instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredBranches |

| Retired branches (any type) More... | |

| ProbePoints::PMUUPtr | ppAllCycles |

| CPU cycle counter even if any thread Context is suspended. More... | |

| ProbePoints::PMUUPtr | ppActiveCycles |

| CPU cycle counter, only counts if any thread contexts is active. More... | |

| ProbePointArg< bool > * | ppSleeping |

| ProbePoint that signals transitions of threadContexts sets. More... | |

Additional Inherited Members | |

Static Public Member Functions inherited from BaseCPU Static Public Member Functions inherited from BaseCPU | |

| static int | numSimulatedInsts () |

| static int | numSimulatedOps () |

| static void | wakeup (ThreadID tid) |

| static int | numSimulatedCPUs () |

| static Counter | numSimulatedInsts () |

| static Counter | numSimulatedOps () |

Static Public Attributes inherited from BaseCPU Static Public Attributes inherited from BaseCPU | |

| static const uint32_t | invldPid = std::numeric_limits<uint32_t>::max() |

| Invalid or unknown Pid. More... | |

| static const Addr | PCMask = ~((Addr)sizeof(TheISA::MachInst) - 1) |

Protected Member Functions inherited from BaseCPU Protected Member Functions inherited from BaseCPU | |

| void | updateCycleCounters (CPUState state) |

| base method keeping track of cycle progression More... | |

| void | enterPwrGating () |

| ProbePoints::PMUUPtr | pmuProbePoint (const char *name) |

| Helper method to instantiate probe points belonging to this object. More... | |

Detailed Description

CheckerCPU class.

Dynamically verifies instructions as they are completed by making sure that the instruction and its results match the independent execution of the benchmark inside the checker. The checker verifies instructions in order, regardless of the order in which instructions complete. There are certain results that can not be verified, specifically the result of a store conditional or the values of uncached accesses. In these cases, and with instructions marked as "IsUnverifiable", the checker assumes that the value from the main CPU's execution is correct and simply copies that value. It provides a CheckerThreadContext (see checker/thread_context.hh) that provides hooks for updating the Checker's state through any ThreadContext accesses. This allows the checker to be able to correctly verify instructions, even with external accesses to the ThreadContext that change state.

Member Typedef Documentation

◆ MachInst

|

protected |

◆ Params

| typedef CheckerCPUParams CheckerCPU::Params |

◆ VecRegContainer

|

protected |

Constructor & Destructor Documentation

◆ CheckerCPU()

| CheckerCPU::CheckerCPU | ( | Params * | p | ) |

Definition at line 64 of file cpu.cc.

References changedPC, curMacroStaticInst, curStaticInst, dtb, exitOnError, itb, numInst, numLoad, MipsISA::p, startNumInst, startNumLoad, updateOnError, warnOnlyOnLoadError, willChangePC, workload, and youngestSN.

◆ ~CheckerCPU()

Member Function Documentation

◆ amoMem()

|

inlineoverride |

◆ armMonitor()

|

inlineoverridevirtual |

◆ checkFlags()

| bool CheckerCPU::checkFlags | ( | const RequestPtr & | unverified_req, |

| Addr | vAddr, | ||

| Addr | pAddr, | ||

| int | flags | ||

| ) |

Checks if the flags set by the Checker and Checkee match.

Definition at line 360 of file cpu.cc.

Referenced by readMem(), and writeMem().

◆ demapDataPage()

|

inline |

Definition at line 562 of file cpu.hh.

References BaseTLB::demapPage(), and MipsISA::vaddr.

◆ demapInstPage()

|

inline |

Definition at line 556 of file cpu.hh.

References BaseTLB::demapPage(), and MipsISA::vaddr.

◆ demapPage()

|

inlineoverridevirtual |

Invalidate a page in the DTLB and ITLB.

Implements ExecContext.

Definition at line 541 of file cpu.hh.

References BaseTLB::demapPage(), and MipsISA::vaddr.

◆ dumpAndExit()

| void CheckerCPU::dumpAndExit | ( | ) |

Definition at line 377 of file cpu.cc.

References curTick(), panic, SimpleThread::pcState(), thread, and warn.

Referenced by Checker< O3CPUImpl >::dumpAndExit(), handleError(), and Checker< O3CPUImpl >::handleError().

◆ genMemFragmentRequest()

| RequestPtr CheckerCPU::genMemFragmentRequest | ( | Addr | frag_addr, |

| int | size, | ||

| Request::Flags | flags, | ||

| const std::vector< bool > & | byte_enable, | ||

| int & | frag_size, | ||

| int & | size_left | ||

| ) | const |

Helper function used to generate the request for a single fragment of a memory access.

Takes care of setting up the appropriate byte-enable mask for the fragment, given the mask for the entire memory access.

- Parameters

-

frag_addr Start address of the fragment. size Total size of the memory access in bytes. flags Request flags. byte_enable Byte-enable mask for the entire memory access. [out] frag_size Fragment size. [in,out] size_left Size left to be processed in the memory access.

- Returns

- Pointer to the allocated Request, nullptr if the byte-enable mask is all-false for the fragment.

Definition at line 138 of file cpu.cc.

References addrBlockOffset(), BaseCPU::cacheLineSize(), ThreadContext::contextId(), isAnyActiveElement(), SimpleThread::pcState(), requestorId, tc, and thread.

Referenced by readMem(), and writeMem().

◆ getAddrMonitor()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 552 of file cpu.hh.

References BaseCPU::getCpuAddrMonitor().

◆ getDataPort()

|

inlineoverridevirtual |

Purely virtual method that returns a reference to the data port.

All subclasses must implement this method.

- Returns

- a reference to the data port

Implements BaseCPU.

Definition at line 107 of file cpu.hh.

References dcachePort.

◆ getDTBPtr()

|

inline |

Definition at line 157 of file cpu.hh.

References dtb.

Referenced by BaseCPU::flushTLBs(), and BaseCPU::takeOverFrom().

◆ getHtmTransactionalDepth()

|

inlineoverridevirtual |

◆ getHtmTransactionUid()

|

inlineoverridevirtual |

◆ getInstPort()

|

inlineoverridevirtual |

Purely virtual method that returns a reference to the instruction port.

All subclasses must implement this method.

- Returns

- a reference to the instruction port

Implements BaseCPU.

Definition at line 116 of file cpu.hh.

References icachePort.

◆ getITBPtr()

|

inline |

Definition at line 156 of file cpu.hh.

References itb.

Referenced by BaseCPU::flushTLBs(), and BaseCPU::takeOverFrom().

◆ getWritableVecPredRegOperand()

|

inlineoverridevirtual |

Gets destination predicate register operand for modification.

Implements ExecContext.

Definition at line 314 of file cpu.hh.

References SimpleThread::getWritableVecPredReg(), X86ISA::reg, ArmISA::si, and thread.

◆ getWritableVecRegOperand()

|

inlineoverridevirtual |

Read destination vector register operand for modification.

Implements ExecContext.

Definition at line 218 of file cpu.hh.

References SimpleThread::getWritableVecReg(), X86ISA::reg, ArmISA::si, and thread.

◆ handleError()

|

inline |

Definition at line 618 of file cpu.hh.

References dumpAndExit(), and exitOnError.

Referenced by readMem(), Checker< O3CPUImpl >::verify(), and writeMem().

◆ inHtmTransactionalState()

|

inlineoverridevirtual |

◆ init()

◆ initiateHtmCmd()

|

inlineoverridevirtual |

Initiate an HTM command, e.g.

tell Ruby we're starting/stopping a transaction

Implements ExecContext.

◆ instAddr()

|

inline |

Definition at line 480 of file cpu.hh.

References SimpleThread::instAddr(), and thread.

◆ microPC()

|

inline |

Definition at line 482 of file cpu.hh.

References SimpleThread::microPC(), and thread.

◆ mwait()

|

inlineoverridevirtual |

◆ mwaitAtomic()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 550 of file cpu.hh.

References SimpleThread::dtb, BaseCPU::mwaitAtomic(), tc, and thread.

◆ newHtmTransactionUid()

|

inlineoverridevirtual |

◆ nextInstAddr()

|

inline |

Definition at line 481 of file cpu.hh.

References SimpleThread::nextInstAddr(), and thread.

◆ pcState() [1/2]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 472 of file cpu.hh.

References SimpleThread::pcState(), and thread.

Referenced by Checker< O3CPUImpl >::advancePC(), Checker< O3CPUImpl >::handlePendingInt(), and Checker< O3CPUImpl >::verify().

◆ pcState() [2/2]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 474 of file cpu.hh.

References DPRINTF, SimpleThread::pcState(), thread, and X86ISA::val.

◆ readCCRegOperand()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 322 of file cpu.hh.

References SimpleThread::readCCReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readFloatRegOperandBits()

|

inlineoverridevirtual |

Reads a floating point register in its binary format, instead of by value.

Implements ExecContext.

Definition at line 196 of file cpu.hh.

References SimpleThread::readFloatReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readIntRegOperand()

|

inlineoverridevirtual |

Reads an integer register.

Implements ExecContext.

Definition at line 188 of file cpu.hh.

References SimpleThread::readIntReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readMem()

|

override |

Definition at line 171 of file cpu.cc.

References addr, checkFlags(), Packet::createRead(), curTick(), data, Packet::dataStatic(), dcachePort, dtb, genMemFragmentRequest(), handleError(), Request::NO_ACCESS, NoFault, BaseTLB::Read, RequestPort::sendFunctional(), tc, BaseTLB::translateFunctional(), unverifiedMemData, unverifiedReq, and warn.

◆ readMemAccPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 426 of file cpu.hh.

References SimpleThread::readMemAccPredicate(), and thread.

◆ readMiscReg()

|

inlineoverridevirtual |

Reads a miscellaneous register, handling any architectural side effects due to reading that register.

Implements ExecContext.

Definition at line 492 of file cpu.hh.

References SimpleThread::readMiscReg(), and thread.

◆ readMiscRegNoEffect()

|

inline |

Definition at line 486 of file cpu.hh.

References SimpleThread::readMiscRegNoEffect(), and thread.

◆ readMiscRegOperand()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 516 of file cpu.hh.

References SimpleThread::readMiscReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 417 of file cpu.hh.

References SimpleThread::readPredicate(), and thread.

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements ExecContext.

Definition at line 605 of file cpu.hh.

References SimpleThread::readStCondFailures(), and thread.

◆ readVec16BitLaneOperand()

|

inlineoverridevirtual |

Reads source vector 16bit operand.

Implements ExecContext.

Definition at line 238 of file cpu.hh.

References SimpleThread::readVec16BitLaneReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readVec32BitLaneOperand()

|

inlineoverridevirtual |

Reads source vector 32bit operand.

Implements ExecContext.

Definition at line 247 of file cpu.hh.

References SimpleThread::readVec32BitLaneReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readVec64BitLaneOperand()

|

inlineoverridevirtual |

Reads source vector 64bit operand.

Implements ExecContext.

Definition at line 256 of file cpu.hh.

References SimpleThread::readVec64BitLaneReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readVec8BitLaneOperand()

|

inlineoverridevirtual |

Vector Register Lane Interfaces.

Reads source vector 8bit operand.

Implements ExecContext.

Definition at line 229 of file cpu.hh.

References SimpleThread::readVec8BitLaneReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readVecElemOperand()

|

inlineoverridevirtual |

Vector Elem Interfaces.

Reads an element of a vector register.

Implements ExecContext.

Definition at line 299 of file cpu.hh.

References SimpleThread::readVecElem(), X86ISA::reg, ArmISA::si, and thread.

◆ readVecPredRegOperand()

|

inlineoverridevirtual |

Predicate registers interface.

Reads source predicate register operand.

Implements ExecContext.

Definition at line 306 of file cpu.hh.

References SimpleThread::readVecPredReg(), X86ISA::reg, ArmISA::si, and thread.

◆ readVecRegOperand()

|

inlineoverridevirtual |

Read source vector register operand.

Implements ExecContext.

Definition at line 207 of file cpu.hh.

References SimpleThread::readVecReg(), X86ISA::reg, ArmISA::si, and thread.

◆ recordPCChange()

|

inline |

Definition at line 534 of file cpu.hh.

References changedPC, newPCState, and X86ISA::val.

Referenced by CheckerThreadContext< TC >::pcState().

◆ serialize()

|

override |

◆ setCCRegOperand()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 380 of file cpu.hh.

References X86ISA::reg, SimpleThread::setCCReg(), setScalarResult(), ArmISA::si, thread, and X86ISA::val.

◆ setDcachePort()

| void CheckerCPU::setDcachePort | ( | RequestPort * | dcache_port | ) |

Definition at line 122 of file cpu.cc.

References dcachePort.

◆ setFloatRegOperandBits()

|

inlineoverridevirtual |

Sets the bits of a floating point register of single width to a binary value.

Implements ExecContext.

Definition at line 371 of file cpu.hh.

References X86ISA::reg, SimpleThread::setFloatReg(), setScalarResult(), ArmISA::si, thread, and X86ISA::val.

◆ setIcachePort()

| void CheckerCPU::setIcachePort | ( | RequestPort * | icache_port | ) |

Definition at line 116 of file cpu.cc.

References icachePort.

◆ setIntRegOperand()

|

inlineoverridevirtual |

Sets an integer register to a value.

Implements ExecContext.

Definition at line 362 of file cpu.hh.

References X86ISA::reg, SimpleThread::setIntReg(), setScalarResult(), ArmISA::si, thread, and X86ISA::val.

◆ setMemAccPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 432 of file cpu.hh.

References SimpleThread::setMemAccPredicate(), thread, and X86ISA::val.

◆ setMiscReg()

|

inlineoverridevirtual |

Sets a miscellaneous register, handling any architectural side effects due to writing that register.

Implements ExecContext.

Definition at line 507 of file cpu.hh.

References DPRINTF, miscRegIdxs, SimpleThread::setMiscReg(), thread, and X86ISA::val.

Referenced by setMiscRegOperand().

◆ setMiscRegNoEffect()

|

inline |

Definition at line 498 of file cpu.hh.

References DPRINTF, miscRegIdxs, SimpleThread::setMiscRegNoEffect(), thread, and X86ISA::val.

◆ setMiscRegOperand()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 524 of file cpu.hh.

References RegId::index(), X86ISA::reg, setMiscReg(), ArmISA::si, and X86ISA::val.

◆ setPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 420 of file cpu.hh.

References SimpleThread::setPredicate(), thread, and X86ISA::val.

◆ setScalarResult()

|

inline |

Definition at line 331 of file cpu.hh.

References result, InstResult::Scalar, and ArmISA::t.

Referenced by setCCRegOperand(), setFloatRegOperandBits(), and setIntRegOperand().

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements ExecContext.

◆ setSystem()

| void CheckerCPU::setSystem | ( | System * | system | ) |

Definition at line 95 of file cpu.cc.

References dtb, FullSystem, SimpleThread::getTC(), itb, MipsISA::p, BaseCPU::system, systemPtr, tc, thread, BaseCPU::threadContexts, and workload.

Referenced by BaseSimpleCPU::BaseSimpleCPU().

◆ setVecElemOperand()

|

inlineoverridevirtual |

Sets a vector register to a value.

Implements ExecContext.

Definition at line 399 of file cpu.hh.

References X86ISA::reg, SimpleThread::setVecElem(), setVecElemResult(), ArmISA::si, thread, and X86ISA::val.

◆ setVecElemResult()

|

inline |

Definition at line 347 of file cpu.hh.

References result, ArmISA::t, and InstResult::VecElem.

Referenced by setVecElemOperand().

◆ setVecLaneOperand() [1/4]

|

inlineoverridevirtual |

Write a lane of the destination vector operand.

Implements ExecContext.

Definition at line 273 of file cpu.hh.

References setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperand() [2/4]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 291 of file cpu.hh.

References setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperand() [3/4]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 285 of file cpu.hh.

References setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperand() [4/4]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 279 of file cpu.hh.

References setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperandT()

|

inline |

Write a lane of the destination vector operand.

Definition at line 266 of file cpu.hh.

References X86ISA::reg, SimpleThread::setVecLane(), ArmISA::si, thread, and X86ISA::val.

Referenced by setVecLaneOperand().

◆ setVecPredRegOperand()

|

inlineoverridevirtual |

Sets a destination predicate register operand to a value.

Implements ExecContext.

Definition at line 408 of file cpu.hh.

References X86ISA::reg, SimpleThread::setVecPredReg(), setVecPredResult(), ArmISA::si, thread, and X86ISA::val.

◆ setVecPredResult()

|

inline |

Definition at line 355 of file cpu.hh.

References result, ArmISA::t, and InstResult::VecPredReg.

Referenced by setVecPredRegOperand().

◆ setVecRegOperand()

|

inlineoverridevirtual |

Sets a destination vector register operand to a value.

Implements ExecContext.

Definition at line 389 of file cpu.hh.

References X86ISA::reg, SimpleThread::setVecReg(), setVecResult(), ArmISA::si, thread, and X86ISA::val.

◆ setVecResult()

|

inline |

Definition at line 339 of file cpu.hh.

References result, ArmISA::t, and InstResult::VecReg.

Referenced by setVecRegOperand().

◆ syscall()

|

inlineoverridevirtual |

◆ tcBase()

|

inlineoverridevirtual |

Returns a pointer to the ThreadContext.

Implements ExecContext.

Definition at line 629 of file cpu.hh.

References tc.

◆ threadBase()

|

inline |

◆ totalInsts()

|

inlineoverridevirtual |

◆ totalOps()

|

inlineoverridevirtual |

◆ unserialize()

|

override |

◆ wakeup()

|

inlineoverridevirtual |

◆ writeMem()

|

override |

Definition at line 255 of file cpu.cc.

References addr, checkFlags(), curTick(), data, dtb, genMemFragmentRequest(), handleError(), NoFault, Request::STORE_NO_DATA, tc, BaseTLB::translateFunctional(), unverifiedMemData, unverifiedReq, warn, and BaseTLB::Write.

Member Data Documentation

◆ changedPC

| bool CheckerCPU::changedPC |

Definition at line 636 of file cpu.hh.

Referenced by CheckerCPU(), and recordPCChange().

◆ curMacroStaticInst

|

protected |

Definition at line 143 of file cpu.hh.

Referenced by CheckerCPU().

◆ curStaticInst

|

protected |

Definition at line 142 of file cpu.hh.

Referenced by CheckerCPU().

◆ dcachePort

|

protected |

Definition at line 131 of file cpu.hh.

Referenced by getDataPort(), readMem(), and setDcachePort().

◆ dtb

|

protected |

Definition at line 136 of file cpu.hh.

Referenced by CheckerCPU(), getDTBPtr(), readMem(), setSystem(), and writeMem().

◆ exitOnError

| bool CheckerCPU::exitOnError |

Definition at line 639 of file cpu.hh.

Referenced by CheckerCPU(), handleError(), and Checker< O3CPUImpl >::handleError().

◆ icachePort

|

protected |

Definition at line 130 of file cpu.hh.

Referenced by getInstPort(), and setIcachePort().

◆ itb

|

protected |

Definition at line 135 of file cpu.hh.

Referenced by CheckerCPU(), getITBPtr(), and setSystem().

◆ miscRegIdxs

|

protected |

Definition at line 149 of file cpu.hh.

Referenced by setMiscReg(), and setMiscRegNoEffect().

◆ newPCState

| TheISA::PCState CheckerCPU::newPCState |

Definition at line 638 of file cpu.hh.

Referenced by recordPCChange().

◆ numInst

|

protected |

Definition at line 146 of file cpu.hh.

Referenced by CheckerCPU().

◆ numLoad

| Counter CheckerCPU::numLoad |

Definition at line 170 of file cpu.hh.

Referenced by CheckerCPU().

◆ requestorId

|

protected |

id attached to all issued requests

Definition at line 92 of file cpu.hh.

Referenced by genMemFragmentRequest().

◆ result

|

protected |

Definition at line 140 of file cpu.hh.

Referenced by setScalarResult(), setVecElemResult(), setVecPredResult(), and setVecResult().

◆ startNumInst

|

protected |

Definition at line 147 of file cpu.hh.

Referenced by CheckerCPU().

◆ startNumLoad

| Counter CheckerCPU::startNumLoad |

Definition at line 171 of file cpu.hh.

Referenced by CheckerCPU().

◆ systemPtr

|

protected |

Definition at line 128 of file cpu.hh.

Referenced by setSystem().

◆ tc

|

protected |

Definition at line 133 of file cpu.hh.

Referenced by genMemFragmentRequest(), mwaitAtomic(), readMem(), setSystem(), tcBase(), and writeMem().

◆ thread

| SimpleThread* CheckerCPU::thread |

Definition at line 154 of file cpu.hh.

Referenced by dumpAndExit(), genMemFragmentRequest(), getWritableVecPredRegOperand(), getWritableVecRegOperand(), instAddr(), microPC(), mwaitAtomic(), nextInstAddr(), pcState(), readCCRegOperand(), readFloatRegOperandBits(), readIntRegOperand(), readMemAccPredicate(), readMiscReg(), readMiscRegNoEffect(), readMiscRegOperand(), readPredicate(), readStCondFailures(), readVec16BitLaneOperand(), readVec32BitLaneOperand(), readVec64BitLaneOperand(), readVec8BitLaneOperand(), readVecElemOperand(), readVecPredRegOperand(), readVecRegOperand(), setCCRegOperand(), setFloatRegOperandBits(), setIntRegOperand(), setMemAccPredicate(), setMiscReg(), setMiscRegNoEffect(), setPredicate(), setSystem(), setVecElemOperand(), setVecLaneOperandT(), setVecPredRegOperand(), setVecRegOperand(), and threadBase().

◆ unverifiedMemData

| uint8_t* CheckerCPU::unverifiedMemData |

Definition at line 634 of file cpu.hh.

Referenced by readMem(), and writeMem().

◆ unverifiedReq

| RequestPtr CheckerCPU::unverifiedReq |

Definition at line 633 of file cpu.hh.

Referenced by readMem(), and writeMem().

◆ unverifiedResult

| InstResult CheckerCPU::unverifiedResult |

◆ updateOnError

| bool CheckerCPU::updateOnError |

Definition at line 640 of file cpu.hh.

Referenced by CheckerCPU(), and Checker< O3CPUImpl >::handleError().

◆ warnOnlyOnLoadError

| bool CheckerCPU::warnOnlyOnLoadError |

Definition at line 641 of file cpu.hh.

Referenced by CheckerCPU().

◆ willChangePC

| bool CheckerCPU::willChangePC |

Definition at line 637 of file cpu.hh.

Referenced by CheckerCPU().

◆ workload

|

protected |

Definition at line 126 of file cpu.hh.

Referenced by CheckerCPU(), and setSystem().

◆ youngestSN

| InstSeqNum CheckerCPU::youngestSN |

Definition at line 643 of file cpu.hh.

Referenced by CheckerCPU().

The documentation for this class was generated from the following files: