DRAM specific generator is for issuing request with variable page hit length and bank utilization. More...

#include <dram_gen.hh>

Public Member Functions | |

| DramGen (SimObject &obj, RequestorID requestor_id, Tick _duration, Addr start_addr, Addr end_addr, Addr _blocksize, Addr cacheline_size, Tick min_period, Tick max_period, uint8_t read_percent, Addr data_limit, unsigned int num_seq_pkts, unsigned int page_size, unsigned int nbr_of_banks_DRAM, unsigned int nbr_of_banks_util, enums::AddrMap addr_mapping, unsigned int nbr_of_ranks) | |

| Create a DRAM address sequence generator. | |

| PacketPtr | getNextPacket () |

| Get the next generated packet. | |

| void | genStartAddr (unsigned int new_bank, unsigned int new_rank) |

| Insert bank, rank, and column bits into packed address to create address for 1st command in a series. | |

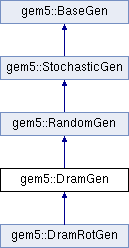

| Public Member Functions inherited from gem5::RandomGen | |

| RandomGen (SimObject &obj, RequestorID requestor_id, Tick _duration, Addr start_addr, Addr end_addr, Addr _blocksize, Addr cacheline_size, Tick min_period, Tick max_period, uint8_t read_percent, Addr data_limit) | |

| Create a random address sequence generator. | |

| void | enter () |

| Enter this generator state. | |

| PacketPtr | getNextPacket () |

| Get the next generated packet. | |

| Tick | nextPacketTick (bool elastic, Tick delay) const |

| Determine the tick when the next packet is available. | |

| Public Member Functions inherited from gem5::StochasticGen | |

| StochasticGen (SimObject &obj, RequestorID requestor_id, Tick _duration, Addr start_addr, Addr end_addr, Addr _blocksize, Addr cacheline_size, Tick min_period, Tick max_period, uint8_t read_percent, Addr data_limit) | |

| Public Member Functions inherited from gem5::BaseGen | |

| BaseGen (SimObject &obj, RequestorID requestor_id, Tick _duration) | |

| Create a base generator. | |

| virtual | ~BaseGen () |

| std::string | name () const |

| Get the name, useful for DPRINTFs. | |

| virtual void | exit () |

| Exit this generator state. | |

Protected Attributes | |

| const unsigned int | numSeqPkts |

| Number of sequential DRAM packets to be generated per cpu request. | |

| unsigned int | countNumSeqPkts |

| Track number of sequential packets generated for a request. | |

| Addr | addr |

| Address of request. | |

| bool | isRead |

| Remember type of requests to be generated in series. | |

| const unsigned int | pageSize |

| Page size of DRAM. | |

| const unsigned int | pageBits |

| Number of page bits in DRAM address. | |

| const unsigned int | bankBits |

| Number of bank bits in DRAM address. | |

| const unsigned int | blockBits |

| Number of block bits in DRAM address. | |

| const unsigned int | nbrOfBanksDRAM |

| Number of banks in DRAM. | |

| const unsigned int | nbrOfBanksUtil |

| Number of banks to be utilized for a given configuration. | |

| enums::AddrMap | addrMapping |

| Address mapping to be used. | |

| const unsigned int | rankBits |

| Number of rank bits in DRAM address. | |

| const unsigned int | nbrOfRanks |

| Number of ranks to be utilized for a given configuration. | |

| Protected Attributes inherited from gem5::RandomGen | |

| Addr | dataManipulated |

| Counter to determine the amount of data manipulated. | |

| Protected Attributes inherited from gem5::StochasticGen | |

| const Addr | startAddr |

| Start of address range. | |

| const Addr | endAddr |

| End of address range. | |

| const Addr | blocksize |

| Blocksize and address increment. | |

| const Addr | cacheLineSize |

| Cache line size in the simulated system. | |

| const Tick | minPeriod |

| Request generation period. | |

| const Tick | maxPeriod |

| const uint8_t | readPercent |

| Percent of generated transactions that should be reads. | |

| const Addr | dataLimit |

| Maximum amount of data to manipulate. | |

| Protected Attributes inherited from gem5::BaseGen | |

| const std::string | _name |

| Name to use for status and debug printing. | |

| const RequestorID | requestorId |

| The RequestorID used for generating requests. | |

| Random::RandomPtr | rng = Random::genRandom() |

Additional Inherited Members | |

| Public Attributes inherited from gem5::BaseGen | |

| const Tick | duration |

| Time to spend in this state. | |

| Protected Member Functions inherited from gem5::BaseGen | |

| PacketPtr | getPacket (Addr addr, unsigned size, const MemCmd &cmd, Request::FlagsType flags=0) |

| Generate a new request and associated packet. | |

Detailed Description

DRAM specific generator is for issuing request with variable page hit length and bank utilization.

Currently assumes a single channel configuration.

Definition at line 61 of file dram_gen.hh.

Constructor & Destructor Documentation

◆ DramGen()

| gem5::DramGen::DramGen | ( | SimObject & | obj, |

| RequestorID | requestor_id, | ||

| Tick | _duration, | ||

| Addr | start_addr, | ||

| Addr | end_addr, | ||

| Addr | _blocksize, | ||

| Addr | cacheline_size, | ||

| Tick | min_period, | ||

| Tick | max_period, | ||

| uint8_t | read_percent, | ||

| Addr | data_limit, | ||

| unsigned int | num_seq_pkts, | ||

| unsigned int | page_size, | ||

| unsigned int | nbr_of_banks_DRAM, | ||

| unsigned int | nbr_of_banks_util, | ||

| enums::AddrMap | addr_mapping, | ||

| unsigned int | nbr_of_ranks ) |

Create a DRAM address sequence generator.

- Parameters

-

obj SimObject owning this sequence generator requestor_id RequestorID related to the memory requests _duration duration of this state before transitioning start_addr Start address end_addr End address _blocksize Size used for transactions injected cacheline_size cache line size in the system min_period Lower limit of random inter-transaction time max_period Upper limit of random inter-transaction time read_percent Percent of transactions that are reads data_limit Upper limit on how much data to read/write num_seq_pkts Number of packets per stride, each of _blocksize page_size Page size (bytes) used in the DRAM nbr_of_banks_DRAM Total number of banks in DRAM nbr_of_banks_util Number of banks to utilized, for N banks, we will use banks: 0->(N-1) addr_mapping Address mapping to be used, assumes single channel system

Definition at line 49 of file dram_gen.cc.

References addr, addrMapping, bankBits, blockBits, countNumSeqPkts, fatal, gem5::floorLog2(), isRead, nbrOfBanksDRAM, nbrOfBanksUtil, nbrOfRanks, numSeqPkts, pageBits, pageSize, gem5::RandomGen::RandomGen(), and rankBits.

Referenced by gem5::DramRotGen::DramRotGen().

Member Function Documentation

◆ genStartAddr()

| void gem5::DramGen::genStartAddr | ( | unsigned int | new_bank, |

| unsigned int | new_rank ) |

Insert bank, rank, and column bits into packed address to create address for 1st command in a series.

- Parameters

-

new_bank Bank number of next packet series new_rank Rank value of next packet series

Definition at line 145 of file dram_gen.cc.

References addr, addrMapping, bankBits, blockBits, gem5::StochasticGen::blocksize, gem5::StochasticGen::endAddr, numSeqPkts, pageBits, pageSize, rankBits, gem5::replaceBits(), gem5::BaseGen::rng, and gem5::StochasticGen::startAddr.

Referenced by getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ getNextPacket()

|

virtual |

Get the next generated packet.

- Returns

- A packet to be sent at the current tick

Implements gem5::BaseGen.

Reimplemented in gem5::DramRotGen.

Definition at line 80 of file dram_gen.cc.

References addr, addrMapping, bankBits, blockBits, gem5::StochasticGen::blocksize, countNumSeqPkts, gem5::RandomGen::dataManipulated, DPRINTF, genStartAddr(), gem5::BaseGen::getPacket(), isRead, nbrOfBanksDRAM, nbrOfBanksUtil, nbrOfRanks, numSeqPkts, pageBits, pageSize, rankBits, gem5::StochasticGen::readPercent, gem5::MemCmd::ReadReq, gem5::replaceBits(), gem5::BaseGen::rng, and gem5::MemCmd::WriteReq.

Member Data Documentation

◆ addr

|

protected |

Address of request.

Definition at line 118 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ addrMapping

|

protected |

Address mapping to be used.

Definition at line 142 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ bankBits

|

protected |

Number of bank bits in DRAM address.

Definition at line 130 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ blockBits

|

protected |

Number of block bits in DRAM address.

Definition at line 133 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ countNumSeqPkts

|

protected |

Track number of sequential packets generated for a request.

Definition at line 115 of file dram_gen.hh.

Referenced by DramGen(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ isRead

|

protected |

Remember type of requests to be generated in series.

Definition at line 121 of file dram_gen.hh.

Referenced by DramGen(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ nbrOfBanksDRAM

|

protected |

Number of banks in DRAM.

Definition at line 136 of file dram_gen.hh.

Referenced by DramGen(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ nbrOfBanksUtil

|

protected |

Number of banks to be utilized for a given configuration.

Definition at line 139 of file dram_gen.hh.

Referenced by DramGen(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ nbrOfRanks

|

protected |

Number of ranks to be utilized for a given configuration.

Definition at line 148 of file dram_gen.hh.

Referenced by DramGen(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ numSeqPkts

|

protected |

Number of sequential DRAM packets to be generated per cpu request.

Definition at line 112 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ pageBits

|

protected |

Number of page bits in DRAM address.

Definition at line 127 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ pageSize

|

protected |

Page size of DRAM.

Definition at line 124 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

◆ rankBits

|

protected |

Number of rank bits in DRAM address.

Definition at line 145 of file dram_gen.hh.

Referenced by DramGen(), genStartAddr(), getNextPacket(), and gem5::DramRotGen::getNextPacket().

The documentation for this class was generated from the following files:

- cpu/testers/traffic_gen/dram_gen.hh

- cpu/testers/traffic_gen/dram_gen.cc

Generated on Sat Oct 18 2025 08:06:50 for gem5 by doxygen 1.14.0