#include <request.hh>

Public Types | |

| enum | : FlagsType { ARCH_BITS = 0x000000FF , INST_FETCH = 0x00000100 , PHYSICAL = 0x00000200 , UNCACHEABLE = 0x00000400 , STRICT_ORDER = 0x00000800 , PRIVILEGED = 0x00008000 , CACHE_BLOCK_ZERO = 0x00010000 , NO_ACCESS = 0x00080000 , LOCKED_RMW = 0x00100000 , LLSC = 0x00200000 , MEM_SWAP = 0x00400000 , MEM_SWAP_COND = 0x00800000 , READ_MODIFY_WRITE = 0x0020000000000000 , PREFETCH = 0x01000000 , PF_EXCLUSIVE = 0x02000000 , EVICT_NEXT = 0x04000000 , ACQUIRE = 0x00020000 , RELEASE = 0x00040000 , ATOMIC_RETURN_OP = 0x40000000 , ATOMIC_NO_RETURN_OP = 0x80000000 , KERNEL = 0x00001000 , SECURE = 0x10000000 , PT_WALK = 0x20000000 , INVALIDATE = 0x0000000100000000 , CLEAN = 0x0000000200000000 , DST_POU = 0x0000001000000000 , DST_POC = 0x0000002000000000 , DST_BITS = 0x0000003000000000 , HTM_START = 0x0000010000000000 , HTM_COMMIT = 0x0000020000000000 , HTM_CANCEL = 0x0000040000000000 , HTM_ABORT = 0x0000080000000000 , TLBI = 0x0000100000000000 , TLBI_SYNC = 0x0000200000000000 , TLBI_EXT_SYNC = 0x0000400000000000 , TLBI_EXT_SYNC_COMP = 0x0000800000000000 , STICKY_FLAGS = INST_FETCH , HAS_NO_ADDR = 0x0001000000000000 } |

| enum | : CacheCoherenceFlagsType { I_CACHE_INV = 0x00000001 , INV_L1 = I_CACHE_INV , V_CACHE_INV = 0x00000002 , K_CACHE_INV = 0x00000004 , GL1_CACHE_INV = 0x00000008 , K_CACHE_WB = 0x00000010 , FLUSH_L2 = 0x00000020 , GL2_CACHE_INV = 0x00000040 , SLC_BIT = 0x00000080 , DLC_BIT = 0x00000100 , GLC_BIT = 0x00000200 , CACHED = 0x00000400 , READ_WRITE = 0x00000800 , SHARED = 0x00001000 } |

| These bits are used to set the coherence policy for the GPU and are encoded in the Vega instructions. More... | |

| typedef uint64_t | FlagsType |

| typedef uint8_t | ArchFlagsType |

| typedef gem5::Flags< FlagsType > | Flags |

| typedef uint64_t | CacheCoherenceFlagsType |

| typedef gem5::Flags< CacheCoherenceFlagsType > | CacheCoherenceFlags |

| using | LocalAccessor |

| enum | : RequestorID { wbRequestorId = 0 , funcRequestorId = 1 , intRequestorId = 2 , invldRequestorId = std::numeric_limits<RequestorID>::max() } |

| Requestor Ids that are statically allocated. More... | |

Public Member Functions | |

| Request () | |

| Minimal constructor. | |

| Request (Addr paddr, unsigned size, Flags flags, RequestorID id) | |

| Constructor for physical (e.g. | |

| Request (Addr vaddr, unsigned size, Flags flags, RequestorID id, Addr pc, ContextID cid, AtomicOpFunctorPtr atomic_op=nullptr) | |

| Request (const Request &other) | |

| ~Request () | |

| void | setContext (ContextID context_id) |

| Set up Context numbers. | |

| void | setStreamId (uint32_t sid) |

| void | setSubstreamId (uint32_t ssid) |

| void | setVirt (Addr vaddr, unsigned size, Flags flags, RequestorID id, Addr pc, AtomicOpFunctorPtr amo_op=nullptr) |

| Set up a virtual (e.g., CPU) request in a previously allocated Request object. | |

| void | setPaddr (Addr paddr) |

| Set just the physical address. | |

| void | splitOnVaddr (Addr split_addr, RequestPtr &req1, RequestPtr &req2) |

| Generate two requests as if this request had been split into two pieces. | |

| bool | hasPaddr () const |

| Accessor for paddr. | |

| Addr | getPaddr () const |

| bool | hasInstCount () const |

| Accessor for instruction count. | |

| Counter | getInstCount () const |

| void | setInstCount (Counter val) |

| bool | hasSize () const |

| Accessor for size. | |

| unsigned | getSize () const |

| const std::vector< bool > & | getByteEnable () const |

| void | setByteEnable (const std::vector< bool > &be) |

| bool | isMasked () const |

| Returns true if the memory request is masked, which means there is at least one byteEnable element which is false (byte is masked) | |

| Tick | time () const |

| Accessor for time. | |

| bool | isLocalAccess () |

| Is this request for a local memory mapped resource/register? | |

| void | setLocalAccessor (LocalAccessor acc) |

| Set the function which will enact that access. | |

| Cycles | localAccessor (ThreadContext *tc, Packet *pkt) |

| Perform the installed local access. | |

| bool | hasAtomicOpFunctor () |

| Accessor for atomic-op functor. | |

| AtomicOpFunctor * | getAtomicOpFunctor () |

| void | setAtomicOpFunctor (AtomicOpFunctorPtr amo_op) |

| bool | hasHtmAbortCause () const |

| Accessor for hardware transactional memory abort cause. | |

| HtmFailureFaultCause | getHtmAbortCause () const |

| void | setHtmAbortCause (HtmFailureFaultCause val) |

| Flags | getFlags () |

| Accessor for flags. | |

| void | setFlags (Flags flags) |

| Note that unlike other accessors, this function sets specific flags (ORs them in); it does not assign its argument to the _flags field. | |

| void | clearFlags (Flags flags) |

| void | setCacheCoherenceFlags (CacheCoherenceFlags extraFlags) |

| void | clearCacheCoherenceFlags (CacheCoherenceFlags extraFlags) |

| bool | hasVaddr () const |

| Accessor function for vaddr. | |

| Addr | getVaddr () const |

| RequestorID | requestorId () const |

| Accesssor for the requestor id. | |

| void | requestorId (RequestorID rid) |

| uint32_t | taskId () const |

| void | taskId (uint32_t id) |

| ArchFlagsType | getArchFlags () const |

| Accessor function for architecture-specific flags. | |

| bool | extraDataValid () const |

| Accessor function to check if sc result is valid. | |

| uint64_t | getExtraData () const |

| Accessor function for store conditional return value. | |

| void | setExtraData (uint64_t extraData) |

| Accessor function for store conditional return value. | |

| bool | hasContextId () const |

| ContextID | contextId () const |

| Accessor function for context ID. | |

| void | setSystemReq (bool sysReq) |

| bool | systemReq () const |

| bool | hasStreamId () const |

| uint32_t | streamId () const |

| bool | hasSubstreamId () const |

| uint32_t | substreamId () const |

| void | setPC (Addr pc) |

| bool | hasPC () const |

| Addr | getPC () const |

| Accessor function for pc. | |

| void | incAccessDepth () const |

| Increment/Get the depth at which this request is responded to. | |

| int | getAccessDepth () const |

| void | setTranslateLatency () |

| Set/Get the time taken for this request to be successfully translated. | |

| Tick | getTranslateLatency () const |

| void | setAccessLatency () |

| Set/Get the time taken to complete this request's access, not including the time to successfully translate the request. | |

| Tick | getAccessLatency () const |

| bool | hasInstSeqNum () const |

| Accessor for the sequence number of instruction that creates the request. | |

| InstSeqNum | getReqInstSeqNum () const |

| void | setReqInstSeqNum (const InstSeqNum seq_num) |

| bool | isUncacheable () const |

| Accessor functions for flags. | |

| bool | isStrictlyOrdered () const |

| bool | isInstFetch () const |

| bool | hasNoAddr () const |

| bool | isPrefetch () const |

| bool | isPrefetchEx () const |

| bool | isLLSC () const |

| bool | isPriv () const |

| bool | isLockedRMW () const |

| bool | isSwap () const |

| bool | isCondSwap () const |

| bool | isReadModifyWrite () const |

| bool | isSecure () const |

| bool | isPTWalk () const |

| bool | isRelease () const |

| bool | isKernel () const |

| bool | isAtomicReturn () const |

| bool | isAtomicNoReturn () const |

| bool | isHTMStart () const |

| bool | isHTMCommit () const |

| bool | isHTMCancel () const |

| bool | isHTMAbort () const |

| bool | isHTMCmd () const |

| bool | isTlbi () const |

| bool | isTlbiSync () const |

| bool | isTlbiExtSync () const |

| bool | isTlbiExtSyncComp () const |

| bool | isTlbiCmd () const |

| bool | isMemMgmt () const |

| bool | isAtomic () const |

| bool | isToPOU () const |

| Accessor functions for the destination of a memory request. | |

| bool | isToPOC () const |

| Flags | getDest () const |

| bool | isAcquire () const |

| bool | isGLCSet () const |

| Accessor functions for the cache bypass flags. | |

| bool | isSLCSet () const |

| bool | isInvL1 () const |

| Accessor functions for the memory space configuration flags and used by GPU ISAs such as the Heterogeneous System Architecture (HSA). | |

| bool | isInvL2 () const |

| bool | isGL2CacheFlush () const |

| void | setGPUFuncAccess (bool flag) |

| bool | getGPUFuncAccess () |

| bool | isCacheClean () const |

| Accessor functions to determine whether this request is part of a cache maintenance operation. | |

| bool | isCacheInvalidate () const |

| bool | isCacheMaintenance () const |

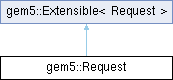

| Public Member Functions inherited from gem5::Extensible< Request > | |

| Extensible ()=default | |

| virtual | ~Extensible ()=default |

| void | setExtension (std::shared_ptr< T > ext) |

| Set a new extension to the packet and replace the old one, if there already exists the same type of extension in this packet. | |

| void | removeExtension (void) |

| Remove the extension based on its type. | |

| std::shared_ptr< T > | getExtension () |

| Get the extension pointer by linear search with the extensionID. | |

Static Public Member Functions | |

| static RequestPtr | createMemManagement (Flags flags, RequestorID id) |

| Factory method for creating memory management requests, with unspecified addr and size. | |

Public Attributes | |

| Tick | translateDelta = 0 |

| Time for the TLB/table walker to successfully translate this request. | |

| Tick | accessDelta = 0 |

| Access latency to complete this memory transaction not including translation time. | |

| int | depth = 0 |

| Level of the cache hierachy where this request was responded to (e.g. | |

Static Public Attributes | |

| static const FlagsType | STORE_NO_DATA |

| static const FlagsType | HTM_CMD |

| static const FlagsType | TLBI_CMD |

Private Types | |

| enum | : PrivateFlagsType { VALID_SIZE = 0x00000001 , VALID_PADDR = 0x00000002 , VALID_VADDR = 0x00000004 , VALID_INST_SEQ_NUM = 0x00000008 , VALID_PC = 0x00000010 , VALID_CONTEXT_ID = 0x00000020 , VALID_EXTRA_DATA = 0x00000080 , VALID_STREAM_ID = 0x00000100 , VALID_SUBSTREAM_ID = 0x00000200 , VALID_HTM_ABORT_CAUSE = 0x00000400 , VALID_INST_COUNT = 0x00000800 , STICKY_PRIVATE_FLAGS = VALID_CONTEXT_ID } |

| typedef uint16_t | PrivateFlagsType |

| typedef gem5::Flags< PrivateFlagsType > | PrivateFlags |

Private Attributes | |

| Addr | _paddr = 0 |

| The physical address of the request. | |

| unsigned | _size = 0 |

| The size of the request. | |

| std::vector< bool > | _byteEnable |

| Byte-enable mask for writes. | |

| RequestorID | _requestorId = invldRequestorId |

| The requestor ID which is unique in the system for all ports that are capable of issuing a transaction. | |

| Flags | _flags |

| Flag structure for the request. | |

| CacheCoherenceFlags | _cacheCoherenceFlags |

| Flags that control how downstream cache system maintains coherence. | |

| PrivateFlags | privateFlags |

| Private flags for field validity checking. | |

| Tick | _time = MaxTick |

| The time this request was started. | |

| uint32_t | _taskId = context_switch_task_id::Unknown |

| The task id associated with this request. | |

| uint32_t | _streamId = 0 |

| The stream ID uniquely identifies a device behind the SMMU/IOMMU Each transaction arriving at the SMMU/IOMMU is associated with exactly one stream ID. | |

| uint32_t | _substreamId = 0 |

| The substream ID identifies an "execution context" within a device behind an SMMU/IOMMU. | |

| bool | _systemReq = 0 |

| For fullsystem GPU simulation, this determines if a requests destination is system (host) memory or dGPU (device) memory. | |

| Addr | _vaddr = MaxAddr |

| The virtual address of the request. | |

| uint64_t | _extraData = 0 |

| Extra data for the request, such as the return value of store conditional or the compare value for a CAS. | |

| ContextID | _contextId = InvalidContextID |

| The context ID (for statistics, locks, and wakeups). | |

| Addr | _pc = MaxAddr |

| program counter of initiating access; for tracing/debugging | |

| InstSeqNum | _reqInstSeqNum = 0 |

| Sequence number of the instruction that creates the request. | |

| AtomicOpFunctorPtr | atomicOpFunctor = nullptr |

| A pointer to an atomic operation. | |

| LocalAccessor | _localAccessor |

| Counter | _instCount = 0 |

| The instruction count at the time this request is created. | |

| HtmFailureFaultCause | _htmAbortCause = HtmFailureFaultCause::INVALID |

| The cause for HTM transaction abort. | |

| bool | _isGPUFuncAccess |

Additional Inherited Members | |

| Protected Member Functions inherited from gem5::Extensible< Request > | |

| std::list< std::shared_ptr< ExtensionBase > >::iterator | findExtension () |

| Go through the extension list and return the iterator to the instance of the type of extension. | |

| Protected Attributes inherited from gem5::Extensible< Request > | |

| std::list< std::shared_ptr< ExtensionBase > > | extensions |

Detailed Description

Definition at line 97 of file request.hh.

Member Typedef Documentation

◆ ArchFlagsType

| typedef uint8_t gem5::Request::ArchFlagsType |

Definition at line 101 of file request.hh.

◆ CacheCoherenceFlags

Definition at line 294 of file request.hh.

◆ CacheCoherenceFlagsType

| typedef uint64_t gem5::Request::CacheCoherenceFlagsType |

Definition at line 293 of file request.hh.

◆ Flags

| typedef gem5::Flags<FlagsType> gem5::Request::Flags |

Definition at line 102 of file request.hh.

◆ FlagsType

| typedef uint64_t gem5::Request::FlagsType |

Definition at line 100 of file request.hh.

◆ LocalAccessor

Definition at line 345 of file request.hh.

◆ PrivateFlags

|

private |

Definition at line 350 of file request.hh.

◆ PrivateFlagsType

|

private |

Definition at line 349 of file request.hh.

Member Enumeration Documentation

◆ anonymous enum

| anonymous enum : CacheCoherenceFlagsType |

These bits are used to set the coherence policy for the GPU and are encoded in the Vega instructions.

The Vega ISA defines two cache levels See the AMD Vega ISA Architecture Manual for more details.

INV_L1: L1 cache invalidation FLUSH_L2: L2 cache flush

Invalidation means to simply discard all cache contents. This can be done in the L1 since it is implemented as a write-through cache and there are other copies elsewhere in the hierarchy.

For flush the contents of the cache need to be written back to memory when dirty and can be discarded otherwise. This operation is more involved than invalidation and therefore we do not flush caches with redundant copies of data.

SLC: System Level Coherent. Accesses are forced to miss in the L2 cache and are coherent with system memory.

GLC: Globally Coherent. Controls how reads and writes are handled by the L1 cache. Global here referes to the data being visible globally on the GPU (i.e., visible to all WGs).

For atomics, the GLC bit is used to distinguish between between atomic return/no-return operations. These flags are used by GPUDynInst.

| Enumerator | |

|---|---|

| I_CACHE_INV | mem_sync_op flags |

| INV_L1 | |

| V_CACHE_INV | |

| K_CACHE_INV | |

| GL1_CACHE_INV | |

| K_CACHE_WB | |

| FLUSH_L2 | |

| GL2_CACHE_INV | |

| SLC_BIT | user-policy flags |

| DLC_BIT | |

| GLC_BIT | |

| CACHED | mtype flags |

| READ_WRITE | |

| SHARED | |

Definition at line 323 of file request.hh.

◆ anonymous enum

| anonymous enum : FlagsType |

| Enumerator | |

|---|---|

| ARCH_BITS | Architecture specific flags. These bits int the flag field are reserved for architecture-specific code. For example, SPARC uses them to represent ASIs. |

| INST_FETCH | The request was an instruction fetch. |

| PHYSICAL | The virtual address is also the physical address. |

| UNCACHEABLE | The request is to an uncacheable address.

|

| STRICT_ORDER | The request is required to be strictly ordered by CPU models and is non-speculative. A strictly ordered request is guaranteed to never be re-ordered or executed speculatively by a CPU model. The memory system may still reorder requests in caches unless the UNCACHEABLE flag is set as well. |

| PRIVILEGED | This request is made in privileged mode. |

| CACHE_BLOCK_ZERO | This is a write that is targeted and zeroing an entire cache block. There is no need for a read/modify/write |

| NO_ACCESS | The request should not cause a memory access. |

| LOCKED_RMW | This request will lock or unlock the accessed memory. When used with a load, the access locks the particular chunk of memory. When used with a store, it unlocks. The rule is that locked accesses have to be made up of a locked load, some operation on the data, and then a locked store. |

| LLSC | The request is a Load locked/store conditional. |

| MEM_SWAP | This request is for a memory swap. |

| MEM_SWAP_COND | |

| READ_MODIFY_WRITE | This request is a read which will be followed by a write. |

| PREFETCH | The request is a prefetch. |

| PF_EXCLUSIVE | The request should be prefetched into the exclusive state. |

| EVICT_NEXT | The request should be marked as LRU. |

| ACQUIRE | The request should be marked with ACQUIRE. |

| RELEASE | The request should be marked with RELEASE. |

| ATOMIC_RETURN_OP | The request is an atomic that returns data. |

| ATOMIC_NO_RETURN_OP | The request is an atomic that does not return data. |

| KERNEL | The request should be marked with KERNEL. Used to indicate the synchronization associated with a GPU kernel launch or completion. |

| SECURE | The request targets the secure memory space. |

| PT_WALK | The request is a page table walk. |

| INVALIDATE | The request invalidates a memory location. |

| CLEAN | The request cleans a memory location. |

| DST_POU | The request targets the point of unification. |

| DST_POC | The request targets the point of coherence. |

| DST_BITS | Bits to define the destination of a request. |

| HTM_START | hardware transactional memory The request starts a HTM transaction |

| HTM_COMMIT | The request commits a HTM transaction. |

| HTM_CANCEL | The request cancels a HTM transaction. |

| HTM_ABORT | The request aborts a HTM transaction. |

| TLBI | |

| TLBI_SYNC | |

| TLBI_EXT_SYNC | The Request tells the CPU model that a remote TLB Sync has been requested. |

| TLBI_EXT_SYNC_COMP | The Request tells the interconnect that a remote TLB Sync request has completed. |

| STICKY_FLAGS | These flags are not cleared when a Request object is reused (assigned a new address). |

| HAS_NO_ADDR | TLBI_EXT_SYNC_COMP seems to be the largest value of FlagsType, so HAS_NO_ADDR's value is that << 1. |

Definition at line 104 of file request.hh.

◆ anonymous enum

|

private |

| Enumerator | |

|---|---|

| VALID_SIZE | Whether or not the size is valid. |

| VALID_PADDR | Whether or not paddr is valid (has been written yet). |

| VALID_VADDR | Whether or not the vaddr is valid. |

| VALID_INST_SEQ_NUM | Whether or not the instruction sequence number is valid. |

| VALID_PC | Whether or not the pc is valid. |

| VALID_CONTEXT_ID | Whether or not the context ID is valid. |

| VALID_EXTRA_DATA | Whether or not the sc result is valid. |

| VALID_STREAM_ID | Whether or not the stream ID and substream ID is valid. |

| VALID_SUBSTREAM_ID | |

| VALID_HTM_ABORT_CAUSE | Whether or not the abort cause is valid. |

| VALID_INST_COUNT | Whether or not the instruction count is valid. |

| STICKY_PRIVATE_FLAGS | These flags are not cleared when a Request object is reused (assigned a new address). |

Definition at line 352 of file request.hh.

◆ anonymous enum

| anonymous enum : RequestorID |

Requestor Ids that are statically allocated.

Definition at line 274 of file request.hh.

Constructor & Destructor Documentation

◆ Request() [1/4]

|

inline |

Minimal constructor.

No fields are initialized. (Note that _flags and privateFlags are cleared by Flags default constructor.)

Definition at line 485 of file request.hh.

Referenced by Request().

◆ Request() [2/4]

|

inline |

Constructor for physical (e.g.

device) requests. Initializes just physical address, size, flags, and timestamp (to curTick()). These fields are adequate to perform a request.

Definition at line 492 of file request.hh.

References _byteEnable, _flags, _isGPUFuncAccess, _paddr, _requestorId, _size, _time, gem5::curTick(), gem5::ArmISA::id, privateFlags, VALID_PADDR, and VALID_SIZE.

◆ Request() [3/4]

|

inline |

Definition at line 501 of file request.hh.

References _byteEnable, _isGPUFuncAccess, gem5::MipsISA::pc, setContext(), setVirt(), and gem5::MipsISA::vaddr.

◆ Request() [4/4]

|

inline |

Definition at line 511 of file request.hh.

References _byteEnable, _cacheCoherenceFlags, _contextId, _extraData, _flags, _localAccessor, _paddr, _pc, _reqInstSeqNum, _requestorId, _size, _taskId, _time, _vaddr, accessDelta, atomicOpFunctor, depth, gem5::Extensible< Request >::Extensible(), privateFlags, Request(), and translateDelta.

◆ ~Request()

|

inline |

Definition at line 531 of file request.hh.

Member Function Documentation

◆ clearCacheCoherenceFlags()

|

inline |

Definition at line 833 of file request.hh.

References _cacheCoherenceFlags, hasPaddr(), and hasVaddr().

◆ clearFlags()

|

inline |

Definition at line 818 of file request.hh.

References _flags, hasPaddr(), and hasVaddr().

◆ contextId()

|

inline |

Accessor function for context ID.

Definition at line 917 of file request.hh.

References _contextId, and hasContextId().

◆ createMemManagement()

|

inlinestatic |

Factory method for creating memory management requests, with unspecified addr and size.

Definition at line 538 of file request.hh.

References gem5::curTick(), and gem5::ArmISA::id.

Referenced by gem5::o3::LSQ::checkStaleTranslations(), and gem5::TimingSimpleCPU::DcachePort::recvTimingSnoopReq().

◆ extraDataValid()

|

inline |

Accessor function to check if sc result is valid.

Definition at line 888 of file request.hh.

References privateFlags, and VALID_EXTRA_DATA.

Referenced by getExtraData().

◆ getAccessDepth()

|

inline |

Definition at line 979 of file request.hh.

References depth.

◆ getAccessLatency()

|

inline |

Definition at line 992 of file request.hh.

References accessDelta.

◆ getArchFlags()

|

inline |

Accessor function for architecture-specific flags.

Definition at line 880 of file request.hh.

References _flags, ARCH_BITS, hasPaddr(), and hasVaddr().

◆ getAtomicOpFunctor()

|

inline |

Definition at line 761 of file request.hh.

References atomicOpFunctor.

◆ getByteEnable()

|

inline |

Definition at line 706 of file request.hh.

References _byteEnable.

◆ getDest()

|

inline |

Definition at line 1086 of file request.hh.

◆ getExtraData()

|

inline |

Accessor function for store conditional return value.

Definition at line 895 of file request.hh.

References _extraData, and extraDataValid().

◆ getFlags()

|

inline |

Accessor for flags.

Definition at line 800 of file request.hh.

References _flags, hasPaddr(), and hasVaddr().

◆ getGPUFuncAccess()

|

inline |

Definition at line 1138 of file request.hh.

References _isGPUFuncAccess.

◆ getHtmAbortCause()

|

inline |

Definition at line 784 of file request.hh.

References _htmAbortCause, and hasHtmAbortCause().

◆ getInstCount()

|

inline |

Definition at line 660 of file request.hh.

References _instCount, and hasInstCount().

◆ getPaddr()

|

inline |

Definition at line 645 of file request.hh.

References _paddr, and hasPaddr().

◆ getPC()

|

inline |

◆ getReqInstSeqNum()

|

inline |

Definition at line 1005 of file request.hh.

References _reqInstSeqNum, and hasInstSeqNum().

◆ getSize()

|

inline |

Definition at line 699 of file request.hh.

◆ getTranslateLatency()

|

inline |

Definition at line 985 of file request.hh.

References translateDelta.

◆ getVaddr()

|

inline |

Definition at line 848 of file request.hh.

References _vaddr, privateFlags, and VALID_VADDR.

◆ hasAtomicOpFunctor()

|

inline |

Accessor for atomic-op functor.

Definition at line 755 of file request.hh.

References atomicOpFunctor.

◆ hasContextId()

|

inline |

Definition at line 910 of file request.hh.

References privateFlags, and VALID_CONTEXT_ID.

Referenced by contextId().

◆ hasHtmAbortCause()

|

inline |

Accessor for hardware transactional memory abort cause.

Definition at line 778 of file request.hh.

References privateFlags, and VALID_HTM_ABORT_CAUSE.

Referenced by getHtmAbortCause().

◆ hasInstCount()

|

inline |

Accessor for instruction count.

Definition at line 655 of file request.hh.

References privateFlags, and VALID_INST_COUNT.

Referenced by getInstCount().

◆ hasInstSeqNum()

|

inline |

Accessor for the sequence number of instruction that creates the request.

Definition at line 999 of file request.hh.

References privateFlags, and VALID_INST_SEQ_NUM.

Referenced by getReqInstSeqNum().

◆ hasNoAddr()

|

inline |

Definition at line 1023 of file request.hh.

References _flags, and HAS_NO_ADDR.

◆ hasPaddr()

|

inline |

Accessor for paddr.

Definition at line 639 of file request.hh.

References privateFlags, and VALID_PADDR.

Referenced by clearCacheCoherenceFlags(), clearFlags(), getArchFlags(), getFlags(), getPaddr(), setCacheCoherenceFlags(), setFlags(), splitOnVaddr(), and time().

◆ hasPC()

|

inline |

Definition at line 961 of file request.hh.

References privateFlags, and VALID_PC.

Referenced by getPC().

◆ hasSize()

|

inline |

Accessor for size.

Definition at line 693 of file request.hh.

References privateFlags, and VALID_SIZE.

Referenced by getSize().

◆ hasStreamId()

|

inline |

Definition at line 928 of file request.hh.

References privateFlags, and VALID_STREAM_ID.

Referenced by setSubstreamId(), and streamId().

◆ hasSubstreamId()

|

inline |

Definition at line 941 of file request.hh.

References privateFlags, and VALID_SUBSTREAM_ID.

Referenced by substreamId().

◆ hasVaddr()

|

inline |

Accessor function for vaddr.

Definition at line 842 of file request.hh.

References privateFlags, and VALID_VADDR.

Referenced by clearCacheCoherenceFlags(), clearFlags(), getArchFlags(), getFlags(), setCacheCoherenceFlags(), setFlags(), splitOnVaddr(), and time().

◆ incAccessDepth()

|

inline |

Increment/Get the depth at which this request is responded to.

This currently happens when the request misses in any cache level.

Definition at line 978 of file request.hh.

References depth.

◆ isAcquire()

|

inline |

Definition at line 1088 of file request.hh.

References _cacheCoherenceFlags, and ACQUIRE.

◆ isAtomic()

|

inline |

Definition at line 1071 of file request.hh.

References _flags, ATOMIC_NO_RETURN_OP, and ATOMIC_RETURN_OP.

◆ isAtomicNoReturn()

|

inline |

Definition at line 1045 of file request.hh.

References _flags, and ATOMIC_NO_RETURN_OP.

◆ isAtomicReturn()

|

inline |

Definition at line 1044 of file request.hh.

References _flags, and ATOMIC_RETURN_OP.

◆ isCacheClean()

|

inline |

Accessor functions to determine whether this request is part of a cache maintenance operation.

At the moment three operations are supported:

1) A cache clean operation updates all copies of a memory location to the point of reference, 2) A cache invalidate operation invalidates all copies of the specified block in the memory above the point of reference, 3) A clean and invalidate operation is a combination of the two operations.

Definition at line 1127 of file request.hh.

◆ isCacheInvalidate()

|

inline |

Definition at line 1128 of file request.hh.

References _flags, and INVALIDATE.

◆ isCacheMaintenance()

|

inline |

Definition at line 1129 of file request.hh.

References _flags, CLEAN, and INVALIDATE.

◆ isCondSwap()

|

inline |

Definition at line 1034 of file request.hh.

References _flags, and MEM_SWAP_COND.

◆ isGL2CacheFlush()

|

inline |

Definition at line 1110 of file request.hh.

References _cacheCoherenceFlags, and FLUSH_L2.

◆ isGLCSet()

|

inline |

Accessor functions for the cache bypass flags.

The cache bypass can specify which levels in the hierarchy to bypass. If GLC_BIT is set, the requests are globally coherent and bypass TCP. If SLC_BIT is set, then the requests are system level coherent and bypass both TCP and TCC.

Definition at line 1098 of file request.hh.

References _cacheCoherenceFlags, and GLC_BIT.

◆ isHTMAbort()

|

inline |

Definition at line 1050 of file request.hh.

References _flags, and HTM_ABORT.

Referenced by isHTMCmd(), and setHtmAbortCause().

◆ isHTMCancel()

|

inline |

Definition at line 1049 of file request.hh.

References _flags, and HTM_CANCEL.

Referenced by isHTMCmd().

◆ isHTMCmd()

|

inline |

Definition at line 1052 of file request.hh.

References isHTMAbort(), isHTMCancel(), isHTMCommit(), and isHTMStart().

Referenced by isMemMgmt().

◆ isHTMCommit()

|

inline |

Definition at line 1048 of file request.hh.

References _flags, and HTM_COMMIT.

Referenced by isHTMCmd().

◆ isHTMStart()

|

inline |

Definition at line 1047 of file request.hh.

References _flags, and HTM_START.

Referenced by isHTMCmd().

◆ isInstFetch()

|

inline |

Definition at line 1022 of file request.hh.

References _flags, and INST_FETCH.

◆ isInvL1()

|

inline |

Accessor functions for the memory space configuration flags and used by GPU ISAs such as the Heterogeneous System Architecture (HSA).

Note that setting extraFlags should be done via setCacheCoherenceFlags().

Definition at line 1106 of file request.hh.

References _cacheCoherenceFlags, and INV_L1.

◆ isInvL2()

|

inline |

Definition at line 1107 of file request.hh.

References _cacheCoherenceFlags, and GL2_CACHE_INV.

◆ isKernel()

|

inline |

Definition at line 1043 of file request.hh.

◆ isLLSC()

|

inline |

Definition at line 1030 of file request.hh.

◆ isLocalAccess()

|

inline |

Is this request for a local memory mapped resource/register?

Definition at line 741 of file request.hh.

References _localAccessor.

◆ isLockedRMW()

|

inline |

Definition at line 1032 of file request.hh.

References _flags, and LOCKED_RMW.

◆ isMasked()

|

inline |

Returns true if the memory request is masked, which means there is at least one byteEnable element which is false (byte is masked)

Definition at line 724 of file request.hh.

References _byteEnable.

◆ isMemMgmt()

|

inline |

Definition at line 1068 of file request.hh.

References isHTMCmd(), and isTlbiCmd().

◆ isPrefetch()

|

inline |

Definition at line 1025 of file request.hh.

References _flags, PF_EXCLUSIVE, and PREFETCH.

◆ isPrefetchEx()

|

inline |

Definition at line 1029 of file request.hh.

References _flags, and PF_EXCLUSIVE.

◆ isPriv()

|

inline |

Definition at line 1031 of file request.hh.

References _flags, and PRIVILEGED.

◆ isPTWalk()

|

inline |

Definition at line 1041 of file request.hh.

◆ isReadModifyWrite()

|

inline |

Definition at line 1036 of file request.hh.

References _flags, LOCKED_RMW, and READ_MODIFY_WRITE.

◆ isRelease()

|

inline |

Definition at line 1042 of file request.hh.

◆ isSecure()

|

inline |

Definition at line 1040 of file request.hh.

◆ isSLCSet()

|

inline |

Definition at line 1099 of file request.hh.

References _cacheCoherenceFlags, and SLC_BIT.

◆ isStrictlyOrdered()

|

inline |

Definition at line 1021 of file request.hh.

References _flags, and STRICT_ORDER.

◆ isSwap()

|

inline |

Definition at line 1033 of file request.hh.

References _flags, MEM_SWAP, and MEM_SWAP_COND.

◆ isTlbi()

|

inline |

◆ isTlbiCmd()

|

inline |

Definition at line 1063 of file request.hh.

References isTlbi(), isTlbiExtSync(), isTlbiExtSyncComp(), and isTlbiSync().

Referenced by isMemMgmt().

◆ isTlbiExtSync()

|

inline |

Definition at line 1060 of file request.hh.

References _flags, and TLBI_EXT_SYNC.

Referenced by isTlbiCmd().

◆ isTlbiExtSyncComp()

|

inline |

Definition at line 1061 of file request.hh.

References _flags, and TLBI_EXT_SYNC_COMP.

Referenced by isTlbiCmd().

◆ isTlbiSync()

|

inline |

Definition at line 1059 of file request.hh.

References _flags, and TLBI_SYNC.

Referenced by isTlbiCmd().

◆ isToPOC()

|

inline |

Definition at line 1085 of file request.hh.

◆ isToPOU()

|

inline |

Accessor functions for the destination of a memory request.

The destination flag can specify a point of reference for the operation (e.g. a cache block clean to the the point of unification). At the moment the destination is only used by the cache maintenance operations.

Definition at line 1084 of file request.hh.

◆ isUncacheable()

|

inline |

Accessor functions for flags.

Note that these are for testing only; setting flags should be done via setFlags().

Definition at line 1020 of file request.hh.

References _flags, and UNCACHEABLE.

◆ localAccessor()

|

inline |

Perform the installed local access.

Definition at line 746 of file request.hh.

References _localAccessor.

◆ requestorId() [1/2]

|

inline |

◆ requestorId() [2/2]

|

inline |

Definition at line 862 of file request.hh.

References _requestorId.

◆ setAccessLatency()

|

inline |

Set/Get the time taken to complete this request's access, not including the time to successfully translate the request.

Definition at line 991 of file request.hh.

References _time, accessDelta, gem5::curTick(), and translateDelta.

◆ setAtomicOpFunctor()

|

inline |

Definition at line 768 of file request.hh.

References atomicOpFunctor.

◆ setByteEnable()

|

inline |

Definition at line 712 of file request.hh.

References _byteEnable, _size, and gem5::MipsISA::be.

◆ setCacheCoherenceFlags()

|

inline |

Definition at line 825 of file request.hh.

References _cacheCoherenceFlags, hasPaddr(), and hasVaddr().

◆ setContext()

|

inline |

Set up Context numbers.

Definition at line 553 of file request.hh.

References _contextId, privateFlags, and VALID_CONTEXT_ID.

Referenced by Request().

◆ setExtraData()

|

inline |

Accessor function for store conditional return value.

Definition at line 903 of file request.hh.

References _extraData, privateFlags, and VALID_EXTRA_DATA.

◆ setFlags()

|

inline |

Note that unlike other accessors, this function sets specific flags (ORs them in); it does not assign its argument to the _flags field.

Thus this method should rightly be called setFlags() and not just flags().

Definition at line 811 of file request.hh.

References _flags, hasPaddr(), and hasVaddr().

◆ setGPUFuncAccess()

|

inline |

Definition at line 1133 of file request.hh.

References _isGPUFuncAccess.

◆ setHtmAbortCause()

|

inline |

Definition at line 791 of file request.hh.

References _htmAbortCause, isHTMAbort(), privateFlags, gem5::X86ISA::val, and VALID_HTM_ABORT_CAUSE.

◆ setInstCount()

|

inline |

Definition at line 666 of file request.hh.

References _instCount, privateFlags, gem5::X86ISA::val, and VALID_INST_COUNT.

◆ setLocalAccessor()

|

inline |

Set the function which will enact that access.

Definition at line 743 of file request.hh.

References _localAccessor.

◆ setPaddr()

|

inline |

Set just the physical address.

This usually used to record the result of a translation.

Definition at line 604 of file request.hh.

References _paddr, privateFlags, and VALID_PADDR.

◆ setPC()

|

inline |

Definition at line 954 of file request.hh.

References _pc, gem5::MipsISA::pc, privateFlags, and VALID_PC.

◆ setReqInstSeqNum()

|

inline |

Definition at line 1012 of file request.hh.

References _reqInstSeqNum, privateFlags, and VALID_INST_SEQ_NUM.

◆ setStreamId()

|

inline |

Definition at line 560 of file request.hh.

References _streamId, privateFlags, and VALID_STREAM_ID.

◆ setSubstreamId()

|

inline |

Definition at line 567 of file request.hh.

References _substreamId, hasStreamId(), privateFlags, and VALID_SUBSTREAM_ID.

◆ setSystemReq()

|

inline |

Definition at line 924 of file request.hh.

References _systemReq.

◆ setTranslateLatency()

|

inline |

Set/Get the time taken for this request to be successfully translated.

Definition at line 984 of file request.hh.

References _time, gem5::curTick(), and translateDelta.

◆ setVirt()

|

inline |

Set up a virtual (e.g., CPU) request in a previously allocated Request object.

Definition at line 579 of file request.hh.

References _flags, _localAccessor, _pc, _requestorId, _size, _time, _vaddr, accessDelta, atomicOpFunctor, gem5::curTick(), depth, gem5::ArmISA::id, gem5::MipsISA::pc, privateFlags, STICKY_FLAGS, STICKY_PRIVATE_FLAGS, translateDelta, gem5::MipsISA::vaddr, VALID_PC, VALID_SIZE, and VALID_VADDR.

Referenced by Request().

◆ splitOnVaddr()

|

inline |

Generate two requests as if this request had been split into two pieces.

The original request can't have been translated already.

Definition at line 617 of file request.hh.

References _byteEnable, _size, _vaddr, hasPaddr(), and hasVaddr().

◆ streamId()

|

inline |

Definition at line 934 of file request.hh.

References _streamId, and hasStreamId().

◆ substreamId()

|

inline |

Definition at line 947 of file request.hh.

References _substreamId, and hasSubstreamId().

◆ systemReq()

|

inline |

Definition at line 925 of file request.hh.

References _systemReq.

◆ taskId() [1/2]

|

inline |

Definition at line 868 of file request.hh.

References _taskId.

◆ taskId() [2/2]

|

inline |

Definition at line 874 of file request.hh.

References _taskId, and gem5::ArmISA::id.

◆ time()

|

inline |

Accessor for time.

Definition at line 734 of file request.hh.

References _time, hasPaddr(), and hasVaddr().

Member Data Documentation

◆ _byteEnable

|

private |

Byte-enable mask for writes.

Definition at line 399 of file request.hh.

Referenced by getByteEnable(), isMasked(), Request(), Request(), Request(), setByteEnable(), and splitOnVaddr().

◆ _cacheCoherenceFlags

|

private |

Flags that control how downstream cache system maintains coherence.

Definition at line 410 of file request.hh.

Referenced by clearCacheCoherenceFlags(), isAcquire(), isGL2CacheFlush(), isGLCSet(), isInvL1(), isInvL2(), isSLCSet(), Request(), and setCacheCoherenceFlags().

◆ _contextId

|

private |

The context ID (for statistics, locks, and wakeups).

Definition at line 457 of file request.hh.

Referenced by contextId(), Request(), and setContext().

◆ _extraData

|

private |

Extra data for the request, such as the return value of store conditional or the compare value for a CAS.

Definition at line 454 of file request.hh.

Referenced by getExtraData(), Request(), and setExtraData().

◆ _flags

|

private |

Flag structure for the request.

Definition at line 407 of file request.hh.

Referenced by clearFlags(), getArchFlags(), getDest(), getFlags(), hasNoAddr(), isAtomic(), isAtomicNoReturn(), isAtomicReturn(), isCacheClean(), isCacheInvalidate(), isCacheMaintenance(), isCondSwap(), isHTMAbort(), isHTMCancel(), isHTMCommit(), isHTMStart(), isInstFetch(), isKernel(), isLLSC(), isLockedRMW(), isPrefetch(), isPrefetchEx(), isPriv(), isPTWalk(), isReadModifyWrite(), isRelease(), isSecure(), isStrictlyOrdered(), isSwap(), isTlbi(), isTlbiExtSync(), isTlbiExtSyncComp(), isTlbiSync(), isToPOC(), isToPOU(), isUncacheable(), Request(), Request(), setFlags(), and setVirt().

◆ _htmAbortCause

|

private |

The cause for HTM transaction abort.

Definition at line 474 of file request.hh.

Referenced by getHtmAbortCause(), and setHtmAbortCause().

◆ _instCount

|

private |

The instruction count at the time this request is created.

Definition at line 471 of file request.hh.

Referenced by getInstCount(), and setInstCount().

◆ _isGPUFuncAccess

|

private |

Definition at line 476 of file request.hh.

Referenced by getGPUFuncAccess(), Request(), Request(), and setGPUFuncAccess().

◆ _localAccessor

|

private |

Definition at line 468 of file request.hh.

Referenced by isLocalAccess(), localAccessor(), Request(), setLocalAccessor(), and setVirt().

◆ _paddr

|

private |

The physical address of the request.

Valid only if validPaddr is set.

Definition at line 389 of file request.hh.

Referenced by getPaddr(), Request(), Request(), and setPaddr().

◆ _pc

◆ _reqInstSeqNum

|

private |

Sequence number of the instruction that creates the request.

Definition at line 463 of file request.hh.

Referenced by getReqInstSeqNum(), Request(), and setReqInstSeqNum().

◆ _requestorId

|

private |

The requestor ID which is unique in the system for all ports that are capable of issuing a transaction.

Definition at line 404 of file request.hh.

Referenced by Request(), Request(), requestorId(), requestorId(), and setVirt().

◆ _size

|

private |

The size of the request.

This field must be set when vaddr or paddr is written via setVirt() or a phys basec constructor, so it is always valid as long as one of the address fields is valid.

Definition at line 396 of file request.hh.

Referenced by getSize(), Request(), Request(), setByteEnable(), setVirt(), and splitOnVaddr().

◆ _streamId

|

private |

The stream ID uniquely identifies a device behind the SMMU/IOMMU Each transaction arriving at the SMMU/IOMMU is associated with exactly one stream ID.

Definition at line 432 of file request.hh.

Referenced by setStreamId(), and streamId().

◆ _substreamId

|

private |

The substream ID identifies an "execution context" within a device behind an SMMU/IOMMU.

It's intended to map 1-to-1 to PCIe PASID (Process Address Space ID). The presence of a substream ID is optional.

Definition at line 440 of file request.hh.

Referenced by setSubstreamId(), and substreamId().

◆ _systemReq

|

private |

For fullsystem GPU simulation, this determines if a requests destination is system (host) memory or dGPU (device) memory.

Definition at line 446 of file request.hh.

Referenced by setSystemReq(), and systemReq().

◆ _taskId

|

private |

The task id associated with this request.

Definition at line 425 of file request.hh.

◆ _time

The time this request was started.

Used to calculate latencies. This field is set to curTick() any time paddr or vaddr is written.

Definition at line 420 of file request.hh.

Referenced by Request(), Request(), setAccessLatency(), setTranslateLatency(), setVirt(), and time().

◆ _vaddr

The virtual address of the request.

Definition at line 449 of file request.hh.

Referenced by getVaddr(), Request(), setVirt(), and splitOnVaddr().

◆ accessDelta

| Tick gem5::Request::accessDelta = 0 |

Access latency to complete this memory transaction not including translation time.

Definition at line 681 of file request.hh.

Referenced by getAccessLatency(), Request(), setAccessLatency(), and setVirt().

◆ atomicOpFunctor

|

private |

A pointer to an atomic operation.

Definition at line 466 of file request.hh.

Referenced by getAtomicOpFunctor(), hasAtomicOpFunctor(), Request(), setAtomicOpFunctor(), and setVirt().

◆ depth

|

mutable |

Level of the cache hierachy where this request was responded to (e.g.

0 = L1; 1 = L2).

Definition at line 687 of file request.hh.

Referenced by getAccessDepth(), incAccessDepth(), Request(), and setVirt().

◆ HTM_CMD

|

static |

Definition at line 266 of file request.hh.

Referenced by gem5::o3::LSQ::pushRequest().

◆ privateFlags

|

private |

Private flags for field validity checking.

Definition at line 413 of file request.hh.

Referenced by extraDataValid(), getVaddr(), hasContextId(), hasHtmAbortCause(), hasInstCount(), hasInstSeqNum(), hasPaddr(), hasPC(), hasSize(), hasStreamId(), hasSubstreamId(), hasVaddr(), Request(), Request(), setContext(), setExtraData(), setHtmAbortCause(), setInstCount(), setPaddr(), setPC(), setReqInstSeqNum(), setStreamId(), setSubstreamId(), and setVirt().

◆ STORE_NO_DATA

|

static |

Definition at line 263 of file request.hh.

Referenced by gem5::minor::LSQ::pushRequest(), gem5::o3::LSQUnit::write(), gem5::AtomicSimpleCPU::writeMem(), gem5::CheckerCPU::writeMem(), and gem5::TimingSimpleCPU::writeMem().

◆ TLBI_CMD

|

static |

Definition at line 269 of file request.hh.

Referenced by gem5::o3::LSQ::pushRequest().

◆ translateDelta

| Tick gem5::Request::translateDelta = 0 |

Time for the TLB/table walker to successfully translate this request.

Definition at line 675 of file request.hh.

Referenced by getTranslateLatency(), Request(), setAccessLatency(), setTranslateLatency(), and setVirt().

The documentation for this class was generated from the following file:

- mem/request.hh

Generated on Sat Oct 18 2025 08:06:53 for gem5 by doxygen 1.14.0