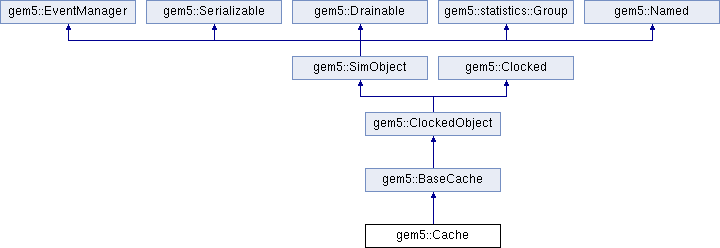

A coherent cache that can be arranged in flexible topologies. More...

#include <cache.hh>

Public Member Functions | |

| Cache (const CacheParams &p) | |

| Instantiates a basic cache object. | |

| bool | sendMSHRQueuePacket (MSHR *mshr) override |

| Take an MSHR, turn it into a suitable downstream packet, and send it out. | |

| Public Member Functions inherited from gem5::BaseCache | |

| void | regProbePoints () override |

| Registers probes. | |

| BaseCache (const BaseCacheParams &p, unsigned blk_size) | |

| ~BaseCache () | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| unsigned | getBlockSize () const |

| Query block size of a cache. | |

| const AddrRangeList & | getAddrRanges () const |

| MSHR * | allocateMissBuffer (PacketPtr pkt, Tick time, bool sched_send=true) |

| void | allocateWriteBuffer (PacketPtr pkt, Tick time) |

| bool | isBlocked () const |

| Returns true if the cache is blocked for accesses. | |

| void | setBlocked (BlockedCause cause) |

| Marks the access path of the cache as blocked for the given cause. | |

| void | clearBlocked (BlockedCause cause) |

| Marks the cache as unblocked for the given cause. | |

| void | schedMemSideSendEvent (Tick time) |

| Schedule a send event for the memory-side port. | |

| bool | inCache (Addr addr, bool is_secure) const |

| bool | hasBeenPrefetched (Addr addr, bool is_secure) const |

| bool | hasBeenPrefetched (Addr addr, bool is_secure, RequestorID requestor) const |

| bool | inMissQueue (Addr addr, bool is_secure) const |

| void | incMissCount (PacketPtr pkt) |

| void | incHitCount (PacketPtr pkt) |

| bool | coalesce () const |

| Checks if the cache is coalescing writes. | |

| void | writebackVisitor (CacheBlk &blk) |

| Cache block visitor that writes back dirty cache blocks using functional writes. | |

| void | invalidateVisitor (CacheBlk &blk) |

| Cache block visitor that invalidates all blocks in the cache. | |

| bool | sendWriteQueuePacket (WriteQueueEntry *wq_entry) |

| Similar to sendMSHR, but for a write-queue entry instead. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize the state of the caches. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| void | promoteWholeLineWrites (PacketPtr pkt) |

| Turn line-sized writes into WriteInvalidate transactions. | |

| bool | access (PacketPtr pkt, CacheBlk *&blk, Cycles &lat, PacketList &writebacks) override |

| Does all the processing necessary to perform the provided request. | |

| void | handleTimingReqHit (PacketPtr pkt, CacheBlk *blk, Tick request_time) override |

| void | handleTimingReqMiss (PacketPtr pkt, CacheBlk *blk, Tick forward_time, Tick request_time) override |

| void | recvTimingReq (PacketPtr pkt) override |

| Performs the access specified by the request. | |

| void | doWritebacks (PacketList &writebacks, Tick forward_time) override |

| Insert writebacks into the write buffer. | |

| void | doWritebacksAtomic (PacketList &writebacks) override |

| Send writebacks down the memory hierarchy in atomic mode. | |

| void | serviceMSHRTargets (MSHR *mshr, const PacketPtr pkt, CacheBlk *blk) override |

| Service non-deferred MSHR targets using the received response. | |

| void | recvTimingSnoopReq (PacketPtr pkt) override |

| Snoops bus transactions to maintain coherence. | |

| void | recvTimingSnoopResp (PacketPtr pkt) override |

| Handle a snoop response. | |

| Cycles | handleAtomicReqMiss (PacketPtr pkt, CacheBlk *&blk, PacketList &writebacks) override |

| Handle a request in atomic mode that missed in this cache. | |

| Tick | recvAtomic (PacketPtr pkt) override |

| Performs the access specified by the request. | |

| Tick | recvAtomicSnoop (PacketPtr pkt) override |

| Snoop for the provided request in the cache and return the estimated time taken. | |

| void | satisfyRequest (PacketPtr pkt, CacheBlk *blk, bool deferred_response=false, bool pending_downgrade=false) override |

| Perform any necessary updates to the block and perform any data exchange between the packet and the block. | |

| void | doTimingSupplyResponse (PacketPtr req_pkt, const uint8_t *blk_data, bool already_copied, bool pending_inval) |

| uint32_t | handleSnoop (PacketPtr pkt, CacheBlk *blk, bool is_timing, bool is_deferred, bool pending_inval) |

| Perform an upward snoop if needed, and update the block state (possibly invalidating the block). | |

| PacketPtr | evictBlock (CacheBlk *blk) override |

| Evict a cache block. | |

| PacketPtr | cleanEvictBlk (CacheBlk *blk) |

| Create a CleanEvict request for the given block. | |

| PacketPtr | createMissPacket (PacketPtr cpu_pkt, CacheBlk *blk, bool needs_writable, bool is_whole_line_write) const override |

| Create an appropriate downstream bus request packet. | |

| bool | isCachedAbove (PacketPtr pkt, bool is_timing=true) |

| Send up a snoop request and find cached copies. | |

| Protected Member Functions inherited from gem5::BaseCache | |

| void | markInService (MSHR *mshr, bool pending_modified_resp) |

| Mark a request as in service (sent downstream in the memory system), effectively making this MSHR the ordering point. | |

| void | markInService (WriteQueueEntry *entry) |

| bool | allocOnFill (MemCmd cmd) const |

| Determine whether we should allocate on a fill or not. | |

| Addr | regenerateBlkAddr (CacheBlk *blk) |

| Regenerate block address using tags. | |

| Cycles | calculateTagOnlyLatency (const uint32_t delay, const Cycles lookup_lat) const |

| Calculate latency of accesses that only touch the tag array. | |

| Cycles | calculateAccessLatency (const CacheBlk *blk, const uint32_t delay, const Cycles lookup_lat) const |

| Calculate access latency in ticks given a tag lookup latency, and whether access was a hit or miss. | |

| void | handleTimingReqMiss (PacketPtr pkt, MSHR *mshr, CacheBlk *blk, Tick forward_time, Tick request_time) |

| void | handleUncacheableWriteResp (PacketPtr pkt) |

| Handling the special case of uncacheable write responses to make recvTimingResp less cluttered. | |

| virtual void | recvTimingResp (PacketPtr pkt) |

| Handles a response (cache line fill/write ack) from the bus. | |

| virtual void | functionalAccess (PacketPtr pkt, bool from_cpu_side) |

| Performs the access specified by the request. | |

| void | updateBlockData (CacheBlk *blk, const PacketPtr cpkt, bool has_old_data) |

| Update the data contents of a block. | |

| void | cmpAndSwap (CacheBlk *blk, PacketPtr pkt) |

| Handle doing the Compare and Swap function for SPARC. | |

| QueueEntry * | getNextQueueEntry () |

| Return the next queue entry to service, either a pending miss from the MSHR queue, a buffered write from the write buffer, or something from the prefetcher. | |

| void | writebackTempBlockAtomic () |

| Send the outstanding tempBlock writeback. | |

| bool | updateCompressionData (CacheBlk *&blk, const uint64_t *data, PacketList &writebacks) |

| When a block is overwriten, its compression information must be updated, and it may need to be recompressed. | |

| void | maintainClusivity (bool from_cache, CacheBlk *blk) |

| Maintain the clusivity of this cache by potentially invalidating a block. | |

| bool | handleEvictions (std::vector< CacheBlk * > &evict_blks, PacketList &writebacks) |

| Try to evict the given blocks. | |

| CacheBlk * | handleFill (PacketPtr pkt, CacheBlk *blk, PacketList &writebacks, bool allocate) |

| Handle a fill operation caused by a received packet. | |

| CacheBlk * | allocateBlock (const PacketPtr pkt, PacketList &writebacks) |

| Allocate a new block and perform any necessary writebacks. | |

| void | evictBlock (CacheBlk *blk, PacketList &writebacks) |

| Evict a cache block. | |

| void | invalidateBlock (CacheBlk *blk) |

| Invalidate a cache block. | |

| PacketPtr | writebackBlk (CacheBlk *blk) |

| Create a writeback request for the given block. | |

| PacketPtr | writecleanBlk (CacheBlk *blk, Request::Flags dest, PacketId id) |

| Create a writeclean request for the given block. | |

| virtual void | memWriteback () override |

| Write back dirty blocks in the cache using functional accesses. | |

| virtual void | memInvalidate () override |

| Invalidates all blocks in the cache. | |

| bool | isDirty () const |

| Determine if there are any dirty blocks in the cache. | |

| bool | inRange (Addr addr) const |

| Determine if an address is in the ranges covered by this cache. | |

| Tick | nextQueueReadyTime () const |

| Find next request ready time from among possible sources. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| const bool | doFastWrites |

| This cache should allocate a block on a line-sized write miss. | |

| std::unordered_set< RequestPtr > | outstandingSnoop |

| Store the outstanding requests that we are expecting snoop responses from so we can determine which snoop responses we generated and which ones were merely forwarded. | |

| Protected Attributes inherited from gem5::BaseCache | |

| CpuSidePort | cpuSidePort |

| MemSidePort | memSidePort |

| gem5::BaseCache::CacheAccessorImpl | accessor |

| MSHRQueue | mshrQueue |

| Miss status registers. | |

| WriteQueue | writeBuffer |

| Write/writeback buffer. | |

| BaseTags * | tags |

| Tag and data Storage. | |

| compression::Base * | compressor |

| Compression method being used. | |

| partitioning_policy::PartitionManager * | partitionManager |

| Partitioning manager. | |

| prefetch::Base * | prefetcher |

| Prefetcher. | |

| ProbePointArg< CacheAccessProbeArg > * | ppHit |

| To probe when a cache hit occurs. | |

| ProbePointArg< CacheAccessProbeArg > * | ppMiss |

| To probe when a cache miss occurs. | |

| ProbePointArg< CacheAccessProbeArg > * | ppFill |

| To probe when a cache fill occurs. | |

| ProbePointArg< CacheDataUpdateProbeArg > * | ppDataUpdate |

| To probe when the contents of a block are updated. | |

| WriteAllocator *const | writeAllocator |

| The writeAllocator drive optimizations for streaming writes. | |

| TempCacheBlk * | tempBlock |

| Temporary cache block for occasional transitory use. | |

| std::unique_ptr< Packet > | pendingDelete |

| Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call. | |

| const bool | writebackClean |

| Determine if clean lines should be written back or not. | |

| PacketPtr | tempBlockWriteback |

| Writebacks from the tempBlock, resulting on the response path in atomic mode, must happen after the call to recvAtomic has finished (for the right ordering of the packets). | |

| EventFunctionWrapper | writebackTempBlockAtomicEvent |

| An event to writeback the tempBlock after recvAtomic finishes. | |

| const unsigned | blkSize |

| Block size of this cache. | |

| const Cycles | lookupLatency |

| The latency of tag lookup of a cache. | |

| const Cycles | dataLatency |

| The latency of data access of a cache. | |

| const Cycles | forwardLatency |

| This is the forward latency of the cache. | |

| const Cycles | fillLatency |

| The latency to fill a cache block. | |

| const Cycles | responseLatency |

| The latency of sending reponse to its upper level cache/core on a linefill. | |

| const bool | sequentialAccess |

| Whether tags and data are accessed sequentially. | |

| const int | numTarget |

| The number of targets for each MSHR. | |

| bool | forwardSnoops |

| Do we forward snoops from mem side port through to cpu side port? | |

| const enums::Clusivity | clusivity |

| Clusivity with respect to the upstream cache, determining if we fill into both this cache and the cache above on a miss. | |

| const bool | isReadOnly |

| Is this cache read only, for example the instruction cache, or table-walker cache. | |

| const bool | replaceExpansions |

| when a data expansion of a compressed block happens it will not be able to co-allocate where it is at anymore. | |

| const bool | moveContractions |

| Similar to data expansions, after a block improves its compression, it may need to be moved elsewhere compatible with the new compression factor, or, if not required by the compaction method, it may be moved to co-allocate with an existing block and thus free an entry. | |

| uint8_t | blocked |

| Bit vector of the blocking reasons for the access path. | |

| uint64_t | order |

| Increasing order number assigned to each incoming request. | |

| Cycles | blockedCycle |

| Stores time the cache blocked for statistics. | |

| MSHR * | noTargetMSHR |

| Pointer to the MSHR that has no targets. | |

| Counter | missCount |

| The number of misses to trigger an exit event. | |

| const AddrRangeList | addrRanges |

| The address range to which the cache responds on the CPU side. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Public Types inherited from gem5::BaseCache | |

| enum | BlockedCause { Blocked_NoMSHRs = MSHRQueue_MSHRs , Blocked_NoWBBuffers = MSHRQueue_WriteBuffer , Blocked_NoTargets , NUM_BLOCKED_CAUSES } |

| Reasons for caches to be blocked. More... | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::BaseCache | |

| System * | system |

| System we are currently operating in. | |

| gem5::BaseCache::CacheStats | stats |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| Protected Types inherited from gem5::BaseCache | |

| enum | MSHRQueueIndex { MSHRQueue_MSHRs , MSHRQueue_WriteBuffer } |

| Indexes to enumerate the MSHR queues. More... | |

Detailed Description

A coherent cache that can be arranged in flexible topologies.

Constructor & Destructor Documentation

◆ Cache()

| gem5::Cache::Cache | ( | const CacheParams & | p | ) |

Instantiates a basic cache object.

Definition at line 69 of file cache.cc.

References gem5::BaseCache::BaseCache(), gem5::X86ISA::CacheParams, doFastWrites, gem5::MipsISA::p, and gem5::BaseCache::system.

Referenced by access(), cleanEvictBlk(), createMissPacket(), doTimingSupplyResponse(), handleAtomicReqMiss(), handleSnoop(), promoteWholeLineWrites(), recvAtomic(), recvTimingReq(), recvTimingSnoopReq(), recvTimingSnoopResp(), sendMSHRQueuePacket(), and serviceMSHRTargets().

Member Function Documentation

◆ access()

|

overrideprotectedvirtual |

Does all the processing necessary to perform the provided request.

- Parameters

-

pkt The memory request to perform. blk The cache block to be updated. lat The latency of the access. writebacks List for any writebacks that need to be performed.

- Returns

- Boolean indicating whether the request was satisfied.

Reimplemented from gem5::BaseCache.

Definition at line 161 of file cache.cc.

References gem5::BaseCache::access(), Cache(), DPRINTF, gem5::BaseCache::evictBlock(), gem5_assert, gem5::BaseCache::isReadOnly, gem5::Packet::isRequest(), gem5::TaggedEntry::isValid(), gem5::Packet::isWrite(), gem5::BaseCache::lookupLatency, gem5::Named::name(), gem5::Packet::print(), gem5::Packet::req, and gem5::BaseCache::tags.

◆ cleanEvictBlk()

Create a CleanEvict request for the given block.

- Parameters

-

blk The block to evict.

- Returns

- The CleanEvict request for the block.

Definition at line 972 of file cache.cc.

References gem5::Packet::allocate(), gem5::BaseCache::blkSize, Cache(), gem5::MemCmd::CleanEvict, gem5::CacheBlk::DirtyBit, DPRINTF, gem5::CacheBlk::getTaskId(), gem5::TaggedEntry::isSecure(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::Packet::print(), gem5::BaseCache::regenerateBlkAddr(), gem5::Request::SECURE, gem5::Request::wbRequestorId, and gem5::BaseCache::writebackClean.

Referenced by evictBlock().

◆ createMissPacket()

|

overrideprotectedvirtual |

Create an appropriate downstream bus request packet.

Creates a new packet with the request to be send to the memory below, or nullptr if the current request in cpu_pkt should just be forwarded on.

- Parameters

-

cpu_pkt The miss packet that needs to be satisfied. blk The referenced block, can be nullptr. needs_writable Indicates that the block must be writable even if the request in cpu_pkt doesn't indicate that. is_whole_line_write True if there are writes for the whole line

- Returns

- A packet send to the memory below

Implements gem5::BaseCache.

Definition at line 492 of file cache.cc.

References gem5::Packet::allocate(), gem5::BaseCache::blkSize, Cache(), gem5::BaseCache::clusivity, gem5::Packet::cmd, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getBlockAddr(), gem5::Packet::hasSharers(), gem5::MemCmd::InvalidateReq, gem5::Packet::isClean(), gem5::Packet::isEviction(), gem5::Packet::isLLSC(), gem5::BaseCache::isReadOnly, gem5::CacheBlk::isSet(), gem5::Packet::isUpgrade(), gem5::TaggedEntry::isValid(), gem5::Packet::needsResponse(), gem5::Packet::print(), gem5::MemCmd::ReadCleanReq, gem5::MemCmd::ReadExReq, gem5::MemCmd::ReadSharedReq, gem5::Packet::req, gem5::MemCmd::SCUpgradeFailReq, gem5::MemCmd::SCUpgradeReq, gem5::Packet::setHasSharers(), gem5::MemCmd::StoreCondFailReq, gem5::MemCmd::UpgradeReq, gem5::CacheBlk::WritableBit, and gem5::MemCmd::WriteLineReq.

Referenced by handleAtomicReqMiss().

◆ doTimingSupplyResponse()

|

protected |

Definition at line 1000 of file cache.cc.

References gem5::BaseCache::blkSize, Cache(), gem5::Clocked::clockEdge(), gem5::Packet::cmd, DPRINTF, gem5::BaseCache::forwardLatency, gem5::Packet::hasSharers(), gem5::Packet::headerDelay, gem5::Packet::isInvalidate(), gem5::Packet::isRead(), gem5::Packet::isRequest(), gem5::Packet::makeTimingResponse(), gem5::BaseCache::memSidePort, gem5::Packet::needsResponse(), gem5::Packet::payloadDelay, gem5::Packet::print(), gem5::MemCmd::ReadResp, gem5::MemCmd::ReadRespWithInvalidate, gem5::Packet::req, and gem5::Packet::setDataFromBlock().

Referenced by handleSnoop(), and recvTimingSnoopReq().

◆ doWritebacks()

|

overrideprotectedvirtual |

Insert writebacks into the write buffer.

Implements gem5::BaseCache.

Definition at line 190 of file cache.cc.

References gem5::BaseCache::allocateWriteBuffer(), gem5::MemCmd::CleanEvict, gem5::Packet::cmd, isCachedAbove(), gem5::Packet::setBlockCached(), gem5::MemCmd::WritebackClean, gem5::BaseCache::writebackClean, gem5::MemCmd::WritebackDirty, and gem5::MemCmd::WriteClean.

Referenced by handleSnoop().

◆ doWritebacksAtomic()

|

overrideprotectedvirtual |

Send writebacks down the memory hierarchy in atomic mode.

Implements gem5::BaseCache.

Definition at line 232 of file cache.cc.

References gem5::Packet::cmd, isCachedAbove(), gem5::BaseCache::memSidePort, gem5::MemCmd::WritebackDirty, and gem5::MemCmd::WriteClean.

Referenced by handleSnoop().

◆ evictBlock()

Evict a cache block.

Performs a writeback if necesssary and invalidates the block

- Parameters

-

blk Block to invalidate

- Returns

- A packet with the writeback, can be nullptr

Implements gem5::BaseCache.

Definition at line 961 of file cache.cc.

References cleanEvictBlk(), gem5::CacheBlk::DirtyBit, gem5::BaseCache::invalidateBlock(), gem5::CacheBlk::isSet(), gem5::BaseCache::writebackBlk(), and gem5::BaseCache::writebackClean.

◆ handleAtomicReqMiss()

|

overrideprotectedvirtual |

Handle a request in atomic mode that missed in this cache.

Creates a downstream request, sends it to the memory below and handles the response. As we are in atomic mode all operations are performed immediately.

- Parameters

-

pkt The packet with the requests blk The referenced block writebacks A list with packets for any performed writebacks

- Returns

- Cycles for handling the request

Implements gem5::BaseCache.

Definition at line 578 of file cache.cc.

References gem5::BaseCache::allocOnFill(), gem5::BaseCache::blkSize, Cache(), gem5::Packet::cmd, gem5::Packet::copyError(), createMissPacket(), DPRINTF, gem5::Packet::fromCache(), gem5::BaseCache::handleFill(), gem5::BaseCache::invalidateBlock(), gem5::Packet::isError(), gem5::Packet::isEviction(), gem5::Packet::isInvalidate(), gem5::Packet::isRead(), gem5::Packet::isResponse(), gem5::TaggedEntry::isValid(), gem5::Packet::isWholeLineWrite(), gem5::Packet::isWrite(), gem5::BaseCache::maintainClusivity(), gem5::Packet::makeAtomicResponse(), gem5::BaseCache::memSidePort, gem5::Packet::needsResponse(), gem5::Packet::needsWritable(), gem5::CacheBlk::print(), gem5::Packet::print(), gem5::Packet::req, satisfyRequest(), gem5::Clocked::ticksToCycles(), gem5::MemCmd::UpgradeResp, gem5::BaseCache::writeAllocator, and gem5::MemCmd::WriteClean.

◆ handleSnoop()

|

protected |

Perform an upward snoop if needed, and update the block state (possibly invalidating the block).

Also create a response if required.

- Parameters

-

pkt Snoop packet blk Cache block being snooped is_timing Timing or atomic for the response is_deferred Is this a deferred snoop or not? pending_inval Do we have a pending invalidation?

- Returns

- The snoop delay incurred by the upwards snoop

Definition at line 1045 of file cache.cc.

References gem5::BaseCache::blkSize, Cache(), gem5::Packet::cacheResponding(), gem5::CacheBlk::clearCoherenceBits(), gem5::Clocked::clockEdge(), gem5::BaseCache::compressor, gem5::Packet::copyResponderFlags(), gem5::BaseCache::cpuSidePort, gem5::CacheBlk::data, gem5::CacheBlk::DirtyBit, doTimingSupplyResponse(), doWritebacks(), doWritebacksAtomic(), DPRINTF, gem5::BaseCache::forwardLatency, gem5::BaseCache::forwardSnoops, gem5_assert, gem5::Packet::getAddr(), gem5::Packet::hasData(), gem5::Packet::hasSharers(), gem5::Packet::headerDelay, gem5::Packet::id, gem5::BaseCache::invalidateBlock(), gem5::Packet::isBlockCached(), gem5::Packet::isClean(), gem5::Packet::isInvalidate(), gem5::Packet::isRead(), gem5::BaseCache::isReadOnly, gem5::Packet::isRequest(), gem5::Packet::isResponse(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::Packet::makeAtomicResponse(), gem5::Packet::mustCheckAbove(), gem5::Named::name(), gem5::Packet::needsResponse(), gem5::Packet::needsWritable(), panic_if, gem5::Packet::payloadDelay, gem5::CacheBlk::print(), gem5::Packet::print(), gem5::Packet::req, gem5::Packet::satisfied(), gem5::Packet::setBlockCached(), gem5::Packet::setCacheResponding(), gem5::Packet::setDataFromBlock(), gem5::Packet::setExpressSnoop(), gem5::Packet::setHasSharers(), gem5::Packet::setResponderHadWritable(), gem5::Packet::setSatisfied(), gem5::CacheBlk::WritableBit, and gem5::BaseCache::writecleanBlk().

Referenced by recvAtomicSnoop(), recvTimingSnoopReq(), and serviceMSHRTargets().

◆ handleTimingReqHit()

|

overrideprotectedvirtual |

Reimplemented from gem5::BaseCache.

Definition at line 313 of file cache.cc.

References gem5::BaseCache::handleTimingReqHit(), and gem5::Packet::req.

◆ handleTimingReqMiss()

|

overrideprotectedvirtual |

Implements gem5::BaseCache.

Definition at line 324 of file cache.cc.

References gem5::BaseCache::allocateMissBuffer(), gem5::BaseCache::allocateWriteBuffer(), gem5::BaseCache::blkSize, gem5::Packet::cmd, gem5::BaseCache::cpuSidePort, gem5::Packet::getBlockAddr(), gem5::Packet::getSize(), gem5::BaseCache::handleTimingReqMiss(), gem5::Packet::isCleanInvalidateRequest(), gem5::Packet::isRead(), gem5::Packet::isSecure(), gem5::MemCmd::isSWPrefetch(), gem5::TaggedEntry::isValid(), gem5::Packet::isWrite(), gem5::MemCmd::LockedRMWWriteReq, gem5::Packet::makeTimingResponse(), gem5::BaseCache::mshrQueue, gem5::Packet::needsResponse(), gem5::X86ISA::pf, gem5::Packet::req, and gem5::BaseCache::stats.

◆ isCachedAbove()

|

protected |

Send up a snoop request and find cached copies.

If cached copies are found, set the BLOCK_CACHED flag in pkt.

Definition at line 1392 of file cache.cc.

References gem5::Packet::cacheResponding(), gem5::Packet::cmd, gem5::BaseCache::cpuSidePort, gem5::BaseCache::forwardSnoops, gem5::Packet::isBlockCached(), gem5::Packet::isEviction(), gem5::Packet::senderState, gem5::Packet::setExpressSnoop(), and gem5::MemCmd::WriteClean.

Referenced by doWritebacks(), and doWritebacksAtomic().

◆ promoteWholeLineWrites()

|

protected |

Turn line-sized writes into WriteInvalidate transactions.

Definition at line 301 of file cache.cc.

References gem5::BaseCache::blkSize, Cache(), gem5::Packet::cmd, doFastWrites, DPRINTF, gem5::Packet::getOffset(), gem5::Packet::getSize(), gem5::Packet::isMaskedWrite(), gem5::MemCmd::WriteLineReq, and gem5::MemCmd::WriteReq.

Referenced by recvAtomic(), and recvTimingReq().

◆ recvAtomic()

Performs the access specified by the request.

- Parameters

-

pkt The request to perform.

- Returns

- The number of ticks required for the access.

Reimplemented from gem5::BaseCache.

Definition at line 668 of file cache.cc.

References Cache(), gem5::Packet::cacheResponding(), DPRINTF, gem5::BaseCache::memSidePort, gem5::Packet::needsWritable(), gem5::Packet::print(), promoteWholeLineWrites(), gem5::BaseCache::recvAtomic(), gem5::Packet::req, and gem5::Packet::responderHadWritable().

◆ recvAtomicSnoop()

Snoop for the provided request in the cache and return the estimated time taken.

- Parameters

-

pkt The memory request to snoop

- Returns

- The number of ticks required for the snoop.

Implements gem5::BaseCache.

Definition at line 1379 of file cache.cc.

References gem5::Clocked::clockPeriod(), gem5::Packet::getAddr(), handleSnoop(), gem5::BaseCache::inRange(), gem5::Packet::isSecure(), gem5::BaseCache::lookupLatency, and gem5::BaseCache::tags.

◆ recvTimingReq()

|

overrideprotectedvirtual |

Performs the access specified by the request.

- Parameters

-

pkt The request to perform.

Reimplemented from gem5::BaseCache.

Definition at line 418 of file cache.cc.

References Cache(), gem5::Packet::cacheResponding(), DPRINTF, gem5::Packet::headerDelay, gem5::BaseCache::memSidePort, gem5::Packet::needsWritable(), gem5::Packet::payloadDelay, gem5::BaseCache::pendingDelete, gem5::Packet::print(), promoteWholeLineWrites(), gem5::BaseCache::recvTimingReq(), gem5::Packet::responderHadWritable(), gem5::Packet::setCacheResponding(), gem5::Packet::setExpressSnoop(), and gem5::BaseCache::tags.

◆ recvTimingSnoopReq()

|

overrideprotectedvirtual |

Snoops bus transactions to maintain coherence.

- Parameters

-

pkt The current bus transaction.

Implements gem5::BaseCache.

Definition at line 1261 of file cache.cc.

References gem5::BaseCache::blkSize, Cache(), gem5::Clocked::clockPeriod(), gem5::Packet::cmd, doTimingSupplyResponse(), DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getBlockAddr(), gem5::Packet::getConstPtr(), gem5::MSHR::getNumTargets(), gem5::WriteQueueEntry::getNumTargets(), gem5::WriteQueueEntry::getTarget(), handleSnoop(), gem5::MSHR::handleSnoop(), gem5::Packet::hasSharers(), gem5::BaseCache::inRange(), gem5::Packet::isEviction(), gem5::Packet::isInvalidate(), gem5::Packet::isRead(), gem5::Packet::isSecure(), gem5::QueueEntry::isUncacheable(), gem5::BaseCache::lookupLatency, gem5::BaseCache::markInService(), gem5::BaseCache::mshrQueue, gem5::Packet::mustCheckAbove(), gem5::Packet::needsResponse(), gem5::Packet::needsWritable(), gem5::BaseCache::numTarget, gem5::BaseCache::order, gem5::QueueEntry::Target::pkt, gem5::MSHR::print(), gem5::Packet::print(), gem5::Packet::req, gem5::Packet::setBlockCached(), gem5::Packet::setCacheResponding(), gem5::Packet::setHasSharers(), gem5::Packet::setResponderHadWritable(), gem5::Packet::snoopDelay, gem5::BaseCache::tags, warn, gem5::MemCmd::WritebackDirty, gem5::BaseCache::writeBuffer, and gem5::MemCmd::WriteClean.

◆ recvTimingSnoopResp()

|

overrideprotectedvirtual |

Handle a snoop response.

- Parameters

-

pkt Snoop response packet

Implements gem5::BaseCache.

Definition at line 267 of file cache.cc.

References Cache(), gem5::Clocked::clockEdge(), gem5::Packet::cmd, DPRINTF, gem5::BaseCache::forwardLatency, gem5::Packet::getAddr(), gem5::MemCmd::HardPFResp, gem5::Packet::headerDelay, gem5::Packet::isSecure(), gem5::BaseCache::memSidePort, outstandingSnoop, gem5::Packet::payloadDelay, gem5::Packet::print(), gem5::BaseCache::recvTimingResp(), and gem5::Packet::req.

◆ satisfyRequest()

|

overrideprotectedvirtual |

Perform any necessary updates to the block and perform any data exchange between the packet and the block.

The flags of the packet are also set accordingly.

- Parameters

-

pkt Request packet from upstream that hit a block blk Cache block that the packet hit deferred_response Whether this request originally missed pending_downgrade Whether the writable flag is to be removed

Reimplemented from gem5::BaseCache.

Definition at line 78 of file cache.cc.

References gem5::BaseCache::blkSize, gem5::CacheBlk::clearCoherenceBits(), gem5::Packet::cmd, gem5::CacheBlk::DirtyBit, gem5::Packet::fromCache(), gem5::Packet::getSize(), gem5::Packet::hasSharers(), gem5::Packet::isRead(), gem5::CacheBlk::isSet(), gem5::Packet::needsWritable(), gem5::MemCmd::ReadCleanReq, gem5::MemCmd::ReadExReq, gem5::BaseCache::satisfyRequest(), gem5::MemCmd::SCUpgradeFailReq, gem5::Packet::setCacheResponding(), gem5::Packet::setHasSharers(), and gem5::CacheBlk::WritableBit.

Referenced by handleAtomicReqMiss(), and serviceMSHRTargets().

◆ sendMSHRQueuePacket()

|

overridevirtual |

Take an MSHR, turn it into a suitable downstream packet, and send it out.

This construct allows a queue entry to choose a suitable approach based on its type.

- Parameters

-

mshr The MSHR to turn into a packet and send

- Returns

- True if the port is waiting for a retry

Reimplemented from gem5::BaseCache.

Definition at line 1420 of file cache.cc.

References gem5::QueueEntry::blkAddr, gem5::BaseCache::Blocked_NoMSHRs, Cache(), gem5::Packet::cacheResponding(), gem5::BaseCache::clearBlocked(), gem5::Packet::cmd, gem5::BaseCache::cpuSidePort, DPRINTF, gem5::BaseCache::forwardSnoops, gem5::Packet::getAddr(), gem5::MSHR::getTarget(), gem5::MemCmd::HardPFReq, gem5::Packet::hasSharers(), gem5::Packet::isBlockCached(), gem5::Packet::isSecure(), gem5::BaseCache::markInService(), gem5::BaseCache::mshrQueue, outstandingSnoop, gem5::QueueEntry::Target::pkt, gem5::Packet::print(), gem5::MipsISA::r, gem5::Packet::req, gem5::Packet::senderState, gem5::BaseCache::sendMSHRQueuePacket(), gem5::Packet::setExpressSnoop(), and gem5::BaseCache::tags.

◆ serviceMSHRTargets()

|

overrideprotectedvirtual |

Service non-deferred MSHR targets using the received response.

Iterates through the list of targets that can be serviced with the current response.

- Parameters

-

mshr The MSHR that corresponds to the reponse pkt The response packet blk The reference block

Implements gem5::BaseCache.

Definition at line 699 of file cache.cc.

References gem5::BaseCache::blkSize, Cache(), gem5::CacheBlk::clearCoherenceBits(), gem5::Clocked::clockEdge(), gem5::Packet::cmd, gem5::Packet::copyError(), gem5::Packet::copyResponderFlags(), gem5::BaseCache::cpuSidePort, gem5::CacheBlk::DirtyBit, DPRINTF, gem5::MSHR::extractServiceableTargets(), gem5::MSHR::Target::FromCPU, gem5::MSHR::Target::FromPrefetcher, gem5::MSHR::Target::FromSnoop, gem5::Packet::getConstPtr(), gem5::Packet::getOffset(), gem5::Packet::getSize(), gem5::MSHR::getTarget(), handleSnoop(), gem5::MemCmd::HardPFReq, gem5::Packet::hasData(), gem5::MSHR::TargetList::hasFromCache, gem5::MSHR::hasLockedRMWReadTarget(), gem5::MSHR::hasPostDowngrade(), gem5::MSHR::hasPostInvalidate(), gem5::Packet::hasRespData(), gem5::Packet::headerDelay, gem5::BaseCache::invalidateBlock(), gem5::MemCmd::InvalidateResp, gem5::Packet::isError(), gem5::MSHR::isForward, gem5::Packet::isInvalidate(), gem5::Packet::isRead(), gem5::BaseCache::isReadOnly, gem5::CacheBlk::isSet(), gem5::MemCmd::isSWPrefetch(), gem5::TaggedEntry::isValid(), gem5::MemCmd::LockedRMWReadReq, gem5::MemCmd::LockedRMWWriteResp, gem5::BaseCache::maintainClusivity(), gem5::Packet::makeTimingResponse(), gem5::Packet::matchAddr(), gem5::Named::name(), gem5::Packet::needsWritable(), panic, panic_if, gem5::Packet::payloadDelay, gem5::QueueEntry::Target::pkt, gem5::MSHR::popTarget(), gem5::Packet::print(), gem5::CacheBlk::ReadableBit, gem5::MemCmd::ReadResp, gem5::MemCmd::ReadRespWithInvalidate, gem5::Packet::req, gem5::BaseCache::responseLatency, satisfyRequest(), gem5::MemCmd::SCUpgradeFailReq, gem5::CacheBlk::setCoherenceBits(), gem5::Packet::setData(), gem5::CacheBlk::setPrefetched(), gem5::BaseCache::stats, gem5::MemCmd::StoreCondFailReq, gem5::MemCmd::StoreCondReq, gem5::BaseCache::system, gem5::MSHR::updateLockedRMWReadTarget(), gem5::MemCmd::UpgradeFailResp, gem5::MSHR::wasWholeLineWrite, gem5::CacheBlk::WritableBit, and gem5::MemCmd::WriteLineReq.

Member Data Documentation

◆ doFastWrites

|

protected |

This cache should allocate a block on a line-sized write miss.

Definition at line 73 of file cache.hh.

Referenced by Cache(), and promoteWholeLineWrites().

◆ outstandingSnoop

|

protected |

Store the outstanding requests that we are expecting snoop responses from so we can determine which snoop responses we generated and which ones were merely forwarded.

Definition at line 80 of file cache.hh.

Referenced by recvTimingSnoopResp(), and sendMSHRQueuePacket().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:49 for gem5 by doxygen 1.14.0