#include <instructions.hh>

Public Member Functions | |

| Inst_DS__DS_BPERMUTE_B32 (InFmt_DS *) | |

| ~Inst_DS__DS_BPERMUTE_B32 () | |

| int | getNumOperands () override |

| int | numDstRegOperands () override |

| int | numSrcRegOperands () override |

| int | getOperandSize (int opIdx) override |

| void | execute (GPUDynInstPtr) override |

| Public Member Functions inherited from gem5::VegaISA::Inst_DS | |

| Inst_DS (InFmt_DS *, const std::string &opcode) | |

| ~Inst_DS () | |

| int | instSize () const override |

| void | generateDisassembly () override |

| void | initOperandInfo () override |

| Public Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| VEGAGPUStaticInst (const std::string &opcode) | |

| ~VEGAGPUStaticInst () | |

| void | generateDisassembly () override |

| bool | isFlatScratchRegister (int opIdx) override |

| bool | isExecMaskRegister (int opIdx) override |

| void | initOperandInfo () override |

| int | getOperandSize (int opIdx) override |

| int | coalescerTokenCount () const override |

| Return the number of tokens needed by the coalescer. | |

| ScalarRegU32 | srcLiteral () const override |

| Public Member Functions inherited from gem5::GPUStaticInst | |

| GPUStaticInst (const std::string &opcode) | |

| virtual | ~GPUStaticInst () |

| void | instAddr (int inst_addr) |

| int | instAddr () const |

| int | nextInstAddr () const |

| void | instNum (int num) |

| int | instNum () |

| void | ipdInstNum (int num) |

| int | ipdInstNum () const |

| void | initDynOperandInfo (Wavefront *wf, ComputeUnit *cu) |

| const std::string & | disassemble () |

| int | numSrcVecOperands () |

| int | numDstVecOperands () |

| int | numSrcVecDWords () |

| int | numDstVecDWords () |

| int | numSrcScalarOperands () |

| int | numDstScalarOperands () |

| int | numSrcScalarDWords () |

| int | numDstScalarDWords () |

| int | maxOperandSize () |

| bool | isALU () const |

| bool | isBranch () const |

| bool | isCondBranch () const |

| bool | isNop () const |

| bool | isReturn () const |

| bool | isEndOfKernel () const |

| bool | isKernelLaunch () const |

| bool | isSDWAInst () const |

| bool | isDPPInst () const |

| bool | isUnconditionalJump () const |

| bool | isSpecialOp () const |

| bool | isWaitcnt () const |

| bool | isSleep () const |

| bool | isBarrier () const |

| bool | isMemSync () const |

| bool | isMemRef () const |

| bool | isFlat () const |

| bool | isFlatGlobal () const |

| bool | isFlatScratch () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isAtomicNoRet () const |

| bool | isAtomicRet () const |

| bool | isScalar () const |

| bool | readsSCC () const |

| bool | writesSCC () const |

| bool | readsVCC () const |

| bool | writesVCC () const |

| bool | readsEXEC () const |

| bool | writesEXEC () const |

| bool | readsMode () const |

| bool | writesMode () const |

| bool | ignoreExec () const |

| bool | isAtomicAnd () const |

| bool | isAtomicOr () const |

| bool | isAtomicXor () const |

| bool | isAtomicCAS () const |

| bool | isAtomicExch () const |

| bool | isAtomicAdd () const |

| bool | isAtomicSub () const |

| bool | isAtomicInc () const |

| bool | isAtomicDec () const |

| bool | isAtomicMax () const |

| bool | isAtomicMin () const |

| bool | isArgLoad () const |

| bool | isGlobalMem () const |

| bool | isLocalMem () const |

| bool | isArgSeg () const |

| bool | isGlobalSeg () const |

| bool | isGroupSeg () const |

| bool | isKernArgSeg () const |

| bool | isPrivateSeg () const |

| bool | isReadOnlySeg () const |

| bool | isSpillSeg () const |

| bool | isGloballyCoherent () const |

| Coherence domain of a memory instruction. | |

| bool | isSystemCoherent () const |

| bool | isI8 () const |

| bool | isF16 () const |

| bool | isF32 () const |

| bool | isF64 () const |

| bool | isFMA () const |

| bool | isMAC () const |

| bool | isMAD () const |

| bool | isMFMA () const |

| bool | hasNoAddr () const |

| virtual void | initiateAcc (GPUDynInstPtr gpuDynInst) |

| virtual void | completeAcc (GPUDynInstPtr gpuDynInst) |

| virtual uint32_t | getTargetPc () |

| void | setFlag (Flags flag) |

| const std::string & | opcode () const |

| const std::vector< OperandInfo > & | srcOperands () const |

| const std::vector< OperandInfo > & | dstOperands () const |

| const std::vector< OperandInfo > & | srcVecRegOperands () const |

| const std::vector< OperandInfo > & | dstVecRegOperands () const |

| const std::vector< OperandInfo > & | srcScalarRegOperands () const |

| const std::vector< OperandInfo > & | dstScalarRegOperands () const |

Additional Inherited Members | |

| Public Types inherited from gem5::GPUStaticInst | |

| enum | OpType { SRC_VEC , SRC_SCALAR , DST_VEC , DST_SCALAR } |

| typedef int(RegisterManager::* | MapRegFn) (Wavefront *, int) |

| Public Attributes inherited from gem5::GPUStaticInst | |

| enums::StorageClassType | executed_as |

| Static Public Attributes inherited from gem5::GPUStaticInst | |

| static uint64_t | dynamic_id_count |

| Protected Member Functions inherited from gem5::VegaISA::Inst_DS | |

| template<typename T> | |

| void | initMemRead (GPUDynInstPtr gpuDynInst, Addr offset) |

| template<int N> | |

| void | initMemRead (GPUDynInstPtr gpuDynInst, Addr offset) |

| template<typename T> | |

| void | initDualMemRead (GPUDynInstPtr gpuDynInst, Addr offset0, Addr offset1) |

| template<typename T> | |

| void | initMemWrite (GPUDynInstPtr gpuDynInst, Addr offset) |

| template<int N> | |

| void | initMemWrite (GPUDynInstPtr gpuDynInst, Addr offset) |

| template<typename T> | |

| void | initDualMemWrite (GPUDynInstPtr gpuDynInst, Addr offset0, Addr offset1) |

| template<typename T> | |

| void | initAtomicAccess (GPUDynInstPtr gpuDynInst, Addr offset) |

| void | calcAddr (GPUDynInstPtr gpuDynInst, ConstVecOperandU32 &addr) |

| Protected Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| void | panicUnimplemented () const |

| Protected Attributes inherited from gem5::VegaISA::Inst_DS | |

| InFmt_DS | instData |

| InFmt_DS_1 | extData |

| Protected Attributes inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| ScalarRegU32 | _srcLiteral |

| if the instruction has a src literal - an immediate value that is part of the instruction stream - we store that here | |

| Protected Attributes inherited from gem5::GPUStaticInst | |

| const std::string | _opcode |

| std::string | disassembly |

| int | _instNum |

| int | _instAddr |

| std::vector< OperandInfo > | srcOps |

| std::vector< OperandInfo > | dstOps |

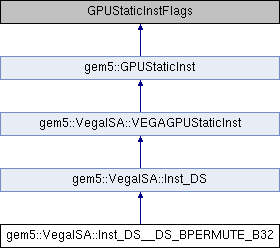

Detailed Description

Definition at line 33371 of file instructions.hh.

Constructor & Destructor Documentation

◆ Inst_DS__DS_BPERMUTE_B32()

| gem5::VegaISA::Inst_DS__DS_BPERMUTE_B32::Inst_DS__DS_BPERMUTE_B32 | ( | InFmt_DS * | iFmt | ) |

While this operation doesn't actually use DS storage we classify it as a load here because it does a writeback to a VGPR, which fits in better with the LDS pipeline logic.

Definition at line 2352 of file ds.cc.

References gem5::VegaISA::Inst_DS::Inst_DS(), and gem5::GPUStaticInst::setFlag().

◆ ~Inst_DS__DS_BPERMUTE_B32()

| gem5::VegaISA::Inst_DS__DS_BPERMUTE_B32::~Inst_DS__DS_BPERMUTE_B32 | ( | ) |

Member Function Documentation

◆ execute()

|

overridevirtual |

One of the offset fields can be used for the index. It is assumed OFFSET0 would be used, as OFFSET1 is typically only used for DS ops that operate on two disparate pieces of data.

The address provided is a byte address, but VGPRs are 4 bytes, so we must divide by 4 to get the actual VGPR index. Additionally, the index is calculated modulo the WF size, 64 in this case, so we simply extract bits 7-2.

If the shuffled index corresponds to a lane that is inactive then this instruction writes a 0 to the active lane in VDST.

This is needed because we treat this instruction as a load but it's not an actual memory request. Without this, the destination register never gets marked as free, leading to a possible deadlock

Similarly, this counter could build up over time, even across multiple wavefronts, and cause a deadlock.

Implements gem5::GPUStaticInst.

Definition at line 2371 of file ds.cc.

References gem5::X86ISA::addr, gem5::bits(), gem5::Wavefront::computeUnit, data, gem5::Wavefront::decLGKMInstsIssued(), gem5::Wavefront::execMask(), gem5::Wavefront::execUnitId, gem5::VegaISA::Inst_DS::extData, gem5::MipsISA::index, gem5::VegaISA::Inst_DS::instData, gem5::VegaISA::NumVecElemPerVecReg(), panic_if, gem5::Wavefront::rdLmReqsInPipe, gem5::Wavefront::simdId, gem5::Wavefront::untrackLGKMInst(), gem5::ComputeUnit::vrf, and gem5::VegaISA::VecOperand< DataType, Const, NumDwords >::write().

◆ getNumOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 33378 of file instructions.hh.

References numDstRegOperands(), and numSrcRegOperands().

◆ getOperandSize()

|

inlineoverridevirtual |

◆ numDstRegOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 33383 of file instructions.hh.

Referenced by getNumOperands().

◆ numSrcRegOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 33384 of file instructions.hh.

Referenced by getNumOperands().

The documentation for this class was generated from the following files:

- arch/amdgpu/vega/insts/instructions.hh

- arch/amdgpu/vega/insts/ds.cc

Generated on Sat Oct 18 2025 08:07:05 for gem5 by doxygen 1.14.0