#include <instructions.hh>

Public Member Functions | |

| Inst_SOPP__S_ENDPGM (InFmt_SOPP *) | |

| ~Inst_SOPP__S_ENDPGM () | |

| int | getNumOperands () override |

| int | numDstRegOperands () override |

| int | numSrcRegOperands () override |

| int | getOperandSize (int opIdx) override |

| void | execute (GPUDynInstPtr) override |

| Public Member Functions inherited from gem5::VegaISA::Inst_SOPP | |

| Inst_SOPP (InFmt_SOPP *, const std::string &opcode) | |

| ~Inst_SOPP () | |

| int | instSize () const override |

| void | generateDisassembly () override |

| void | initOperandInfo () override |

| Public Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| VEGAGPUStaticInst (const std::string &opcode) | |

| ~VEGAGPUStaticInst () | |

| void | generateDisassembly () override |

| bool | isFlatScratchRegister (int opIdx) override |

| bool | isExecMaskRegister (int opIdx) override |

| void | initOperandInfo () override |

| int | getOperandSize (int opIdx) override |

| int | coalescerTokenCount () const override |

| Return the number of tokens needed by the coalescer. | |

| ScalarRegU32 | srcLiteral () const override |

| Public Member Functions inherited from gem5::GPUStaticInst | |

| GPUStaticInst (const std::string &opcode) | |

| virtual | ~GPUStaticInst () |

| void | instAddr (int inst_addr) |

| int | instAddr () const |

| int | nextInstAddr () const |

| void | instNum (int num) |

| int | instNum () |

| void | ipdInstNum (int num) |

| int | ipdInstNum () const |

| void | initDynOperandInfo (Wavefront *wf, ComputeUnit *cu) |

| const std::string & | disassemble () |

| int | numSrcVecOperands () |

| int | numDstVecOperands () |

| int | numSrcVecDWords () |

| int | numDstVecDWords () |

| int | numSrcScalarOperands () |

| int | numDstScalarOperands () |

| int | numSrcScalarDWords () |

| int | numDstScalarDWords () |

| int | maxOperandSize () |

| bool | isALU () const |

| bool | isBranch () const |

| bool | isCondBranch () const |

| bool | isNop () const |

| bool | isReturn () const |

| bool | isEndOfKernel () const |

| bool | isKernelLaunch () const |

| bool | isSDWAInst () const |

| bool | isDPPInst () const |

| bool | isUnconditionalJump () const |

| bool | isSpecialOp () const |

| bool | isWaitcnt () const |

| bool | isSleep () const |

| bool | isBarrier () const |

| bool | isMemSync () const |

| bool | isMemRef () const |

| bool | isFlat () const |

| bool | isFlatGlobal () const |

| bool | isFlatScratch () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isAtomicNoRet () const |

| bool | isAtomicRet () const |

| bool | isScalar () const |

| bool | readsSCC () const |

| bool | writesSCC () const |

| bool | readsVCC () const |

| bool | writesVCC () const |

| bool | readsEXEC () const |

| bool | writesEXEC () const |

| bool | readsMode () const |

| bool | writesMode () const |

| bool | ignoreExec () const |

| bool | isAtomicAnd () const |

| bool | isAtomicOr () const |

| bool | isAtomicXor () const |

| bool | isAtomicCAS () const |

| bool | isAtomicExch () const |

| bool | isAtomicAdd () const |

| bool | isAtomicSub () const |

| bool | isAtomicInc () const |

| bool | isAtomicDec () const |

| bool | isAtomicMax () const |

| bool | isAtomicMin () const |

| bool | isArgLoad () const |

| bool | isGlobalMem () const |

| bool | isLocalMem () const |

| bool | isArgSeg () const |

| bool | isGlobalSeg () const |

| bool | isGroupSeg () const |

| bool | isKernArgSeg () const |

| bool | isPrivateSeg () const |

| bool | isReadOnlySeg () const |

| bool | isSpillSeg () const |

| bool | isGloballyCoherent () const |

| Coherence domain of a memory instruction. | |

| bool | isSystemCoherent () const |

| bool | isI8 () const |

| bool | isF16 () const |

| bool | isF32 () const |

| bool | isF64 () const |

| bool | isFMA () const |

| bool | isMAC () const |

| bool | isMAD () const |

| bool | isMFMA () const |

| bool | hasNoAddr () const |

| virtual void | initiateAcc (GPUDynInstPtr gpuDynInst) |

| virtual void | completeAcc (GPUDynInstPtr gpuDynInst) |

| virtual uint32_t | getTargetPc () |

| void | setFlag (Flags flag) |

| const std::string & | opcode () const |

| const std::vector< OperandInfo > & | srcOperands () const |

| const std::vector< OperandInfo > & | dstOperands () const |

| const std::vector< OperandInfo > & | srcVecRegOperands () const |

| const std::vector< OperandInfo > & | dstVecRegOperands () const |

| const std::vector< OperandInfo > & | srcScalarRegOperands () const |

| const std::vector< OperandInfo > & | dstScalarRegOperands () const |

Additional Inherited Members | |

| Public Types inherited from gem5::GPUStaticInst | |

| enum | OpType { SRC_VEC , SRC_SCALAR , DST_VEC , DST_SCALAR } |

| typedef int(RegisterManager::* | MapRegFn) (Wavefront *, int) |

| Public Attributes inherited from gem5::GPUStaticInst | |

| enums::StorageClassType | executed_as |

| Static Public Attributes inherited from gem5::GPUStaticInst | |

| static uint64_t | dynamic_id_count |

| Protected Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| void | panicUnimplemented () const |

| Protected Attributes inherited from gem5::VegaISA::Inst_SOPP | |

| InFmt_SOPP | instData |

| Protected Attributes inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| ScalarRegU32 | _srcLiteral |

| if the instruction has a src literal - an immediate value that is part of the instruction stream - we store that here | |

| Protected Attributes inherited from gem5::GPUStaticInst | |

| const std::string | _opcode |

| std::string | disassembly |

| int | _instNum |

| int | _instAddr |

| std::vector< OperandInfo > | srcOps |

| std::vector< OperandInfo > | dstOps |

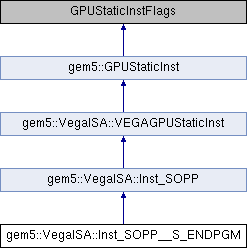

Detailed Description

Definition at line 4521 of file instructions.hh.

Constructor & Destructor Documentation

◆ Inst_SOPP__S_ENDPGM()

| gem5::VegaISA::Inst_SOPP__S_ENDPGM::Inst_SOPP__S_ENDPGM | ( | InFmt_SOPP * | iFmt | ) |

Definition at line 65 of file sopp.cc.

References gem5::VegaISA::Inst_SOPP::Inst_SOPP(), and gem5::GPUStaticInst::setFlag().

◆ ~Inst_SOPP__S_ENDPGM()

Member Function Documentation

◆ execute()

|

overridevirtual |

The parent WF of this instruction is exiting, therefore it should not participate in this barrier any longer. This prevents possible deadlock issues if WFs exit early.

If all WFs have finished, and hence the WG has finished, then we can free up the barrier belonging to the parent WG, but only if we actually used a barrier (i.e., more than one WF in the WG).

Last wavefront of the workgroup has executed return. If the workgroup is not the final one in the kernel, then simply retire it; however, if it is the final one, i.e., indicating the kernel end, then release operation (i.e., GL2 WB) is needed

if it is a kernel end, inject a memory sync, i.e., GL2 WB, and retire the workgroup after receving response. note that GL0V and GL1 are read only, and they just forward GL2 WB request. When forwarding, GL1 send the request to all GL2 in the complex

Implements gem5::GPUStaticInst.

Definition at line 81 of file sopp.cc.

References gem5::ComputeUnit::activeWaves, gem5::Wavefront::barrierId(), gem5::ComputeUnit::ComputeUnitStats::completedWfs, gem5::ComputeUnit::ComputeUnitStats::completedWGs, gem5::Wavefront::computeUnit, gem5::ComputeUnit::cu_id, gem5::ComputeUnit::decMaxBarrierCnt(), gem5::LdsState::decreaseRefCounter(), gem5::Shader::dispatcher(), gem5::Wavefront::dispatchId, DPRINTF, gem5::Wavefront::dropFetch, gem5::ComputeUnit::fetchStage, gem5::FetchStage::fetchUnit(), gem5::FetchUnit::flushBuf(), gem5::RegisterManager::freeRegisters(), gem5::ComputeUnit::getLds(), gem5::Wavefront::getStatus(), gem5::Wavefront::hasBarrier(), gem5::ArmISA::i, gem5::Shader::impl_kern_end_rel, gem5::Wavefront::instructionBuffer, gem5::WFBarrier::InvalidID, gem5::GPUDispatcher::isReachingKernelEnd(), gem5::Wavefront::lastInstExec, gem5::ComputeUnit::maxBarrierCnt(), gem5::GPUDispatcher::notifyWgCompl(), panic_if, gem5::Wavefront::pendingFetch, gem5::Shader::prepareFlush(), gem5::Wavefront::rawDist, gem5::Wavefront::WavefrontStats::readsPerWrite, gem5::ComputeUnit::registerManager, gem5::ComputeUnit::releaseBarrier(), gem5::Wavefront::releaseBarrier(), gem5::Wavefront::S_BARRIER, gem5::Wavefront::S_RETURNING, gem5::Wavefront::S_STOPPED, gem5::statistics::DistBase< Derived, Stor >::sample(), gem5::GPUDispatcher::scheduleDispatch(), gem5::GPUStaticInst::setFlag(), gem5::Wavefront::setStatus(), gem5::ComputeUnit::shader, gem5::Wavefront::simdId, gem5::ComputeUnit::stats, gem5::Wavefront::stats, gem5::Wavefront::vecReads, gem5::Wavefront::wfDynId, gem5::Wavefront::wfSlotId, and gem5::Wavefront::wgId.

◆ getNumOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 4528 of file instructions.hh.

References numDstRegOperands(), and numSrcRegOperands().

◆ getOperandSize()

|

inlineoverridevirtual |

◆ numDstRegOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 4533 of file instructions.hh.

Referenced by getNumOperands().

◆ numSrcRegOperands()

|

inlineoverridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 4534 of file instructions.hh.

Referenced by getNumOperands().

The documentation for this class was generated from the following files:

- arch/amdgpu/vega/insts/instructions.hh

- arch/amdgpu/vega/insts/sopp.cc

Generated on Sat Oct 18 2025 08:07:23 for gem5 by doxygen 1.14.0